## Modular Exponentiation on Reconfigurable Hardware

by Thomas Blum

A Thesis Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE In partial fulfillment of the requirements for the Degree of Master of Science in Electrical Engineering

April 8th, 1999

Approved:

Prof. Christof Paar ECE Department Thesis Advisor Prof. Yusuf Leblebici ECE Department Thesis Committee

Prof. Fred J. Looft ECE Department Thesis Committee Prof. John Orr ECE Department Head

## Abstract

It is widely recognized that security issues will play a crucial role in the majority of future computer and communication systems. A central tool for achieving system security are cryptographic algorithms. For performance as well as for physical security reasons, it is often advantageous to realize cryptographic algorithms in hardware. In order to overcome the well-known drawback of reduced flexibility that is associated with traditional ASIC solutions, this contribution proposes arithmetic architectures which are optimized for modern field programmable gate arrays (FPGAs). The proposed architectures perform modular exponentiation with very long integers. This operation is at the heart of many practical public-key algorithms such as RSA and discrete logarithm schemes. We combine two versions of Montgomery modular multiplication algorithm with new systolic array designs which are well suited for FPGA realizations. The first one is based on a radix of two and is capable of processing a variable number of bits per array cell leading to a low cost design. The second design uses a radix of sixteen, resulting in a speed–up of a factor three at the cost of more used resources. The designs are flexible, allowing any choice of operand and modulus.

Unlike previous approaches, we systematically implement and compare several versions of our new architecture for different bit lengths. We provide absolute area and timing measures for each architecture on Xilinx XC4000 series FPGAs. As a first practical result we show that it is possible to implement modular exponentiation at secure bit lengths on a single commercially available FPGA. Secondly we present faster processing times than previously reported. The Diffie-Hellman key exchange scheme with a modulus of 1024 bits and an exponent of 160 bits is computed in 1.9 ms. Our fastest design computes a 1024 bit RSA decryption in 3.1 ms when the Chinese remainder theorem is applied. These times are more than ten times faster than any reported software implementation. They also outperform most of the hardware-implementations presented in technical literature.

# Contents

| 1        | Intr           | oduction                                                            | 1  |

|----------|----------------|---------------------------------------------------------------------|----|

|          | 1.1            | Motivation                                                          | 1  |

|          | 1.2            | Thesis Goals                                                        | 2  |

|          | 1.3            | Thesis Outline                                                      | 3  |

| <b>2</b> | Pre            | vious Work                                                          | 4  |

|          | 2.1            | Montgomery Reduction and Redundant Representation                   | 4  |

|          | 2.2            | Montgomery Reduction and Systolic Arrays                            | 6  |

|          | 2.3            | Other Work                                                          | 6  |

|          | 2.4            | Implementations                                                     | 7  |

| 3        | Pre            | liminaries: Public–Key Algorithms                                   | 9  |

|          | 3.1            | RSA                                                                 | 9  |

|          | 3.2            | Algorithms Based on the Discrete Logarithm Problem in Finite Fields | 10 |

|          | 3.3            | Elliptic Curves                                                     | 12 |

| 4        | $\mathbf{Pre}$ | liminaries: Modular Exponentiation                                  | 14 |

|          | 4.1            | Square & Multiply Algorithm                                         | 14 |

|          | 4.2            | Montgomery Reduction                                                | 15 |

|          | 4.3            | Montgomery Multiplication for Radix Two                             | 18 |

|          | 4.4            | High–Radix Montgomery Algorithm                                     | 20 |

| <b>5</b> | Ger            | neral Design Considerations                                         | 23 |

|          | 5.1            | Xilinx XC4000 Series FPGAs                                          | 23 |

|          |                | 5.1.1 Configurable Logic Blocks                                     | 23 |

|          |                | 5.1.2 Routing Topologies                                            | 24 |

|          |                | 5.1.3 Special Features of the XC4000 Family                         | 26 |

|          |                | 5.1.4 Cost and Speed Evaluation                                     | 27 |

|          | 5.2            | Architectures Suitable for FPGAs                                    | 27 |

|          |                | 5.2.1 Systolic Array vs. Redundant Representation                   | 27 |

|          |                | 5.2.2 State Machine and Storage Elements                            | 31 |

| 6            | $\mathbf{Des}$ | sign 1: A Resource Efficient Architecture                         | <b>32</b> |

|--------------|----------------|-------------------------------------------------------------------|-----------|

|              | 6.1            | Design Overview                                                   | 32        |

|              | 6.2            | Processing Elements                                               | 34        |

|              | 6.3            | Modular Multiplication                                            | 37        |

|              | 6.4            | Modular Exponentiation                                            | 39        |

|              |                | 6.4.1 Data Flow                                                   | 39        |

|              |                | 6.4.2 Function Blocks                                             | 42        |

| 7            | Des            | sign 2: A Speed Efficient Architecture                            | 46        |

|              | 7.1            | Design Overview                                                   | 46        |

|              | 7.2            | Processing Elements                                               | 49        |

|              | 7.3            | Modular Multiplication                                            | 51        |

|              | 7.4            | Modular Exponentiation                                            | 54        |

|              |                | 7.4.1 Data Flow                                                   | 54        |

|              |                | 7.4.2 Function Blocks                                             | 57        |

| 8            | Me             | thodology                                                         | 59        |

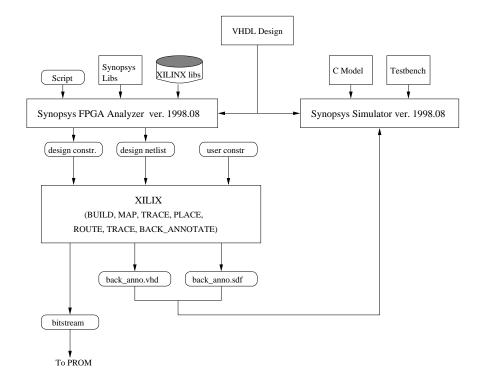

|              | 8.1            | Xilinx Synopsys Interface                                         | 60        |

|              | 8.2            | Simulation and Verification                                       | 60        |

|              | 8.3            | Synthesis                                                         | 61        |

|              | 8.4            | Place and Route                                                   | 62        |

| 9            | Res            | sults                                                             | 63        |

|              | 9.1            | Design 1                                                          | 63        |

|              | 9.2            | Design 2                                                          | 65        |

|              | 9.3            | Application to RSA                                                | 67        |

|              | 9.4            | Application to Algorithms Based on the Discrete Logarithm Problem | 68        |

|              | 9.5            | Application to Elliptic Curves                                    | 68        |

| 10           | Cor            | mparison and Outlook                                              | 72        |

| $\mathbf{A}$ | Tes            | t Bench Sample                                                    | 75        |

| в            | Syn            | nosys Script                                                      | 83        |

| C            | •              |                                                                   | 00        |

| С            |                | nulation Results                                                  | 89        |

|              |                | Processing Elements                                               | 89        |

|              | C.2            |                                                                   | 94        |

|              | C.3            | Modular Exponentiation                                            | 98        |

# List of Tables

| 5.1  | Routing per CLB in XC4000XL and XC4000XV devices [38]                                   | 26 |

|------|-----------------------------------------------------------------------------------------|----|

| 5.2  | Amount of CLBs used for RAM and DP RAM blocks on XC4000 devices $% \mathcal{A}^{(1)}$ . | 27 |

| 9.1  | Design 1: CLB usage, minimal clock cycle time, and time–area product of                 |    |

|      | modular exponentiation architectures on Xilinx FPGAs                                    | 63 |

| 9.2  | Design 1: CLB usage and execution time for a full modular exponentiation                | 65 |

| 9.3  | Design 2: CLB usage, minimal clock cycle time, and time-area product of                 |    |

|      | modular exponentiation architectures on Xilinx FPGAs                                    | 65 |

| 9.4  | Design2: CLB usage and execution time for a full modular exponentiation                 | 66 |

| 9.5  | Application to RSA: Encryption                                                          | 67 |

| 9.6  | Application to RSA: Decryption                                                          | 67 |

| 9.7  | CLB usage and execution time for algorithms based on the DL–problem                     | 68 |

| 9.8  | Operations for a point addition                                                         | 69 |

| 9.9  | Operations for a Doubling                                                               | 70 |

| 9.10 | Application to Elliptic Curves: Execution time for point addition and dou-              |    |

|      | bling (160 bits)                                                                        | 71 |

| 9.11 | Application to Elliptic Curves: Execution time for a general point multipli-            |    |

|      | cation (160 bits)                                                                       | 71 |

|      |                                                                                         |    |

# List of Figures

| 5.1 | XC4000 CLB Structure [38]                                                               | 4 |  |

|-----|-----------------------------------------------------------------------------------------|---|--|

| 5.2 | Xilinx FPGA structure [38] 2                                                            | 5 |  |

| 6.1 | Processing element (unit) of Design 1 that computes $S_{i+1} = (S_i + q_i \cdot M)/2 +$ |   |  |

|     | $a_i \cdot B, q_i, a_i \in \{0, 1\}$                                                    | 5 |  |

| 6.2 | Systolic Array for modular multiplication                                               | 7 |  |

| 6.3 | Design for a modular exponentiation                                                     | 0 |  |

| 6.4 | DP RAM Z Unit                                                                           | 2 |  |

| 6.5 | Exp RAM Unit                                                                            | 4 |  |

| 6.6 | Prec RAM Unit                                                                           | 5 |  |

| 7.1 | Processing Element (unit)                                                               | 9 |  |

| 7.2 | Systolic array for modular multiplication                                               | 2 |  |

| 7.3 | Design for a modular exponentiation                                                     | 4 |  |

| 7.4 | DP RAM Z Unit    5                                                                      | 7 |  |

| 8.1 | Design flow                                                                             | 1 |  |

| C.1 | Processing Element: Loading of the pre-computation factor and calculation               |   |  |

|     | of its multiples                                                                        | 1 |  |

| C.2 | Processing Element: Computation of two modular multiplications (first cycles) 9         | 2 |  |

| C.3 | Processing Element: Computation of two modular multiplications (last cycles). 9.        | 3 |  |

| C.4 | Systolic Array: Beginning of the pre-computation                                        | 5 |  |

| C.5 | Systolic Array: End of the pre-computation in units 0,1,2 9                             | 6 |  |

| C.6 | Systolic Array: End of the pre-computation in units 41,42,43 9                          | 7 |  |

| C.7 | Modular Exponentiation: Beginning of pre-computation                                    |   |  |

| C.8 | Modular Exponentiation: End of pre-computation and beginning of $Z_1$ , $P_1$           |   |  |

|     | calculation                                                                             | 1 |  |

| C.9 | Modular Exponentiation: Loading the exponent and computation of a mod-                  |   |  |

|     | ular exponentiation with a 19-bit exponent 10                                           | 2 |  |

## Chapter 1

## Introduction

#### 1.1 Motivation

It is widely recognized that security issues will play a crucial role in many future computer and communication systems. A central tool for achieving system security is cryptography. For performance as well as for physical security reasons it is often required to realize cryptographic algorithms in hardware. Traditional ASIC solutions, however, have the well-known drawback of reduced flexibility compared to software solutions. Since modern security protocols are increasingly defined to be *algorithm independent*, a high degree of flexibility with respect to the cryptographic algorithms is desirable. A promising solution which combines high flexibility with the speed and physical security of traditional hardware is the implementation of cryptographic algorithms on reconfigurable devices such as FPGAs and EPLDs. In the case of public-key schemes, algorithm independence can mean not only a change of the actual cryptographic algorithm but also a change of parameters such as bit length, modulus, or exponents. One application, dealt with in this report, includes arithmetic architectures for modular exponentiation with very long integers which is at the heart of most modern public-key schemes. Most notably, both RSA and discrete logarithm-based (e.g., Diffie-Hellman key exchange or the Digital Signature Algorithm, DSA) schemes require modular long number exponentiation.

The challenge at hand is to design arithmetic architectures for operands with up to 1024 bits on current FPGAs. The very long word lengths prohibit the application of many proposed architectures as they would result in unrealistically large resource requirements. In this thesis we derive two modular exponentiation architectures which combine Montgomery's modular reduction scheme and novel systolic array architectures. The systolic array architecture requires considerably fewer logic resources than many other systolic array architectures for modular arithmetic. This is crucial, as one of our goals was to derive solutions that can fit into a single FPGA, a design goal that has many cost and design advantages over multi–FPGA solutions. Another important objective was to systematically implement various architecture options for different bit lengths and compare performance and resource usage.

#### 1.2 Thesis Goals

Based on the general considerations in the previous section we defined the following goals for the thesis research:

- Implementation of a 1024-bit modular exponentiation architecture in a single commercially available FPGA device. 1024 bits is the recommended bit size for RSA and discrete logarithm systems and thus highly relevant for practical applications. The computation time of our architecture should be close to a previously reported architecture that used 16 FPGAs [33].

- 2. It should be investigated which of the two proposed general architecture options, based on systolic arrays and a redundant representation, is best suited for modular exponentiation architectures on FPGAs.

- 3. To find an optimal resource usage and computation time trade-off for the FPGA architectures that will be designed.

- 4. A resource efficient FPGA design should be developed which allows the implementation of a 1024 bit architecture at moderate costs.

- 5. It should be investigated weather the high–radix Montgomery modular multiplication algorithm proposed in [9] can be used for modular exponentiation architectures on FPGAs.

- 6. Develop and implement a design that is considerably faster than any previously reported FPGA architecture and reaches speeds similar to the fastest design reported in technical literature [27].

#### 1.3 Thesis Outline

This thesis is structured as follows. In Chapter 2, we summarize some of the previous work on modular exponentiation. Chapter 3 describes three families of algorithms in public–key cryptography, and the modular arithmetic needed for their implementation. Chapter 4 describes algorithms for modular exponentiation and multiplication and some simplifications and speed-ups for their hardware implementation. In Section 5 we summarize some of the relevant features of the Xilinx XC4000 FPGA series. Based on these features we derive some characteristics for our architectures. Chapter 6 outlines our architecture for modular exponentiation, optimized for low resource usage. Chapter 7 describes an architecture optimized for speed. Chapter 8 describes our methodology and tools that were used for this research. Chapter 9 posts the timing and area results obtained. A comparison to other architectures and an outlook conclude this thesis.

## Chapter 2

## **Previous Work**

In the following, we will summarize relevant previous work in the field of modular multiplication. Most presented approaches are based on an algorithm proposed by Peter Montgomery in 1985 [19], either in conjunction with a redundant number representation or in a systolic array architecture. Solutions using other algorithms have also been presented.

## 2.1 Montgomery Reduction and Redundant Representation

Applying Montgomery's algorithm, the cost of a modular exponentiation is reduced to a series of additions of very long integers. To avoid the carry propagation in multiplication/addition architectures several solutions have been proposed in the literature. They either use Montgomery's algorithm, in combination with a redundant radix number system [26, 33, 7, 9, 36] or a Residue Number System [2].

In [7] Montgomery's modular multiplication algorithm is adapted for an efficient hardware implementation. A gain in speed results from a faster clock, due to simpler combinatorial logic. Compared to previous techniques based on Brickell's Algorithm [4], a speed-up factor of two is reported.

The Research Laboratory of Digital Equipment Corp. in Paris implemented modular exponentiation architectures on FPGAs [33, 26]. They utilized an array of 16 XILINX 3090 FPGAs. Compared to XILINX 4000 series in terms of flip-flops, this is equivalent to a chip with 5100 configurable logic blocks (CLBs). In terms of logic resources this is equivalent to a chip of 4000 CLBs. In their work they used several speed-up methods [26] including the Chinese remainder theorem, asynchronous carry completion adder, and a windowing exponentiation method. The implementation computes a 970bit RSA decryption at a rate of 185kb/s (5.2ms per 970 bit decryption) and a 512 bit RSA decryption in excess of 300 kb/s (1.7ms per 512 bit decryption). A drawback of this solution is that the binary representation of the modulus is hardwired into the logic representation so that the architecture has to be reconfigured with every new modulus.

The problem of using high radices in Montgomery's modular multiplication algorithm is the more complex determination of the quotient. This behavior made a pipelined execution of the algorithm impossible. Reference [9] rewrites the algorithm and avoids thereby any operation involved in the quotient determination. The necessary pre-computation has to be done only once for a given modulus.

Reference [36] proposes a novel VLSI architecture for Montgomery's modular multiplication algorithm. The critical path that determines the clock speed is pipelined. This is done by interleaving each iteration of the algorithm. Compared to previous propositions, an improvement of the time–area product of a factor two is reported.

Reference [2] describes a new approach using a Residue Number System (RNS). The algorithm is implemented with n moduli in the RNS on n reasonably simple processors. The resulting processing time is O(n).

#### 2.2 Montgomery Reduction and Systolic Arrays

There have been a number of proposals for systolic array architectures for modular arithmetic. However, no implementations have been reported to our knowledge. In [8] a VLSI solution is presented where a modular multiplication is calculated in  $(4m + 1) \cdot 3m/2$  clock cycles, where m is the number of bits of the modulus. That is approximately four times more cycles than in a conventional solution. In terms of resources, this design would be suitable for FPGA.

Similar two-dimensional systolic arrays are presented in [10, 35, 36]. For a radix of two they all propose an  $m \times m$  matrix of one bit processing elements. With this configuration 2m modular multiplications are calculated at the same time and the theoretical throughput is one modular multiplication per clock cycle. In terms of resources, such a solution is not feasible in either VLSI or FPGA for the bit length required in public-key algorithms. Even implementing only one row of processing elements, (resulting in m times slower throughput) into presently available FPGAs is difficult in terms of resources.

In reference [30] a linear systolic array was obtained by systematically mapping a two-dimensional graph model onto a one-dimensional systolic array.

Reference [15] describes an architecture based on one row of processing elements and a radix of two. Squarings and multiplications are computed in parallel. The system requires n systolic processing elements for an n-bit modular exponentiation, and the resulting execution time is  $2n^2$  clock cycles.

#### 2.3 Other Work

References [4, 25, 32, 31] describe different algorithms for modular multiplication avoiding costly division. Reference [3] compares these algorithms. An overview of previously presented architectures for VLSI implementations and their underlying algorithms for modular integer arithmetic is also provided in this contribution. Reference [5] summarizes the chips available in 1990 for performing RSA encryption.

In Reference [34] a generalization of [4] is presented and some conclusions are drawn about the choice of the radix.

Reference [29] proposes a radix–4 hardware algorithm. A redundant number representation is used and the propagation of carries in additions is therefore avoided. A processing speed–up of about six times compared to previous work is reported.

More recently an approach [39] has been presented that utilizes pre-computed complements of the modulus and is based on the iterative Horner's rule. Compared to Montgomery's algorithms these approaches use the most significant bits of an intermediate result to decide which multiples of the modulus to subtract. The drawback of these solutions is that they either need a large amount of storage space or many clock cycles to complete a modular multiplication. The authors attempted to overcome the later problem by a higher clock frequency which is possible due to a simplified modulo reduction operation.

#### 2.4 Implementations

To our knowledge, the fastest reported software implementation of modular exponentiation [37] computes RSA decryption with a 1024–bit modulus in 43 ms.

In Reference [23] a table with several VLSI hardware implementations for RSA is published. The fastest chip computes RSA decryption with a 512–bit modulus in 8 ms. These chips are somewhat dated, though. More recently an ASIC implementation has been reported [16] that computes RSA decryption with a 1024–bit modulus in 150 ms. However, the author claims in [27] that 1024–bit exponentiation architectures with 10 ms computation time are available. This time corresponds to an RSA computation time of 2.5 ms if the Chinese remainder theorem is used for speeding– up the computation. Only one FPGA implementation of RSA has been reported in technical literature so far [33]. 970-bit RSA decryption is computed in 5.2 ms in this approach. A detailed comparison of the modular exponentiation architectures that we develop in this thesis with the previously reported implementations will be given in Chapter 9.

## Chapter 3

# Preliminaries: Public–Key Algorithms

In this chapter we review the three most popular families of public key algorithms. Information on secure key length is given as well as speed-up methods proposed in the literature. We will show that all algorithm families are based on modular long number arithmetic.

### 3.1 RSA

RSA was proposed by Rivest, Shamir and Adleman [21] in 1978. The private key of a user consists of two large primes p and q and an exponent D. The public key consists of the modulus  $M = p \times q$ ,  $M = \sum_{i=0}^{m-1} m_i 2^i$ ,  $m_i \in \{0, 1\}$  and an exponent E such that  $E = D^{-1} \mod (p-1)(q-1)$ ,  $E = \sum_{i=0}^{n-1} e_i 2^i$ ,  $e_i \in \{0, 1\}$ . In the remainder of this thesis we assume that E can be represented by n bits, and M can be represented by m digits. To encrypt a message X the user computes:

$$Y = X^E \bmod M$$

Decryption is done by calculating:

$$X = Y^D \bmod M$$

The identical operations are used for the RSA digital signature scheme. In order to thwart currently known attacks, the modulus M and thus X and Y should have a length of 768 – 1024 bits. Both encryption and decryption require algorithms for computing a modular exponentiation.

For speeding up encryption the use of a short exponent E has been proposed [13]. Recommended by the International Telecommunications Union ITU is the the Fermat prime  $F_4 = 2^{16} + 1$ . Using  $F_4$ , the encryption is executed in only 17 operations. Other short exponents proposed include E = 3 and E = 17.

Obviously the same trick can not be used for decryption, as the decryption exponent D must be kept secret. But using the knowledge of the factors of  $M = q \times p$ , the Chinese Remainder Theorem [20] can be applied by the decrypting party. Two m/2 size modular exponentiations and an additional recombination instead of one m size modular exponentiation are computed in this case. Each modular exponentiation of length m/2 takes 1/4 of the time required for an m – bit exponentiation (see Chapter 4). If both exponentiations are performed serially, an over-all speed-up factor of two is achieved. If they are performed in parallel, a speed-up factor of four is achieved.

## 3.2 Algorithms Based on the Discrete Logarithm Problem in Finite Fields

The best known public-key schemes based on the discrete logarithm problem in finite fields are the Diffie-Hellman key exchange scheme, the Digital Signature Algorithm (DSA) and the ElGamal encryption scheme (see, e.g., [17]). As an example, we present below the Diffie-Hellman key exchange scheme, proposed in 1976 by W. Diffie and M.E. Hellman [6].

The goal of this protocol is to establish a secret session key between to parties over an insecure channel. The two parties, Alice and Bob, want to establish a secret key without Oscar, the adversary, being able to compute this key. During the setup phase Alice and Bob obtain the public parameters p and  $\alpha$ . Parameter p is a large prime and  $\alpha$  a primitive element in  $Z_p^*$  or a subgroup of  $Z_p^*$ .

The algorithm proceeds as follows:

1a) Alice generates a random key: 1b) Bob generates a random key:  $a_A \in \{2, 3, \dots, p-1\}$  (private)  $a_B \in \{2, 3, \dots p - 1\}$  (private) 2a) Alice computes her public key:

$\beta_A$

- $\beta_A = \alpha^{a_A} \mod p \text{ (public)}$

- 3a) Alice sends  $\beta_A$  to Bob

- 4a) Alice computes:

$$K_s = \beta_B^{a_A} = (\alpha^{a_B})^{a_A} = \alpha^{a_B \cdot a_A} \mod p$$

2b) Bob computes his public key:  $\beta_B = \alpha^{a_B} \mod p \text{ (public)}$

$$\stackrel{\beta_B}{\leftarrow}$$

3b) Bob send  $\beta_B$  to Alice

4b) Bob computes:

$$K_s = (\alpha^{a_A})^{a_B} = \alpha^{a_A \cdot a_B} \mod p$$

After the final stage of the algorithm, Alice and Bob share a session key  $K_s$ . Oscar cannot regenerate the session key from the public parameters  $\alpha$ ,  $\beta_A$ , and  $\beta_B$  because the two random integers  $a_A$  and  $a_B$ , generated by Alice and Bob are private and were never transmitted over the insecure channel.

The computational complexity of the algorithm lies in steps 2 and 4, the computation of a modular exponentiation. The index-calculus method is the currently best known attack against discrete logarithm-based schemes. In order to thwart this attack, the modulus p and thus  $\alpha$  should have a length of 768–1024 bits, and even longer bit lengths are recommended for highly sensitive applications. If  $\alpha$  generates a subgroup of order n, the exponents  $a_A$ ,  $a_B$  can be restricted to  $0 < a_A, a_B < n$ . In practice, a 160 bit exponent can be used with moduli up to 1024 bit.

#### 3.3 Elliptic Curves

Elliptic Curve public-key cryptosystems were proposed independently in 1986/1987 by Victor Miller [18] and Neil Koblitz [14]. We restrict ourselves in the following to curves over prime fields, as opposed to curves over extension fields such as  $GF(2^m)$ . An elliptic curve is a set of all pairs  $(x,y), x, y \in Z_p$ , that fulfill the equation:

$$y^2 \equiv x^3 + ax + b \bmod p$$

To perform an addition of two points  $P_1 = (x_1, y_1)$ ,  $P_2 = (x_2, y_2)$ ,  $P_3 = P_1 + P_2 = (x_3, y_3)$  we need to compute the following equations:

$$x_3 = \lambda^2 - x_1 - x_2$$

$$y_3 = \lambda \cdot (x_1 - x_3) - y_1$$

$$\lambda = \begin{cases} \frac{y_2 - y_1}{x_2 - x_1} \mod p, & \text{if } P_1 \neq P_2 \text{ (addition)} \\ \frac{3x_1^2 + a}{2y_1} \mod p, & \text{if } P_1 = P_2 \text{ (doubling)} \end{cases}$$

The complexity of this operation is two multiplications and one inversion (pointaddition) or three multiplications and one inversion (point-doubling), if we ignore additions and subtractions. The inversion is very costly to implement. To optimize the addition of two points by avoiding the inversion, the use of projective coordinates has been proposed. A projective point (X,Y,Z) in the projective plane can be identified with a point (x,y) in the affine plane. The homogeneous elliptic curve is a set of all points (X,Y,Z) that fulfill the equation:

$$ZY^2 \equiv X^3 + aXZ^2 + bZ^3 \bmod p$$

The addition formulae are now [12]:

addition:

$$\begin{split} X_3 &= VA\\ Y_3 &= U(V^2X_1Z_2 - A) - V^3Y_1Z_2\\ Z_3 &= V^3Z_1Z_2 \end{split}$$

where  $U = Y_2Z_1 - Y_1Z_2$ ,  $V = X_2Z_1 - X_1Z_2$ ,  $A = U^2Z_1Z_2 - V^2T$ ,  $T = X_2Z_1 + X_1Z_2$ doubling:  $X_3 = 2SH$  $Y_3 = W(4F - H) - 8E^2$  $Z_3 = 8S^3$ where  $S = Y_1Z_1$ ,  $W = 3X_1^2 + aZ_1^2$ ,  $E = Y_1S$ ,  $F = X_1E$ ,  $H = W^2 - 8F$

To perform an elliptic curve projective space addition we have to compute 15 multiplications, and 12 multiplications are needed for a doubling operation.

A method similar to Algorithm 4.1 combines additons and doublings to a general point multiplication,  $e \cdot P$ , that is, addition of the point P e-times to itself. Point multiplication is the core operation in elliptic curve public key crypto-systems. If we use a modulus and operands of length m+1 bits, m doublings and an average of m/2additions have to be executed.

The currently best known attack against elliptic curve public key crypto-systems uses the Silver-Pohlig-Hellmann algorithm [24] together with Pollard's rho method. In order to thwart this attack, the modulus p and thus X, Y, and Z should have a length of at least 160 bits. We note that this operand bit length is considerably shorter than in the case of RSA or DL schemes.

## Chapter 4

# Preliminaries: Modular Exponentiation

In this chapter we review the square & multiply algorithm, which is the most popular algorithm for modular exponentiation. Secondly we develop versions of Montgomery's modular multiplication algorithm, which are well suited for hardware implementations.

### 4.1 Square & Multiply Algorithm

The public-key schemes described in Chapter 3 are based on modular exponentiation or repeated point addition. Both operations are in their most basic forms done by the square and multiply algorithm [13].

**Algorithm 4.1** compute  $Z = X^E \mod M$ , where  $E = \sum_{i=0}^{n-1} e_i 2^i$ ,  $e_i \in \{0, 1\}$

- 1. Z = X

- 2. FOR i = n 2 down to 0 DO

- 3.  $Z = Z^2 \mod M$

- 4. IF  $e_i = 1$  THEN  $Z = Z \cdot X \mod M$

#### 5. END FOR

Algorithm 4.1 takes 2(n-1) operations in the worst case and 1.5(n-1) on average. To compute a squaring and a multiplication in parallel we can use the following version of the square & multiply algorithm [36]:

Algorithm 4.2 computes  $P = X^E \mod M$ , where  $E = \sum_{i=0}^{n-1} e_i 2^i$ ,  $e_i \in \{0, 1\}$

- 1.  $P_0 = 1, Z_0 = X$

- 2. FOR i = 0 to n 1 DO

- 3.  $Z_{i+1} = Z_i^2 \mod M$

- 4. IF  $e_i = 1$  THEN  $P_{i+1} = P_i \cdot Z_i \mod M$ ELSE  $P_{i+1} = P_i$

- 5. END FOR

Algorithm 4.2 takes 2n operations in the worst case and 1.5n on average. A speedup can be achieved by applying the l – ary method [13] which is a generalization of Algorithm 4.1. The l – ary method processes l exponent bits at the time. The drawback here is that  $(2^{l} - 2)$  multiples of X have to be precomputed and stored. A reduction to  $2^{l-1}$  pre-computations is possible. The resulting complexity is roughly n/l multiplications and n squaring operations.

#### 4.2 Montgomery Reduction

As shown in the previous section, modular exponentiation is reduced to a series of modular multiplications and squaring steps. The algorithm for modular multiplication described below has been proposed by P. L. Montgomery in 1985 [19]. It is a method for multiplying two integers modulo M, while avoiding division by M. The idea is to transform the integers in m-residues and compute the multiplication with these m-residues. Finally we transform back to the normal representation. This approach is only beneficial if we compute a series of multiplications in the transform domain (e.g., modular exponentiation). To compute the Montgomery multiplication, we chose a radix R > M, with gcd(M, R) = 1. Division by R has to be inexpensive, thus an optimal choice is  $R = 2^m$  if we assume that  $M = \sum_{i=0}^{m-1} m_i 2^i$ . The *m*-residue of x is  $xR \mod M$ . We also compute  $M' = -M^{-1} \mod R$ . Now we define a function MRED(T) that computes  $TR^{-1} \mod M$ : This function computes the normal representation of T, given T is an *m*-residue.

**Algorithm 4.3** MRED(T): computes a Montgomery reduction of T $T < RM, R = 2^m, M = \sum_{i=0}^{m-1} m_i 2^i, \operatorname{gcd}(M, R) = 1$

1.  $U = TM' \mod R$ 2. t = (T + UM)/R3. IF  $t \ge M$  RETURN t - MELSE RETURN t

The result of MRED(T) is  $t = TR^{-1} \mod M$ . For the proof of this equation, see [19].

Now we consider a multiplication of two integers a and b in the transform domain, where their respective representations are  $(aR \mod M)$  and  $(bR \mod M)$ . To acquire the result  $(abR \mod M)$  we feed their product into MRED(T):

$$MRED((aR \mod M) \cdot (bR \mod M)) = abR^2R^{-1} = abR \mod M$$

For a modular exponentiation we can repeat this step numerous times according to Algorithm 4.1 or 4.2 to get the final result  $ZR \mod M$  (Algorithm 4.1) or  $P_nR \mod M$ (Algorithm 4.2). We finally feed one of these values into MRED(T) to get the result  $Z \mod M$  or  $P_n \mod M$ .

The initial transform step still requires costly modular reductions. To avoid the division involved, we can take the following approach. First we compute  $R^2 \mod M$  using division. This step needs to be done only once for a given cryptosystem. To get a and b in the transform domain we run MRED $(a \cdot R^2 \mod M)$  and MRED $(b \cdot R^2 \mod M)$

M) to get  $aR \mod M$  and  $bR \mod M$ . Obviously, any variable can be transformed in this manner.

We now consider a hardware implementation of Algorithm 4.3: To compute step 2 we need an  $m \times m$ -bit multiplication and a 2m-bit addition. The intermediate result can have as many as 2m bits. Instead of computing U at once, we can compute one digit of an r-radix representation at a time. We have to chose a radix r, such that gcd(M,r) = 1 [28]. Division by r has to be inexpensive, thus an optimal choice is  $r = 2^k$ . All variables are now represented in a basis-r representation. Another improvement is to include the multiplication  $A \times B$  in the algorithm.

Algorithm 4.4 [7] Montgomery Modular Multiplication for computing  $A \cdot B \mod M$ , where  $M = \sum_{i=0}^{m-1} (2^k)^i m_i$ ,  $m_i \in \{0, 1 \dots 2^k - 1\}$ ;  $B = \sum_{i=0}^{m-1} (2^k)^i b_i$ ,  $b_i \in \{0, 1 \dots 2^k - 1\}$ ;  $A = \sum_{i=0}^{m-1} (2^k)^i a_i$ ,  $a_i \in \{0, 1 \dots 2^k - 1\}$ ; A, B < M;  $M < R = 2^{km}$ ;  $M' = -M^{-1} \mod 2^k$ ;  $\gcd(2^k, M) = 1$

- 1.  $S_0 = 0$ 2.  $FOR \ i = 0 \ to \ m - 1 \ DO$ 3.  $q_i = (((S_i + a_i B) \ mod \ 2^k)M') \ mod \ 2^k$ 4.  $S_{i+1} = (S_i + q_i M + a_i B)/2^k$ 5.  $END \ FOR$ 6.  $IF \qquad S_m \ge M \ RETURN \ S_m - M$

- $ELSE \qquad RETURN S_m$

The output of Algorithm 4.4 is  $S_m = ABR^{-1} \mod M$ . Considering a radix  $r = 2^k$ , we need at most two  $k \times k$ - bit multiplications and a k-bit addition to compute step 3. For step 4 two  $k \times m$ - bit multiplications and two m + k-bit additions are needed. The maximal bit length of S is reduced to m + k + 2 bits, compared to the 2m bits of Algorithm 4.3. In Section 4.3 we review further improvements of Algorithm 4.4 for the case of r = 2. Section 4.4 treats the algorithm for larger radix.

#### 4.3 Montgomery Multiplication for Radix Two

Algorithm 4.5 is a simplification of Algorithm 4.4 for radix r = 2. For the radix r = 2, the operations in step 3 of Algorithm 4.4 are done modulo 2. The modulus M must be odd due to the condition  $gcd(M, 2^k) = 1$ . It follows immediately that  $M \equiv 1 \mod 2$ . Hence  $M' \equiv -M^{-1} \mod 2$  also degenerates to M' = 1. Thus the multiplication by  $M' \mod 2$  in step 3 can be omitted.

**Algorithm 4.5** [7] Montgomery Modular Multiplication (Radix r = 2) for computing  $A \cdot B \mod M$ , where  $M = \sum_{i=0}^{m-1} 2^i m_i$ ,  $m_i \in \{0, 1\}$ ;  $B = \sum_{i=0}^{m-1} 2^i b_i, \ b_i \in \{0, 1\};$  $A = \sum_{i=0}^{m-1} 2^{i} a_{i}, \ a_{i} \in \{0, 1\};$  $A, B < M; M < R = 2^m; \operatorname{gcd}(2, M) = 1$ 1.  $S_0 = 0$ FOR i = 0 to m - 1 DO 2. $q_i = (S_i + a_i B) \bmod 2$ 3.  $S_{i+1} = (S_i + q_iM + a_iB)/2$ 4. END FOR 5. IF $S_m \ge M RETURN S_m - M$ 6.

ELSE  $RETURN S_m$

The final comparison and subtraction in step 6 of Algorithm 4.5 would be costly to implement, as an m bit comparison is very slow or expensive in terms of resource usage. It would also make a pipelined execution of the algorithm impossible. It can easily be verified that  $S_{i+1} < 2M$  always holds if A, B < M.  $S_m$ , however, can not be reused as input A or B for the next modular multiplication. If we perform two more executions of the for loop with  $a_{m+1} = 0$  and inputs A, B < 2M, the inequality  $S_{m+2} < 2M$  is satisfied. Now,  $S_{m+2}$  can be used as input B for the next modular multiplication. We just allow S to have two more bits for intermediate results.

To further reduce the complexity of Algorithm 4.5, B can be shifted up by one position, i.e., multiplied by two [7]. This results in  $a_i \cdot B \mod 2 = 0$  and the addition in step 3 is avoided. In the update of  $S_{i+1}$  we replace  $(S_i + q_iM + a_iB)/2$  by  $(S_i + q_iM)/2 + a_iB$ . The cost of this simplification is one more execution of the loop with  $a_{m+2} = 0$ . The algorithm below comprises the just mentioned optimizations.

- Algorithm 4.6 [7] MONT\_R2(A,B): Montgomery Modular Multiplication (Radix r = 2) for computing  $A \cdot B \mod M$ , where  $M = \sum_{i=0}^{m-1} 2^i m_i$ ,  $m_i \in \{0, 1\}$ ;  $B = \sum_{i=0}^{m} 2^i b_i$ ,  $b_i \in \{0, 1\}$ ;  $A = \sum_{i=0}^{m+2} 2^i a_i$ ,  $a_i \in \{0, 1\}$ ,  $a_{m+1} = 0$ ,  $a_{m+2} = 0$ ; A, B < 2M,  $M < R = 2^{m+2}$ ; gcd(2, M) = 1

- 1.  $S_0 = 0$

- 2. FOR i = 0 to m + 2 DO

- 3.  $q_i = S_i \mod 2$

- 4.  $S_{i+1} = (S_i + q_i \cdot M)/2 + a_i \cdot B$

- 5. END FOR

The algorithm above calculates  $S_{m+3} = (2^{-(m+2)}AB) \mod M$ . To get the correct result we need an extra Montgomery modular multiplication by  $2^{2(m+2)} \mod M$ . However, if further multiplications are required as in exponentiation algorithms, it is better to pre-multiply all inputs by the factor  $2^{2(m+2)} \mod M$ . Thus every intermediate result carries a factor  $2^{m+2}$ . We just need to Montgomery multiply the result by "1" to eliminate that factor.

The final Montgomery multiplication with "1" insures that our final result is smaller than M. Consider Algorithm 4.6 with B < 2M and A = (0, ..., 0, 1). We will get  $S_1 = a_0 \cdot B = B < 2M$ . As all remaining  $a_i = 0$ , we get at most  $S_{i+1} = (S_i + M)/2 \rightarrow M$ . If only one  $q_i = 0$  (i = 1, 2...m + 2), then  $S_{i+1} = S_i/2 < M$ (probability:  $1 - 2^{-(m+2)}$ ).

The computational complexity of Algorithm 4.6 lies in the two additions of m bit operands for computing  $S_{i+1}$ . Recall that  $m \approx 160 - 1024$  is of great interest in public–key algorithms. As the propagation of m carries is too slow and an equivalent

carry look ahead logic requires to many resources, two different strategies have been pursued in literature:

- 1. Redundant representation: The intermediate results are kept in redundant form. Resolution into binary representation is only done at the very end and for feeding the intermediate result back as  $a_i$  in Algorithm 4.6.

- 2. Systolic Arrays: Typically m processing units calculate 1 bit per clock cycle. The computed carries,  $q_i$  and  $a_i$  are "pumped" through the processing units. As these signals have to be distributed only between adjacent processing units, a faster clock speed and a resulting higher throughput should be possible. The cost is a higher latency and possibly more resources.

#### 4.4 High–Radix Montgomery Algorithm

The goal of this section is to improve Algorithm 4.4 to make it suitable for a hardware implementation. At first we avoid the costly comparison and subtraction of step 6. The output  $S_m$  has to be small enough to be fed back in the algorithm as A or B. We change the conditions to  $4M < 2^{km}$  and A, B < 2M. This results in  $S_m < 2M$ as needed for further processing. The penalty is two more executions of the loop (see also Section 4.3 for k = 1).

In Section 4.3 the multiplication in the quotient  $q_i$  determination of Algorithm 4.4 was avoided. This is also possible for higher radixes [9]. M has to be transformed to  $\tilde{M} = (M' \mod 2^k)M$ . This step must be performed only once for a given crypto– system. The conditions for the algorithm are  $4\tilde{M} < 2^{km}$  and  $A, B < 2\tilde{M}$  now. Thus for the same bit length of M the loop has to be executed one more time. An other penalty is a larger range of  $S_m$ . Algorithm 4.7 comprises the above mentioned improvements. Algorithm 4.7 [9] Montgomery Modular Multiplication for computing  $A \cdot B \mod M$ , where  $M = \sum_{i=0}^{m-3} (2^k)^i m_i$ ,  $m_i \in \{0, 1 \dots 2^k - 1\}$ ;  $\tilde{M} = (M' \mod 2^k)M$ ,  $\tilde{M} = \sum_{i=0}^{m-2} (2^k)^i \tilde{m}_i$ ,  $\tilde{m}_i \in \{0, 1 \dots 2^k - 1\}$ ;  $B = \sum_{i=0}^{m-1} (2^k)^i b_i$ ,  $b_i \in \{0, 1 \dots 2^k - 1\}$ ;  $A = \sum_{i=0}^{m-1} (2^k)^i a_i$ ,  $a_i \in \{0, 1 \dots 2^k - 1\}$ ;  $A, B < 2\tilde{M}$ ;  $4\tilde{M} < 2^{km}$ ;  $M' = -M^{-1} \mod 2^k$

- 1.  $S_0 = 0$

- 2. FOR i = 0 to m 1 DO

- 3.  $q_i = (S_i + a_i B) \mod 2^k$

- 4.  $S_{i+1} = (S_i + q_i \tilde{M} + a_i B)/2^k$

- 5. END FOR

The quotient  $q_i$  determination complexity can further be reduced by replacing *B* by  $B \cdot 2^k$ . Since  $a_i B \mod 2^k \equiv 0$ , step 3 is reduced to  $q_i = S_i \mod 2^k$ . The addition in step 3 is avoided at the cost of an additional iteration of the loop, to compensate for the extra factor  $2^k$  in *B*. A Montgomery algorithm optimized for hardware implementation is shown below:

Algorithm 4.8 [9] MONT\_RH(A,B):Montgomery Modular Multiplication for computing  $A \cdot B \mod M$ , where  $M = \sum_{i=0}^{m-3} (2^k)^i m_i$ ,  $m_i \in \{0, 1 \dots 2^k - 1\}$ ;  $\tilde{M} = (M' \mod 2^k)M$ ,  $\tilde{M} = \sum_{i=0}^{m-2} (2^k)^i \tilde{m_i}$ ,  $\tilde{m_i} \in \{0, 1 \dots 2^k - 1\}$ ;  $B = \sum_{i=0}^{m-1} (2^k)^i b_i$ ,  $b_i \in \{0, 1 \dots 2^k - 1\}$ ;  $A = \sum_{i=0}^m (2^k)^i a_i$ ,  $a_i \in \{0, 1 \dots 2^k - 1\}$ ,  $a_m = 0$ ;  $A, B < 2\tilde{M}$ ;  $4\tilde{M} < 2^{km}$ ;  $M' = -M^{-1} \mod 2^k$

- 1.  $S_0 = 0$

- 2. FOR i = 0 to m DO

- 3.  $q_i = (S_i) \mod 2^k$

- 4.  $S_{i+1} = (S_i + q_i \tilde{M})/2^k + a_i B$

- 5. END FOR

The result of Algorithm 4.8 is  $S_{m+1} = ABR^{-1} \mod M$  where  $R = 2^{km} \mod M$ . We perform the same pre-computations as mentioned in Section 4.3: Pre-multiply all inputs by the factor  $2^{2km} \mod M$ . Thus every intermediate result carries a factor  $2^{km}$ . We just need to Montgomery multiply the final result by 1 to eliminate that factor.

The final Montgomery multiplication with 1 makes sure our final result is smaller than  $\tilde{M}$ . Consider Algorithm 4.8 with  $B < 2\tilde{M}$  and  $A = (0, \ldots, 0, 1)$ . We will obtain  $S_1 = a_0 \cdot B = B < 2\tilde{M}$ . As all remaining  $a_i = 0$ , we get at most  $S_{i+1} = (S_i + (2^k - 1)\tilde{M})/2^k \to \tilde{M}$ . If only one  $q_i \neq 2^k - 1$ ,  $(i = 1, 2 \dots m)$ ,  $q_i \in \{0, 1 \dots 2^k - 1\}$ , then  $S_{i+1} < \tilde{M}$ .  $\tilde{M}$ , however, can be  $2^k - 1$  times larger than M and the same is true for the result of a modular exponentiation  $S_{m+1}$ . The last quotient  $q_m$  and the factor  $M' \mod 2^k$  might determine the number of times M has to be subtracted from  $S_{m+1}$ . This behavior, however, has not been studied in this thesis. We assume that the final comparison and eventual modular reduction step is performed outside of our design.

Algorithm 4.8 is used for the architecture described in Chapter 7. The designs we implemented have moduli of 160, 256, 512, 768, and 1024 bits. The radix chosen was  $r = 2^4 = 16$ . For the rest of this thesis we use the following convention for specifying the complexity:  $M = \sum_{i=0}^{m-1} (2^k)^i m_i \Rightarrow \tilde{M} = \sum_{i=0}^m (2^k)^i \tilde{m}_i$ ,  $B = \sum_{i=0}^{m+1} (2^k)^i b_i$ ,  $A = \sum_{i=0}^{m+2} (2^k)^i a_i$ ,  $a_{m+2} = 0$ . The loop in Algorithm 4.8 is executed m + 3 times and the response is  $S_{m+3} = ABR^{-1} \mod M$ , where  $R = 2^{k(m+2)} \mod M$ . Thus the precomputation factor is  $2^{2k(m+2)} \mod M$ .

The computational complexity of Algorithm 4.8 lies in the two additions of m + kbit operands for computing  $S_{i+1}$ . Another costly operation is the computation of the multiples of M and B in step 4.

## Chapter 5

## **General Design Considerations**

In this chapter we present some of the relevant features of the Xilinx XC4000 Series FPGAs and introduce a metric for FPGA cost and performance evaluation. Based on these features we derive some characteristics for our architectures. The pros and cons of two different approaches to implement Montgomery's algorithm are exhibited.

### 5.1 Xilinx XC4000 Series FPGAs

#### 5.1.1 Configurable Logic Blocks

An FPGA device consists of three types of reconfigurable elements, the Configurable Logic Blocks (CLBs), I/O blocks (IOBs) and routing resources [38].

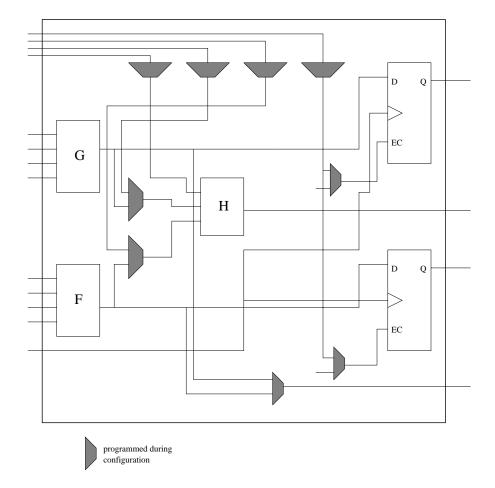

Figure 5.1.1 shows the structure of a CLB. An XC4000 CLB is made up of three look-up tables (LUT) F, G, and H, two flip-flops and programmable multiplexers. Any boolean function of 5 inputs, any two functions of 4 inputs and some functions of up to 9 inputs can be computed in one CLB. The multiplexers can route the outputs of the look-up tables directly to the outputs or to the flip-flops. In the first case the flip-flops can be utilized to store direct inputs. This is important for a design with a large amount of registers. The same CLB can be used to store two bits and compute two independent logic functions. Thus a considerable amount of resources can be

Figure 5.1: XC4000 CLB Structure [38]

saved as will be shown in Sections 6.2 and 7.2.

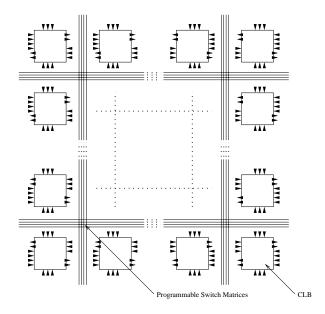

#### 5.1.2 Routing Topologies

Programmable routing resources connect the CLBs and IOBs into a network. The structure of XC4000 FPGA devices is shown in Figure 5.2. A matrix of switch boxes is placed over the CLB array. These switch boxes make it possible to connect any two CLBs together.

Routing in the XILINX FPGA is accomplished through a hierarchal structure.

Figure 5.2: Xilinx FPGA structure [38]

Each row or column of routing lines between CLBs has a number of different types of lines. These include single, double, quad, long, and global lines. Single lines route signals between adjacent CLBs. Double lines stretch over two CLBs. For the architectures described in Chapters 6 and 7, devices of the XC4000XL and XC4000XV families were used. Table 5.1 shows their routing resources per CLB:

The numbers show that a large amount of connections are available for closely located CLBs. On the other hand routing gets increasingly difficult for CLBs further apart. In Section 5.2.1 we will discuss some consequences this issue causes for the choice of our architectures. For a detailed description of the routing structure inside the XILINX FPGA, refer to [38].

|                 | Vertical | Horizontal |

|-----------------|----------|------------|

| Singles         | 8        | 8          |

| Doubles         | 4        | 4          |

| Quads           | 12       | 12         |

| Longlines       | 10       | 6          |

| Direct Connects | 2        | 2          |

| Globals         | 8        | 0          |

| Carry Logic     | 1        | 0          |

Table 5.1: Routing per CLB in XC4000XL and XC4000XV devices [38]

#### 5.1.3 Special Features of the XC4000 Family

The XC4000 devices contain dedicated, hard-wired carry logic to both accelerate and condense arithmetic functions such as adders and counters [38]. An n bit ripple carry adder is implemented in n/2 + 2 CLBs. The ripple carry outputs are routed between CLBs on high speed dedicated paths. The maximum delay from the operand input to the sum output of a N-bit adder is approximately:

$$t_{pd} = 4.5 + N \cdot 0.35 \ [ns]$$

For an n-bit counter, the minimum clock period is approximately:

$$t_{clk-clk} = 9.5 + N \cdot 0.35 \ [ns]$$

These values vary slightly for different devices and speed grades.

Another very useful feature of the XC4000 devices is the possibility to implement RAM in CLBs. A single CLB can be programmed as a  $16 \times 2$  bit or  $32 \times 1$  bit ROM/RAM or as a  $16 \times 1$  bit Dual Port RAM. RAM with larger address width requires considerably more resources. Table 5.2 shows the amount of CLBs used for implementing  $64 \times 2$ -bit,  $128 \times 2$ -bit, and  $256 \times 2$ -bit RAM and DP RAM blocks.

|        | $64 \times 2$ -bits | $128 \times 2\text{-bits}$ | $256 \times 2\text{-bits}$ |

|--------|---------------------|----------------------------|----------------------------|

|        | CLBs                | CLBs                       | CLBs                       |

| RAM    | 6                   | 12                         | 24                         |

| DP RAM | 16                  | 32                         | 64                         |

Table 5.2: Amount of CLBs used for RAM and DP RAM blocks on XC4000 devices

#### 5.1.4 Cost and Speed Evaluation

In previous work [36, 35, 7] related to modular arithmetic architectures, the gate count model has been used for cost evaluation and the gate delay model for speed evaluation. This is not appropriate for FPGAs. As the functional unit of an FPGA is the CLB, we evaluate the cost (C) in number of CLBs. The operation time (T) consists of logic delay in the CLBs and routing delay and is obtained from Xilinx's Timing Analyzer software. As a third parameter we use the time–area product (TA). It is defined by time multiplied by cost.

#### 5.2 Architectures Suitable for FPGAs

#### 5.2.1 Systolic Array vs. Redundant Representation

As described in Section 4.3, there have been two principle approaches proposed to compute Montgomery modular multiplication.

- 1. Avoid the carry propagation delays by keeping intermediate results in redundant representation. Resolution into binary representation is only done at the very end and for feeding the intermediate result back as  $a_i$  in Algorithm 4.8.

- 2. Systolic Arrays: Processing units compute successive values for a single digit position. The computed carries,  $q_i$  and  $a_i$ , are "pumped" through the processing units.

A solution following approach 1 has already been implemented in FPGAs [33]. A matrix of 16 FPGAs has been used. The second approach using systolic arrays has drawn considerable attention in the research community. However, no architectures that specifically target FPGAs have been reported, nor are there reports of ASIC implementations of such systolic architectures.

The question at hand is which solution is better suited for an FPGA implementation. To answer this we first take a closer look at the equation we have to implement (Section 4.4):

$$q_i = S_i \mod 2^k$$

$$S_{i+1} = (S_i + q_i \cdot \tilde{M})/2^k + a_i \cdot B$$

(5.1)

Equation (5.1) is executed iteratively to compute a modular multiplication. A series of modular multiplications combine to a modular exponentiation according to the square & multiply Algorithms 4.1 or 4.2. Additionally a pre-computation and post-computation are necessary (Section 4.3 and 4.4).

An architecture comprising these computations has two major parts:

1. The arithmetic part computes Equation (5.1). The operands B,  $\tilde{M}$  and  $S_i$  must be stored and multiples of  $\tilde{M}$  and B have to be calculated. Furthermore two additions have to be computed. To avoid a long carry chain, we can divide the adder into units that typically compute one digit of  $S_{i+1}$  in Equation (5.1). If the units compute one iteration of (5.1) at the same time, the result  $S_{i+1}$  must be kept in redundant representation. A separate adder is needed to resolve the redundancy of  $S_{i+1}$  for further processing. In a systolic array approach the units compute an iteration of 5.1 successively. The overflow of a unit is fed as carry to the next unit. In both approaches we have to globally feed  $q_i$  and  $a_i$  to all units. The quotient  $q_i$  is computed once per iteration in the least significant unit. The result of the modular multiplication  $S_{m+3}$  must be stored and reused as operand A for the successive squaring. Therefore all digits of  $S_{m+3}$  need to be distributed to all units of the design.

2. A control and storage part contains the finite state machine (FSM) that controls the execution of the square & multiply algorithm and the pre– and post– computations. We also need storage elements for the pre–computation factor, the exponent and operand A. A is processed serially and has to be distributed digit by digit globally over the arithmetic part.

Clearly, the arithmetic part will utilize most of the resources. Considerations concerning its design will decide between an systolic array and a redundant representation architecture. Some considerations concerning the control part are discussed in Subsection 5.2.2.

Two recent MS theses [22] and [11] in the same field found that a major problem when implementing designs in FPGAs, is the availability of enough routing resources. As discussed in Section 5.1.2, the problem worsens if there are many connections between CLBs which are far apart. When considering an implementation of an *architecture* with *redundant representation* there are some routing issues to deal with:

To compute Equation (5.1) with a radix  $r = 2^k$ ,  $q_i$  and  $a_i$ , each k bits wide and some control signals have to be distributed globally over the arithmetic part. As all redundant digits of  $S_{i+1}$  are computed concurrently, the signals have to arrive at their destination at the same time. The resulting high fan-out causes also considerable propagation delays. Another issue is feeding B and  $\tilde{M}$  to the locations where they are stored and processed. To avoid the full size bus that feeds these signals in parallel, we need a systolic approach at least for the loading of B and  $\tilde{M}$ . Lastly, the redundant result  $S_{m+1}$  of a modular multiplication has to be resolved and distributed as A for further processing. As the low order bits of A are needed first, the resolution of the most significant bits is not critical in terms of propagation delay. The routing, however, is an issue as the full length result has to be stored and distributed all over the arithmetic part.

Routing in a systolic array architecture is much less critical:

In a systolic array architecture we have typically m units, each processing k bits. The k signals  $q_i$  and  $a_i$  and the control signals are "pumped" through the units, from register to register. k bits of  $S_{i+1}$  are computed per clock cycle. Only k bits of the result  $S_{m+1}$  of a modular multiplication are valid at the time. Thus with an additional k bit register per unit we can "pump" the result back through the units. We can further store the result in RAM, k bits at the time, for further processing. So far no connections stretch over more than one unit. If reasonably small units are designed routing is not problematic. B and  $\tilde{M}$  can be loaded over k bit wide buses. The load signal propagates through the units and activates the clock enable of one unit per cycle. Thus only 2k signals have to be routed all over the design.

Summarizing the last two paragraphs, three major advantages of a systolic array architecture were found.

- routing resources Most connections are within one unit or are stretching to an adjacent unit. The availability of enough routing resources is much less an issue compared to an architecture where signals have to be distributed all over the design.

- **propagation delay** A higher clock frequency is possible due to less additional routing delays of long paths.

- synchronous design A fully synchronous design is possible, as we do not need an asynchronous carry completion adder as described in [33], to resolve the redundant representation of the result S.

In contrast to these three advantage, we possibly need more resources to implement a systolic array. A considerable amount of registers is needed for "pumping" the operand A, the quotient Q, the control word and the result S consecutively through the units. CLBs used for implementing registers, however, can be reused for logic functions as pointed out in Section 5.1.1.

#### 5.2.2 State Machine and Storage Elements

We chose a synchronous methodology for all designs presented in this thesis. In the synchronous approach, the clock period is determined by the longest combinatorial delay between two registers.

One of the major goals of this work was to design a high–speed modular exponentiation architecture. This can be done by reducing the amount of iterations in Algorithm 4.8 by choosing a high radix. Secondly the propagation delay of Step 4 in the same algorithm needs to be optimized. This step is typically computed in one clock cycle and determines the minimum clock period.

The FSM and central storage elements have to be designed in such a way that their minimum clock period is smaller than the combinatorial delay of the arithmetic part. To speed–up the FSM as much as possible "one–hot encoding" was used. Each state is represented with an individual bit, resulting in decreased logic complexity associated with each state [1]. On the other hand more registers are needed. We accept this minor disadvantage as the FSM uses only a small percentage of the whole design.

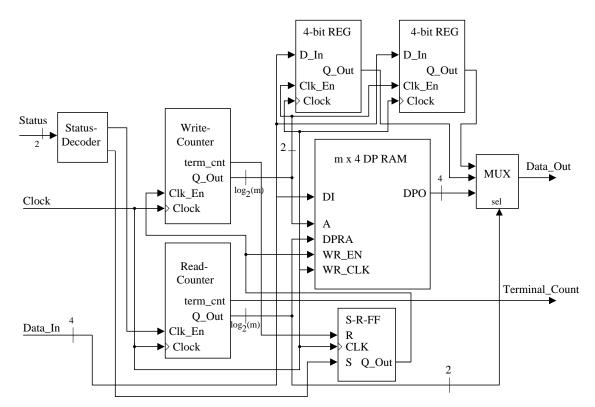

In the central storage elements we need to store data serially. Such data includes the pre-computation factor, the exponent, and intermediate results of the square & multiply algorithm. The usage of RAM saves a large amount of resources compared to registers. A 1024 bit exponent stored in a  $16 \times 64$ -bit RAM uses 32 CLBs, while an equivalent register needs 512 CLBs. RAM with address width larger than 4 bit require more resources and feature larger access delays, due to additional address decoding. The RAM have to be designed in such a way that their access time does not determine the minimal clock period of the design.

## Chapter 6

# Design 1: A Resource Efficient Architecture

In this chapter we describe our first architecture. The goal was to design an area efficient architecture using Algorithm 4.6. As target devices we use the Xilinx XC4000 family as described in Chapter 5. The results of the actual implementation of the architecture will be described in Chapter 9.

#### 6.1 Design Overview

A general radix 2 systolic array as proposed in [10, 35, 8] utilizes m times m processing elements, where m is the number of bits of the modulus and each element processes a single bit. 2m modular multiplications can be processed simultaneously, featuring a throughput of one modular multiplication per clock cycle and a latency of 2m cycles. As this approach would result in unrealistically large CLB counts for the bit length required in modern public–key schemes, we implemented only one row of processing elements. With this approach two modular multiplications can be processed simultaneously and the performance reduces to a throughput of two modular multiplications per 2m cycles. The latency remains 2m cycles.

The second consideration was the choice of the radix  $r = 2^k$ . Increasing k reduces the amount of steps to be executed in Algorithm 4.8. Such an approach, however, requires more resources: The main expense lies in the computation of the  $2^k$  multiples of M and B in Algorithm 4.8. They can either be pre-computed and stored in RAM or calculated by a multiplexer network as proposed in Reference [9]. Clearly, the CLB count becomes smallest for r = 2, as no multiples of M or B have to be calculated or pre-computed.

Using a radix r = 2, the following equation has to be implemented (Algorithm 4.6):

$$S_{i+1} = (S_i + q_i \cdot M)/2 + a_i \cdot B, \ q_i, a_i \in \{0, 1\}$$

To further reduce the required number of CLBs we took the following measures:

- 1. A considerable amount of CLBs are used in the overhead of a processing element (unit). At least  $a_i$ ,  $q_i$  and two control bits have to be stored and decoded in each unit. If only one bit is processed per unit, the overhead is required m times. In order to save resources we implemented units that process u = 4,8,16 bits. With this approach we need only m/u instead of m units, and a considerable amount of overhead can be saved. For processing more than one bit per unit large adders are needed. Thus we expect the processing time and resource requirements to increase exponentially. The possibility to use the fast carry ripple adder as described in Section 5.1.3, however, causes processing time and CLB count to grow only proportionally.

- 2. Computing u bits per unit, the operands  $S_i$ , B and M have all u bits in each unit. The result  $S_{i+1}$  has a maximum of u + 2 bits, u result bits and two carry bits that are fed to the next unit. Instead of using two adders and computing the two additions serially in each execution of the loop, we pre-compute B + M and store the result in a register. The resulting carry is fed to the next unit. Thus we need only one adder, that adds  $S_i$  to 0, B, M or B + M. This adder

is also used for computing B + M. With this approach the result  $S_{i+1}$  is only u + 1 bits wide and just one carry bit is fed to the next unit.

Similar to the approach in [15] we compute squarings and multiplications in parallel. As explained in Section 6.3, this measure fully utilizes every cycle.

Design 1 can be divided hierarchically into three levels.

- **Processing Element** Computes u bits of a modular multiplication.

- Modular Multiplication An array of processing elements computes a modular multiplication.

- Modular Exponentiation Combine modular multiplications to a modular exponentiation according to Algorithm 4.2.

In the following we describe the system with a bottom-up approach.

### 6.2 Processing Elements

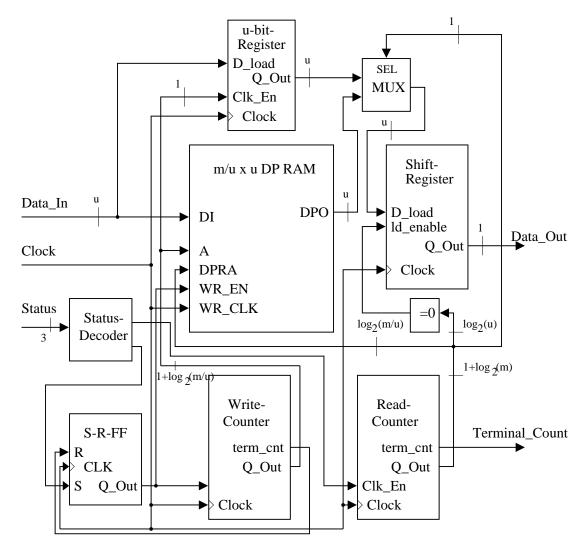

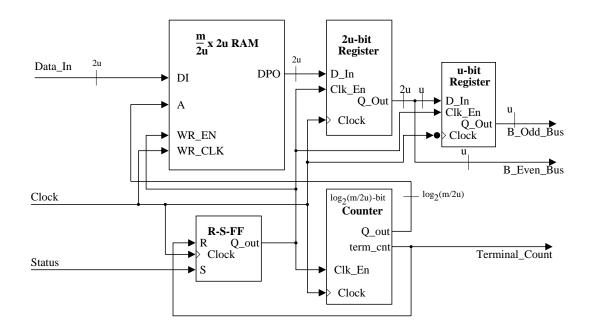

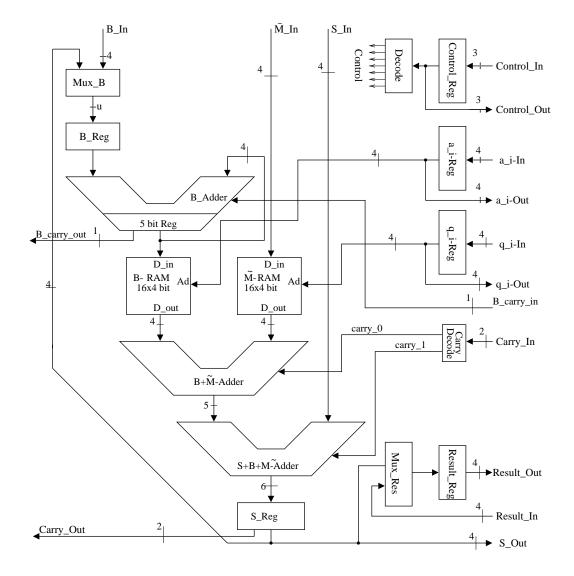

Figure 6.1 shows the implementation of a processing element.

In the processing elements we need the following registers:

- *M-Reg* (*u* bits): storage of the modulus

- B-Reg (u bits): storage of the B multiplier

- B+M-Reg (u bits): storage of the intermediate result B+M

- S-Reg (u + 1 bits): storage of the intermediate result (inclusive carry)

- S-Reg-2 (u-1 bits): storage of the intermediate result

- Control-Reg (3 bits): control of the multiplexers and clock enables

35

Figure 6.1: Processing element (unit) of Design 1 that computes  $S_{i+1} = (S_i + q_i \cdot M)/2 + a_i \cdot B, q_i, a_i \in \{0, 1\}$

- $a_i, q_i$  (2 bits): multiplier A, quotient Q

- Result-Reg (u bits): storage of the result at the end of a multiplication

The registers need a total of (6u + 5)/2 CLBs, the adder u/2 + 2 CLBs, the multiplexers  $4 \cdot u/2$  CLBs, and the decoder 2 CLBs. The possibility of re-using registers for combinatorial logic allows some savings of CLBs.  $Mux_B$  and  $Mux_{Res}$  are implemented in the CLBs of *B-Reg* and *Result-Reg*,  $Mux_1$  and  $Mux_2$  partially in *M-Reg* and *B+M-Reg*. The resulting costs are approximately 3u + 4 CLBs per *u*-bit processing unit. That is 3 to 4 CLBs per bit, depending on the unit size *u*.

Let's compare this expense to the resources needed for a one bit unit implemen-

tation (u = 1). We would need a total of seven bit register space  $(M, B, a_i, q_i, \text{control}(2)$  and result) plus eventually a B + M register and a 4-bit input – 3 bit output (2 carries, result) adder. Together with one or two CLBs for decoding the control word and multiplexing, we would have a total of 6 or 7 CLBs per unit. With such a large amount of CLBs we can implement a much faster architecture, as we will see in Chapter 7.

Before a unit can compute a modular multiplication, the system parameters have to be loaded. M is stored into M-Reg of the unit. At the beginning of a modular multiplication, the operand B is loaded from either B-in or S-Reg, according to the select line of multiplexer B-Mux. The next step is to compute M + B once and store the result in the B+M-Reg. This operation needs two clock cycles, as the result is clocked into S-Reg first. The select lines of  $Mux_1$  and  $Mux_2$  are controlled by  $a_i$  or the control word respectively.

In the following 2(m + 2) cycles a modular multiplication is computed according to Algorithm 4.6. Multiplexer  $Mux_1$  selects one of its inputs 0, M, B, B + M to be fed in the adder according to the value of the binary variables  $a_i$  and  $q_i$ .  $Mux_2$  feeds the u - 1 most significant bits of the previous result S-Reg<sub>2</sub> plus the least significant result bit of the next unit (division by two/shift right) into the second input of the adder. The result is stored in S-Reg for one cycle. The least significant bit goes into the unit to the right (division by two / shift right) and the carry to the unit to the left. In this cycle a second modular multiplication is calculated in the adder, with updated values of S-Reg<sub>2</sub>,  $a_i$  and  $q_i$ . The second multiplication uses the same operand B but a different operand A.

At the end of a modular multiplication,  $S_{m+3}$  is valid for one cycle at the output of the adder. This value is both stored into *Result-Reg*, as fed via *S-Reg* into *B-Reg*. The result of the second multiplication is fed into *Result-Reg* one cycle later.

#### 6.3 Modular Multiplication

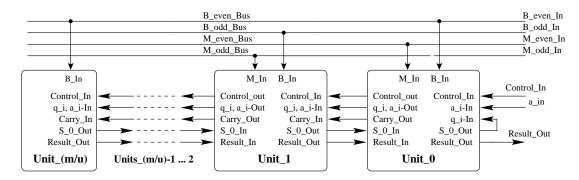

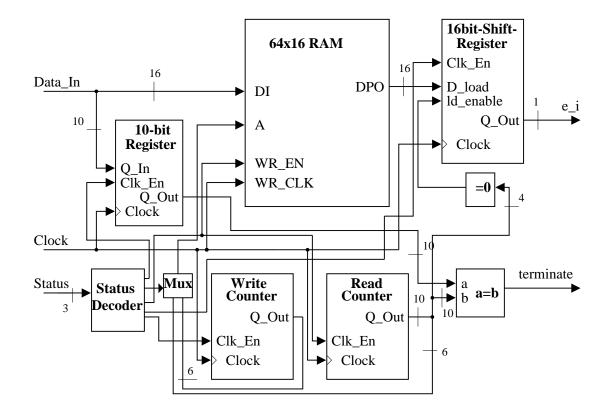

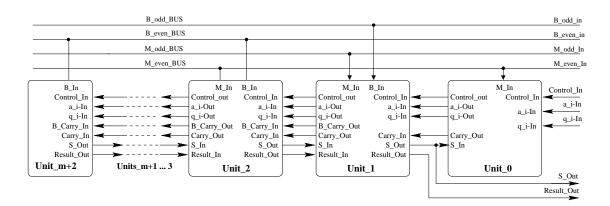

Figure 6.2 shows how the processing elements are connected to an array for computing an *m*-bit modular multiplication. To compute  $S_{i+1} = (S_i + q_i \cdot M)/2 + a_i \cdot B$  with  $M = \sum_{i=0}^{m-1} 2^i \cdot m_i$ , we need m/u + 1 units.  $Unit_1 \dots Unit_{(m/u)-1}$  are designed as described in Section 6.2.  $Unit_0$  has only u - 1 B inputs as  $B_0$  is added to a shifted value  $S_i + q_i M$ . The result bit S-Reg<sub>0</sub> is always zero according to the properties of Montgomery's algorithm.  $Unit_{m/u}$  processes the most significant bit of B and the temporary overflow of the intermediate result  $S_{i+1}$ . There is no M input into this unit.

Figure 6.2: Systolic Array for modular multiplication

The inputs and outputs of the units are connected to each other in the following way. The control word,  $q_i$  and  $a_i$  are pumped from right to left through the units. The result is pumped from left to right. The *carry-out* signals are fed to the *carry-in* inputs to the right. Output  $S_0$  out is always connected to input  $S_0$ . In of the unit to the right. This represents the division by 2 of the equation.

At first the modulus M is fed into the units. To allow enough time for the signals to propagate to all the units, M is valid for two clock cycles. We use two M-Buses, the M-even-Bus connected to all even numbered units  $unit_0$ ,  $unit_2 \ldots unit_{m/u}$ , and the M-odd-Bus connected to all odd numbered units  $unit_1$ ,  $unit_3 \ldots unit_{(m/u)-1}$ . This approach allows to feed u bits of  $\tilde{M}$  to the units per clock cycle. Thus it takes m/u cycles to load the full modulus M.

The operand B is loaded similarly. The signals are also valid for two clock cycles. We also use two *B-Buses*, the *B-even-Bus* connected to all even numbered units  $unit_0, unit_2 \dots unit_{m/u}$ , and the *B-odd-Bus* connected to all odd numbered units  $unit_1$ ,  $unit_3 \dots unit_{(m/u)-1}$ .

After the operand B is loaded, the computation of Algorithm 4.6 can begin. Starting at the rightmost  $unit_0$ , the control word,  $a_i$ , and  $q_i$  are fed into their registers. The adder computes S-Reg-2 plus B, M, or B + M in one clock cycle according to  $a_i$  and  $q_i$ . The least significant bit of the result is read back as  $q_{i+1}$  for the next computation. The resulting carry bit, the control word,  $a_i$  and  $q_i$  are pumped into the unit to the left, where the same computation takes place in the next clock cycle. In such a systolic fashion the control word,  $a_i$ ,  $q_i$ , and the carry bits are pumped from right to left through the whole unit array. The division by two in Algorithm 4.6 leads also to a shift-right operation. The least significant bit of a unit's addition ( $S_0$ ) is always fed back into the unit to the right. After a modular multiplication is completed, the results are pumped from left to right through the units and consecutively stored in RAM for further processing.

A single processing element computes u bits of  $S_{i+1} = (S_i + q_i \cdot M)/2 + a_i \cdot B$  of Algorithm 4.6. In clock cycle i,  $unit_0$  computes bits  $0 \dots u - 1$  of  $S_i$ . In cycle i + 1,  $unit_1$  uses the resulting carry and computes bits  $u \dots 2u - 1$  of  $S_i$ .  $Unit_0$  uses the right shifted (division by 2) bit u of  $S_i$  ( $S_0$ ) to compute bits  $0 \dots u - 1$  of  $S_{i+1}$  in clock cycle i + 2.

Clock cycle i + 1 is unproductive in  $unit_0$  while waiting for the result of  $unit_1$ . This inefficiency is avoided by computing squares and multiplications in parallel according to Algorithm 4.2. Both  $p_{i+1}$  and  $z_{i+1}$  depend on  $z_i$ . We therefore store the intermediate result  $z_i$  in the *B*-Registers and feed  $z_i$  and  $p_i$  into the  $a_i$  input of the units for squaring and multiplication.

#### 6.4 Modular Exponentiation

#### 6.4.1 Data Flow

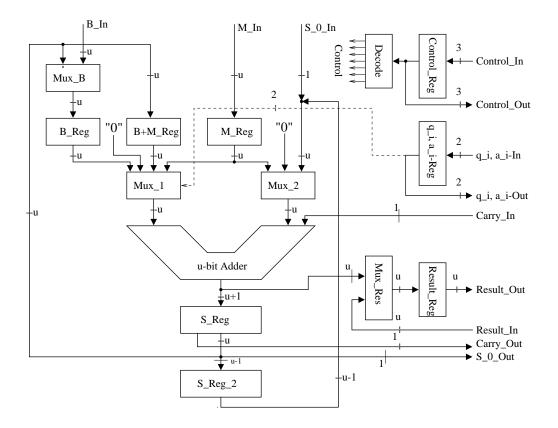

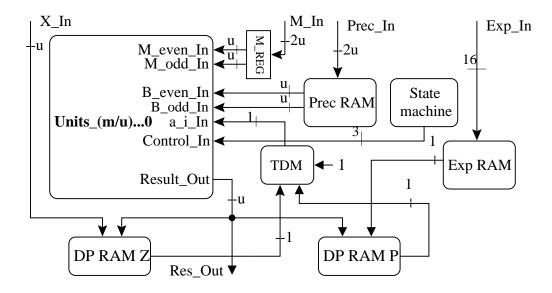

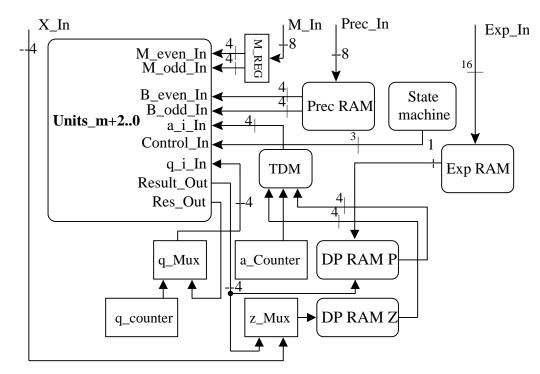

Figure 6.3 shows how the array of units is utilized for modular exponentiation. At the heart of our design is a finite state machine (FSM) with 17 states. An *idle* state, four states for loading the system parameters, and four times three states for computing the modular exponentiation. The actual modular exponentiation is executed in four main states, *pre-computation*<sub>1</sub>, *pre-computation*<sub>2</sub>, *computation*, and *post-computation*. Each of these main states is subdivided in three sub-states, *load-B*, B+M, and *calculate-multiplication*. The control word fed into *control-in* is encoded according to the states. The FSM is clocked at half the clock rate. The same is true for loading and reading the RAM and DP RAM elements. This measure makes sure the maximal propagation time is in the units. Thus the minimal clock cycle time and the resulting speed of a modular exponentiation relates to the effective computation time in the units and not to the computation of overhead.

Before a modular exponentiation is computed, the system parameters have to be loaded. The modulus M is read 2u bits at the time from I/O into M-Reg. Reading starts from low order bits to high order bits. M is fed from M-Reg u bits at the time alternatively to M-even-Bus and M-odd-Bus. The signals are valid two cycles at a time. The exponent E is read 16 bits at the time from I/O and stored into Exp-RAM. The first 16 bit wide word from I/O specifies the length of the exponent in bits. Up to 64 following words contain the actual exponent. The pre-computation factor  $2^{2(m+2)} \mod M$  is read from I/O 2u bits at the time. It is stored into Prec-RAM.

In state Pre-compute<sub>1</sub> we read the X value from I/O, u bits per clock cycle, and store it into DP RAM Z. At the same time the pre–computation factor  $2^{2(m+2)} \mod$

Figure 6.3: Design for a modular exponentiation

M is read from *Prec RAM* and fed u bits per clock cycle alternatively via the *B-even-Bus* and *B-odd-Bus* to the *B*-registers of the units. In the next two clock cycles, B + M is calculated in the units.

Now we begin calculating the pre-computation. The initial values of Algorithm 4.2 are  $P_0 = 1$  and  $Z_0 = X$ . Both values have to be multiplied by  $2^{2(m+2)} \mod M$ . This can be done in parallel as both multiplications use a common operand  $2^{2(m+2)} \mod M$ , that is already stored in B. The time division multiplexing unit (TDM) reads X from  $DP \ RAM \ Z$  and multiplexes X and  $1, 0 \dots 0$  on the  $a_i$ -bus into the units.

After 2(m+3) clock cycles the low order bits of the result of MONT\_R2( $2^{2(m+2)}$  mod M, X) =  $X \cdot 2^{m+2}$  mod M appear at *Result-Out* and are stored in *DP RAM Z*. The low order bits of the result of MONT\_R2( $2^{2(m+2)} \mod M, 1$ ) =  $2^{m+2} \mod M$  appear at *Result-Out* one cycle later and are stored in *DP RAM P*. This process repeats for 2m cycles, until all digits of the two results are saved in *DP RAM Z* and *DP RAM P*. The result  $X \cdot 2^{m+2} \mod M$  is also stored in the *B*-registers of the units.

In state  $pre-compute_2$  the actual computation of Algorithm 4.2 begins. For both

calculations of  $Z_1$  and  $P_1$  we use  $Z_0$  as an operand. This value is stored in the *B*-registers. The second operand  $Z_0$  or  $P_0$  respectively, is read from *DP RAM Z* and *DP RAM P* and "pumped" via *TDM* as  $a_i$  into the units. After another 2(m + 3) clock cycles the low order bits of the result of  $Z_1$  and  $P_1$  appear at *Result-Out.*  $Z_1$  is stored in *DP RAM Z*.  $P_1$  is needed only if the first bit of the exponent  $e_0$  is equal to "1". Depending on  $e_0$ ,  $P_1$  is either stored in *DP RAM P* or discarded.

In state *compute* the loop of Algorithm 4.2 is executed n - 1 times.  $Z_i$  in *DP RAM Z* is updated after every cycle and "pumped" back as  $a_i$  into the units.  $P_i$  in *DP RAM P* is updated only if the relevant bit of the exponent  $e_i$  is equal to "1". In this way always the last stored  $P_i$  is "pumped" back into the units.