# Split Non-Linear Cyclic Analog-to-Digital Converter

By Shant Orchanian

The design, layout and simulation of a Cyclic ADC in the 0.18µm process that is fully differential, self-calibrating and performs 1 million samples per second.

A Thesis

Submitted to the Faculty of WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the Degree of Master of Science in Electrical and Computer Engineering

by

Shant Orchanian

April 2010

APPROVED:

Professor John A. McNeill, Major Advisor

Professor Stephen J. Bitar

Professor Donald R. Brown

# ABSTRACT

Analog-to-Digital Converters (ADC's) are inherently optimized for linearity in order to produce an accurate digital representation of an analog voltage. The Cyclic ADC's linearity is limited by one of its components, the residue amplifier. The residue amplifier is used to amplify the error between the analog voltage and the digital decision by a gain of two in each cycle of a conversion. In previous designs, this was accomplished by using a compound op-amp with a large open loop gain for linearity, and negative feedback to achieve the gain of two. This thesis explores the use of a resistively loaded differential pair to achieve this gain. The design reduces die size, power usage, and analog complexity. To correct for this inherent non-linearity, a Split ADC concept is employed to enable digital background calibration and a correction algorithm to account for this non-linearity. The Integrated circuit is designed, laid out, and simulated using the Cadence Integrated Circuit Front to Back design suite (ICFB) in the 0.18um Jazz CMOS process.

# TABLE OF CONTENTS

| 1 | Ι   | ntrod  | luction                                   | . 8 |

|---|-----|--------|-------------------------------------------|-----|

|   | 1.1 | G      | oals and Specifications                   | . 8 |

|   | 1.2 | Р      | roject Motivation                         | .9  |

|   | 1   | 1.2.1  | Non-Linearity                             | .9  |

|   | 1   | 1.2.2  | Digital Calibration                       | .9  |

|   | 1   | 1.2.3  | Simplicity and Innovation                 | 10  |

| 2 | F   | Prefac | ce                                        | 11  |

| 3 | E   | Backg  | round                                     | 12  |

|   | 3.1 | А      | nalog-to-Digital Converters               | 12  |

|   | 3.2 | A      | DC Performance Metrics                    | 12  |

|   | 3.3 | 0      | Oversampling Converters                   | 16  |

|   | 3.4 | N      | lyquist Converters                        | 17  |

|   | 3   | 3.4.1  | Pipelined ADCs                            | 17  |

|   | 3   | 3.4.2  | Successive Approximation ADCs             | 18  |

|   | 3   | 3.4.3  | The Cyclic ADC                            | 22  |

|   | 3.5 | Т      | 'he Role of Capacitors                    | 24  |

|   | 3   | 3.5.1  | Thermal Noise                             | 24  |

|   | 3.6 | 0      | Options for Output Driving                | 25  |

|   | 3   | 3.6.1  | Understanding LVDS                        | 25  |

|   | 3   | 3.6.2  | The Concepts behind LVDS                  | 25  |

|   | 3   | 3.6.3  | Different Types of LVDS                   | 26  |

|   | 3   | 3.6.4  | Contrasting LVDS Types and Configurations | 27  |

|   | 3   | 3.6.5  | A Typical LVDS Circuit                    | 28  |

|   | 3   | 3.6.6  | Applications                              | 29  |

|   | 3   | 3.6.7  | Assessing LVDS in the ADC Design Process  | 29  |

|   | 3.7 | Т      | 'he Split-ADC Concept                     | 30  |

| 3 | 3.8 | The    | e Current Mirror                                          | 31 |

|---|-----|--------|-----------------------------------------------------------|----|

| 3 | 3.9 | The    | e Differential Pair                                       | 33 |

|   | 3.9 | .1     | Bartlett's Bisection Theorem                              | 34 |

| 4 | Hig | gh-Lev | vel Design                                                | 37 |

| 2 | 4.1 | Blo    | ck Diagram                                                | 37 |

| 5 | Th  | e Inpı | ut Block                                                  |    |

| 5 | 5.1 | Tra    | nsistor Size Optimization                                 |    |

|   | 5.1 | .1     | Dealing with the Presence of Distortion                   |    |

|   | 5.1 | .2     | Performing a Parametric Analysis                          | 40 |

|   | 5.1 | .3     | Choosing Total Width                                      | 44 |

| 4 | 5.2 | Red    | lucing the Noise Floor                                    | 45 |

|   | 5.2 | .1     | Resistor Tolerance                                        | 47 |

|   | 5.2 | .2     | Implementation of Input Block                             | 48 |

|   | 5.2 | .3     | Layout of the Input block                                 | 50 |

| 6 | Th  | e Swi  | tched Capacitor Network                                   | 51 |

| e | 5.1 | Def    | ining the Correct Number of Capacitors for the Network    | 52 |

|   | 6.1 | .1     | Using One Capacitor                                       | 52 |

|   | 6.1 | .2     | Using Two Capacitors                                      | 53 |

|   | 6.1 | .3     | Testing the Two Capacitor System                          | 54 |

| e | 5.2 | The    | e Final Switch Capacitor Design: Four Capacitors          | 55 |

| e | 5.3 | Lay    | out of the Switched Capacitor Circut                      | 60 |

| e | 5.4 | Det    | ermining Voltage Reference Values for Switched Capacitors | 61 |

| 7 | Dif | feren  | tial Amplifier                                            | 62 |

| 7 | 7.1 | Fun    | damental Components of the Differential Amplifier         | 62 |

| 7 | 7.2 | Diff   | Ferential Amplifier Voltage Levels                        | 63 |

|   | 7.2 | .1     | KT/C Capacitor Sizing                                     | 66 |

|   | 7.2 | .2     | Derivations of Resistive Load Values and Bias Current     | 67 |

|   |     |        | 4                                                         |    |

|   | 7. | 3     | Rep  | lica Bias Analysis                                                    | 68  |

|---|----|-------|------|-----------------------------------------------------------------------|-----|

|   |    | 7.3.1 | 1    | Advantages and Purpose of Using Replica Bias                          | 68  |

|   |    | 7.3.2 | 2    | Designing Replica Bias                                                | 68  |

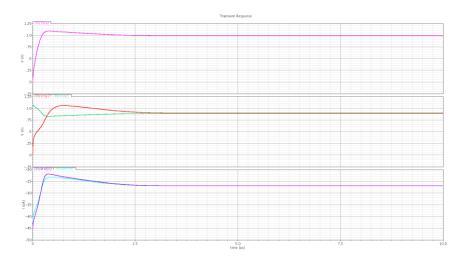

|   |    | 7.3.3 | 3    | Simulation of the Replica Bias Circuit                                | 69  |

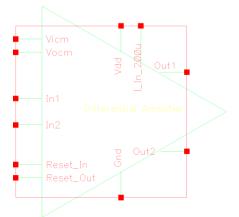

|   |    | 7.3.4 | 1    | Differential Pair Symbol Representation                               | 69  |

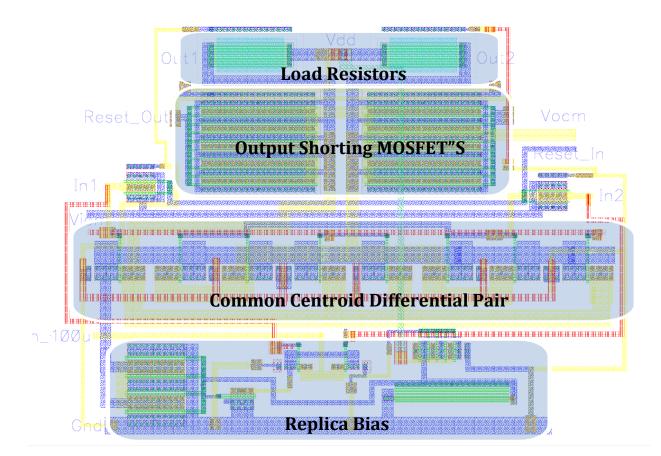

|   |    | 7.3.5 | 5    | Differential Pair Layout                                              | 70  |

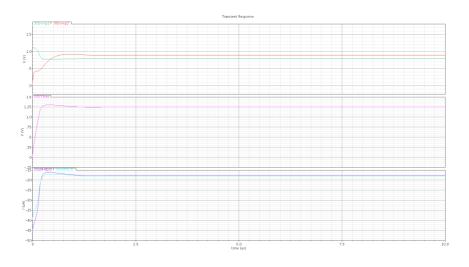

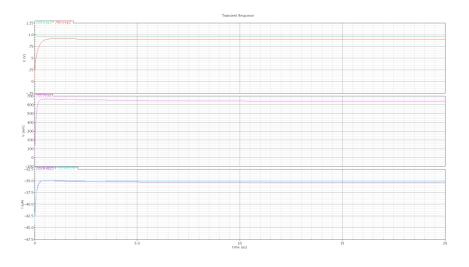

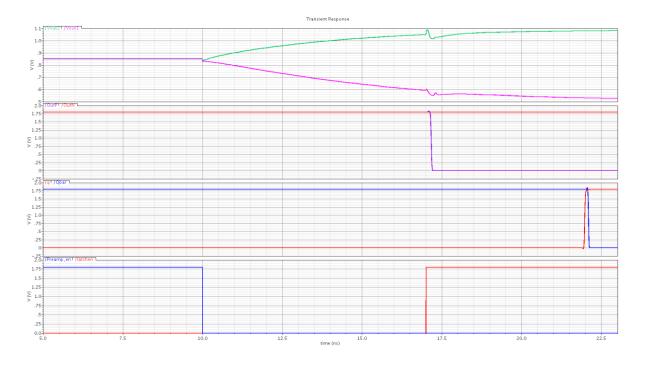

|   |    | 7.3.6 | 6    | Differential Pair Extracted Simulation                                | 71  |

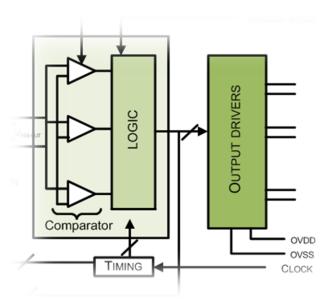

| 8 |    | The   | Logi | c Block                                                               | 72  |

|   | 8. | 1     | driv | ring transistor gates                                                 | 72  |

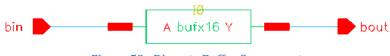

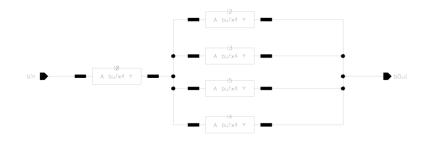

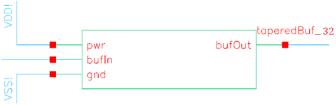

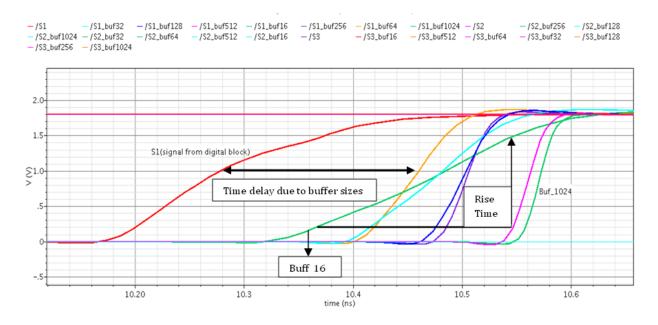

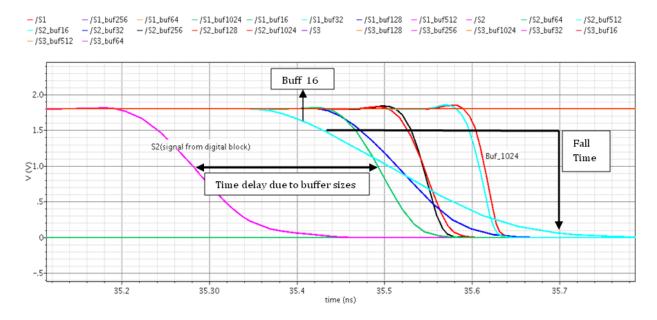

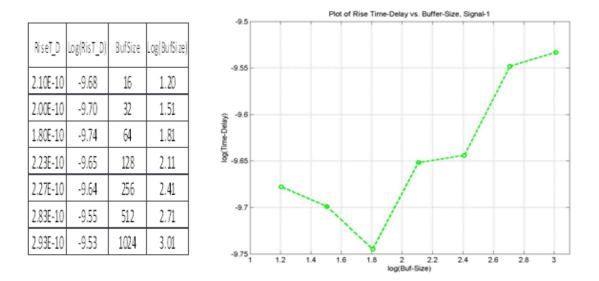

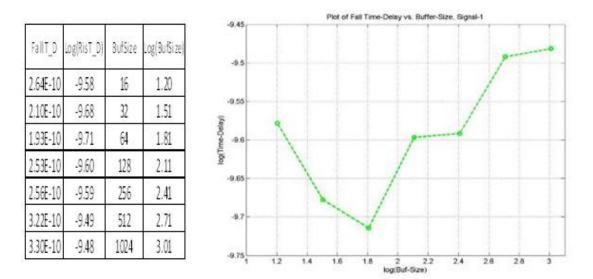

|   |    | 8.1.1 | 1    | Tapered Buffer                                                        | 73  |

|   |    | 8.1.2 | 2    | Advantages of Using Tapered Buffers                                   | 73  |

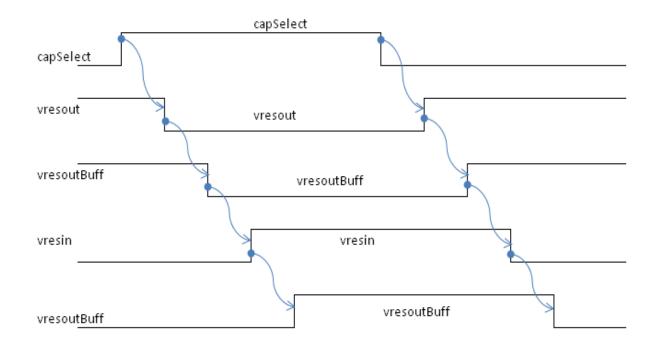

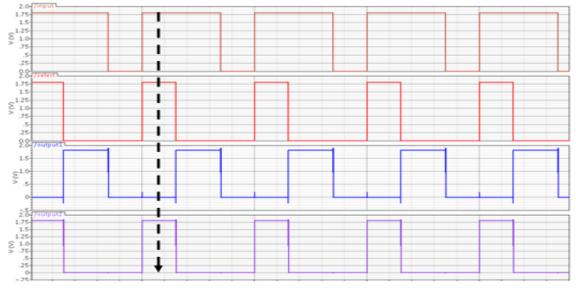

|   | 8. | 2     | sam  | ple and hold circuit simulations                                      | 75  |

|   |    | 8.2.2 | 2    | Layout of Sample and hold Buffers                                     | 82  |

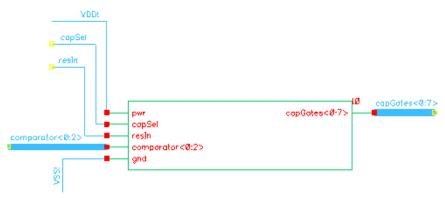

|   | 8. | 3     | Driv | ving Transistor Gates at Capacitor Array                              | 84  |

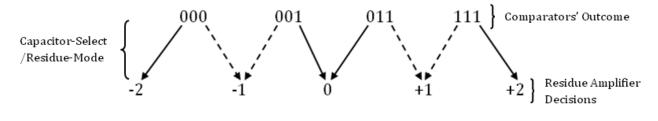

|   |    | 8.3.1 | 1    | Implementing Residue Amplifier Decisions                              | 85  |

|   |    | 8.3.2 | 2    | Example of a Decision Implementation                                  | 86  |

|   |    | 8.3.3 | 3    | Final Step in Designing the Gate Digital Driver                       | 87  |

|   |    | 8.3.4 | 1    | Layout of the Gate Digital Driver                                     |     |

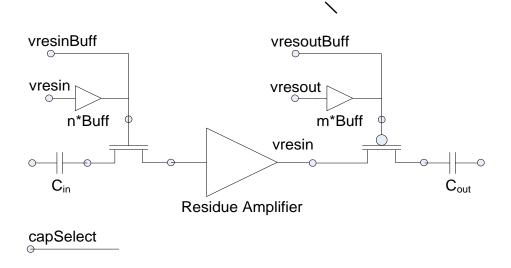

|   | 8. | 4     | Driv | ving Transistor Gates of Input-Output Capacitors of Residue Amplifier | 89  |

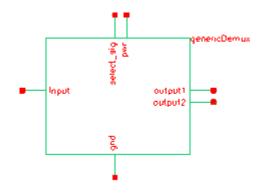

|   | 8. | 5     | Des  | igning "genericDemux"                                                 | 91  |

|   |    | 8.5.1 | 1    | "genericDemux" Symbol Representation                                  | 92  |

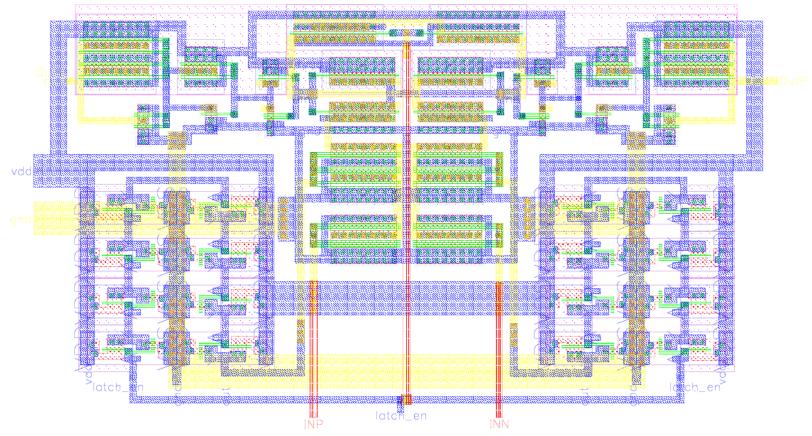

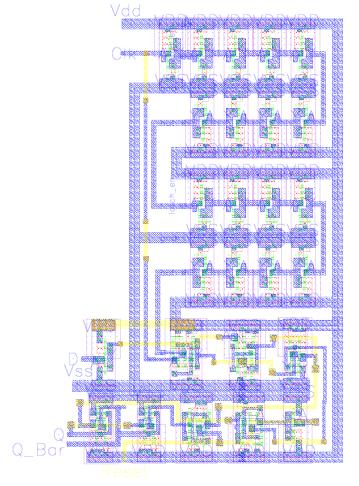

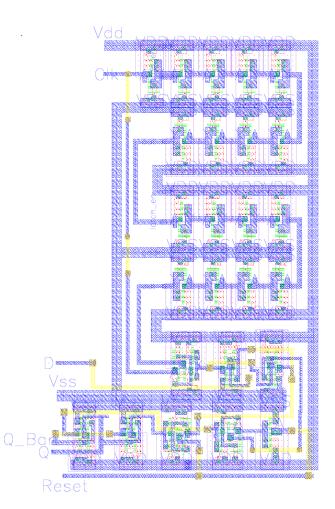

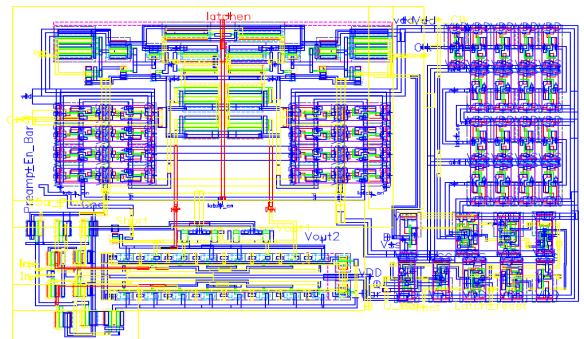

|   |    | 8.5.2 | 2    | Layout Of The Digital Block                                           | 93  |

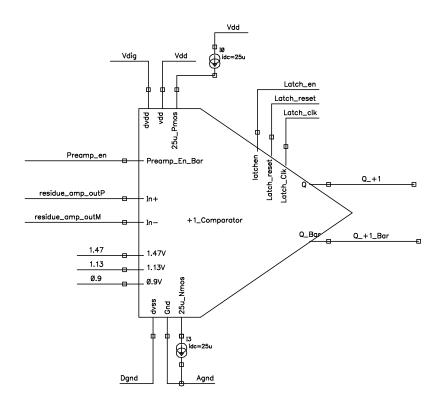

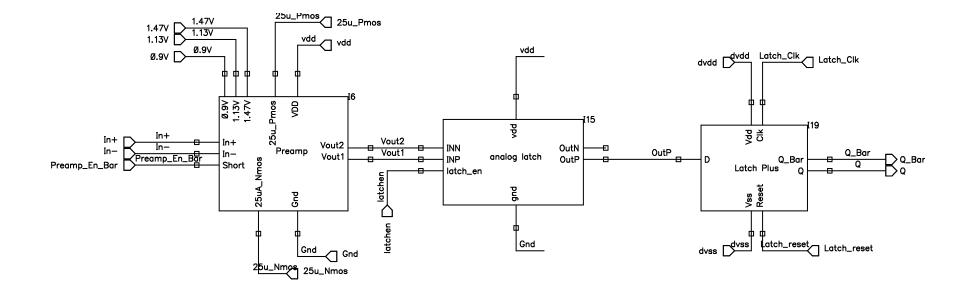

| 9 |    | The   | Com  | iparators                                                             | 94  |

|   | 9. | 1     | The  | Pre-Amplifiers                                                        | 94  |

|   |    | 9.1.1 | 1    | The ±1 Preamp                                                         | 94  |

|   |    | 9.1.2 | 2    | The 0 Preamp                                                          |     |

|   | 9. | 2     | Ana  | log Latch                                                             | 104 |

| 9.2     | 2.1 Layout of the Analog Latch            |     |

|---------|-------------------------------------------|-----|

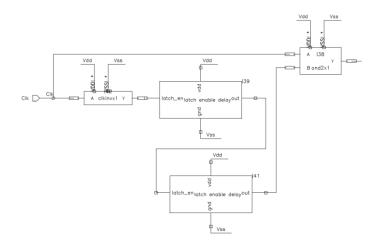

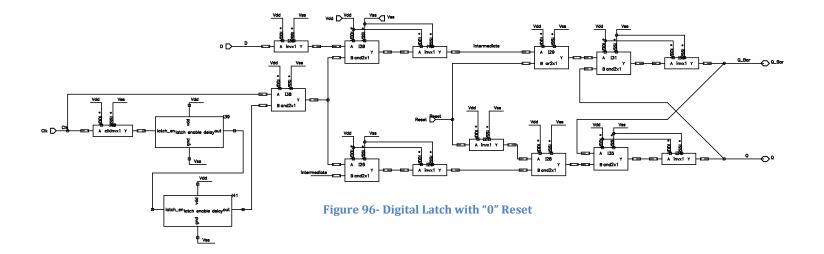

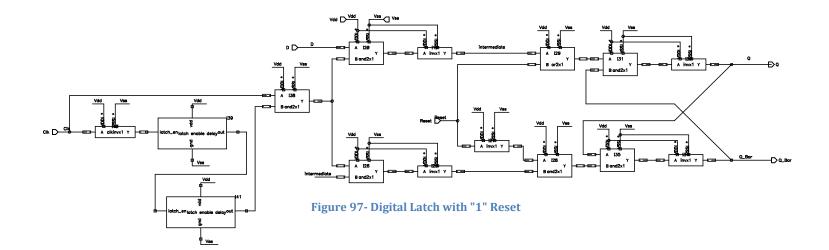

| 9.3     | Digital latch                             |     |

| 9.3     | 3.1 Layout of the Digital Latches         |     |

| 9.4     | Putting it all together                   |     |

| 9.4     | 4.1 Layout of Complete Comparators        |     |

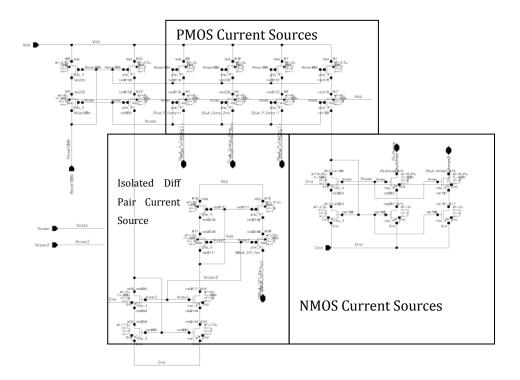

| The Bia | as Block                                  |     |

| 9.5     | Problems with Bias Block                  |     |

| 9.6     | Results of Isolation                      |     |

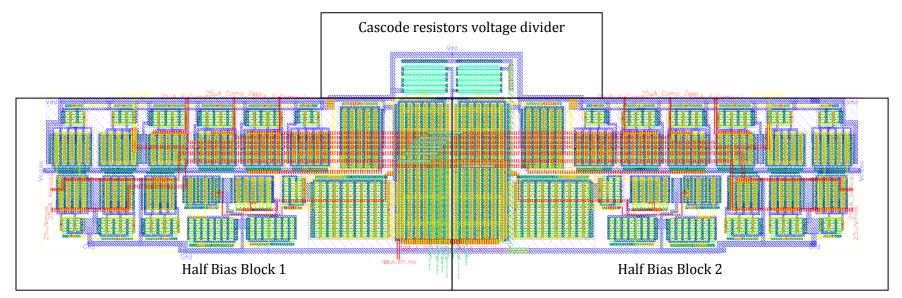

| 9.7     | Layout of the Bias Block                  |     |

| 10 7    | The Output Block                          |     |

| 10.1    | Creating LVDS Drivers                     |     |

| 10.2    | Making the Choice between LVDS and LVCMOS |     |

| 10.3    | Output Process                            |     |

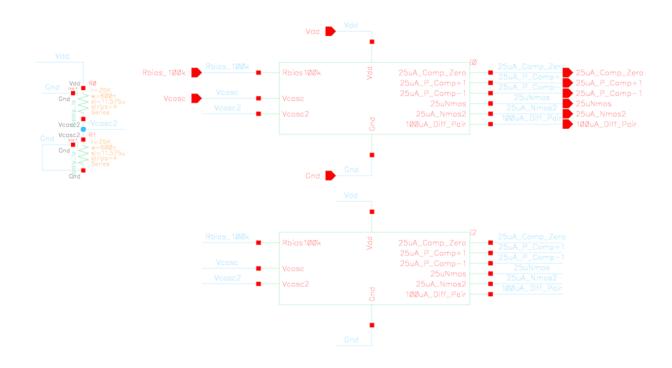

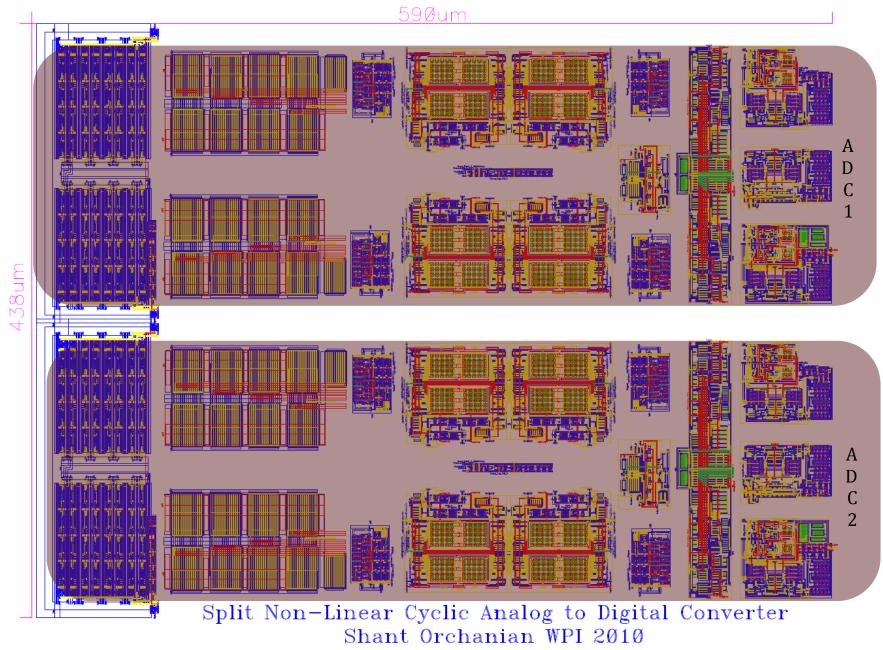

| 11      | Putting it All Together                   |     |

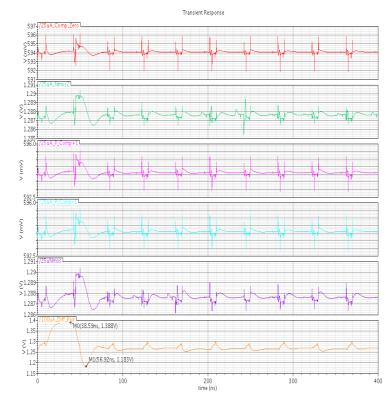

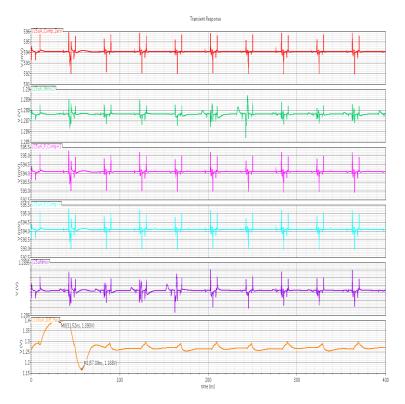

| 11.1    | Full Chip Schematic Simulations           |     |

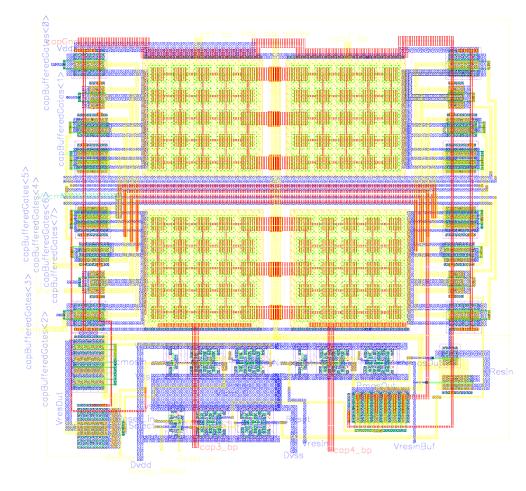

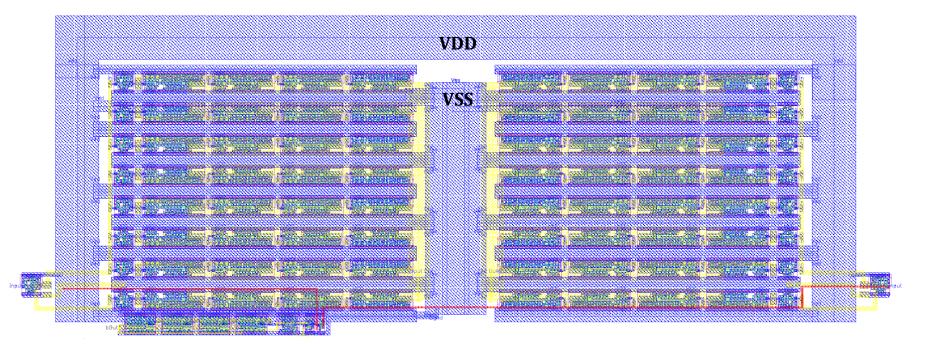

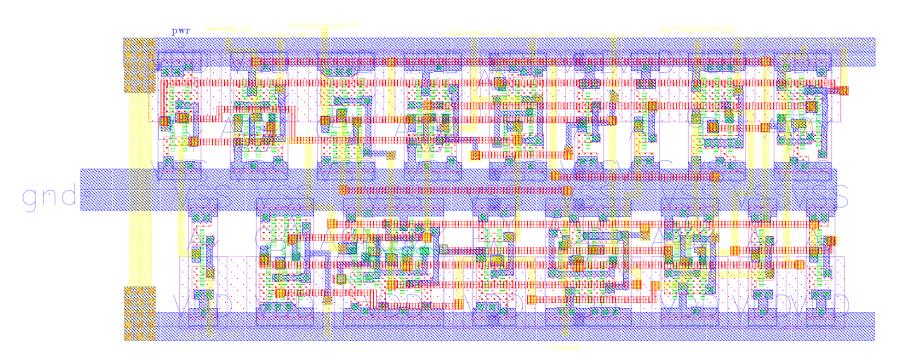

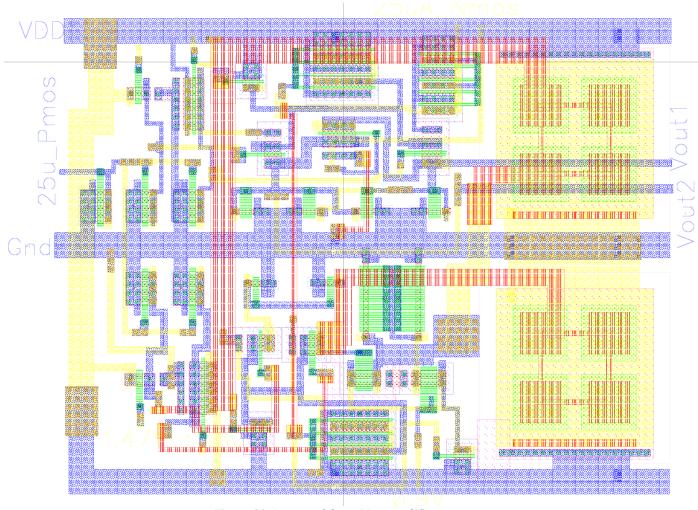

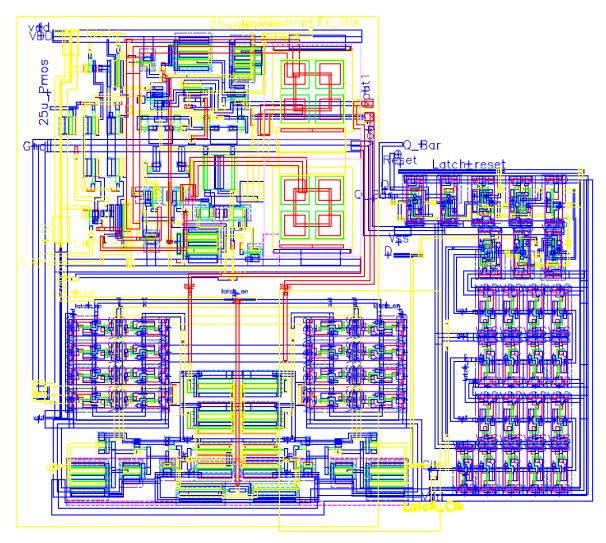

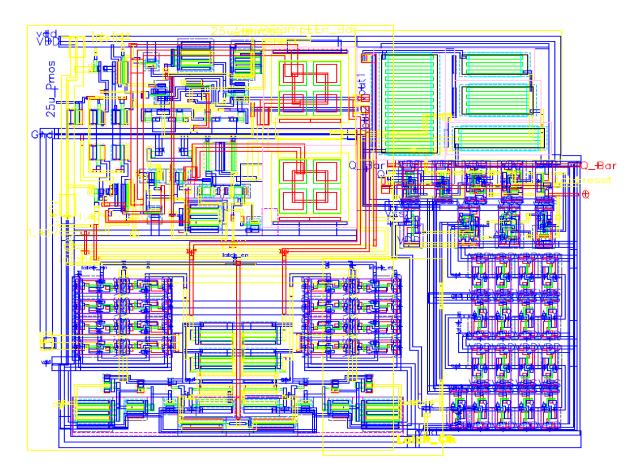

| 11.2    | Layout of completed ADC                   |     |

| 11.3    | Extracted simulations of the complete ADC |     |

| 12      | Noise Analysis                            |     |

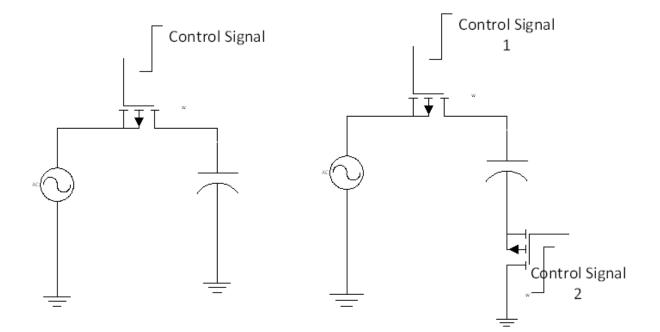

| 12.1    | Circuit Schematic                         |     |

| 12.2    | Bandwidth of Residue Amplifier            |     |

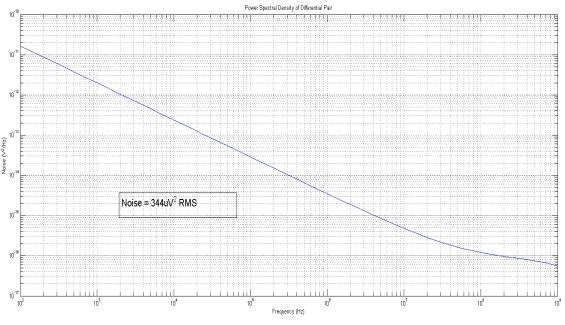

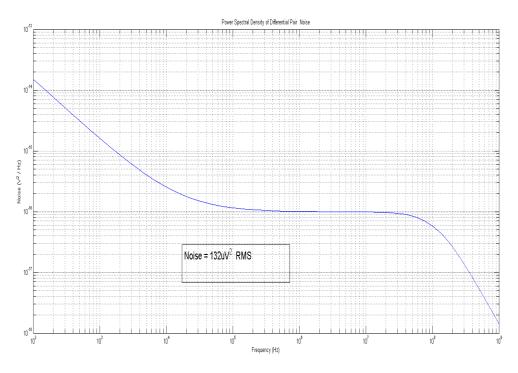

| 12.3    | Noise in the Differential Pair            |     |

| 12      | .3.1 Resistor Noise                       |     |

| 12      | .3.2 Replica Bias Noise                   |     |

| 12.4    | Noise Simulations using Cadence           |     |

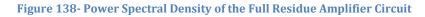

| 12.5    | 1/f noise                                 | 140 |

| 12.6    | Choosing the length of the MOSFET's       | 142 |

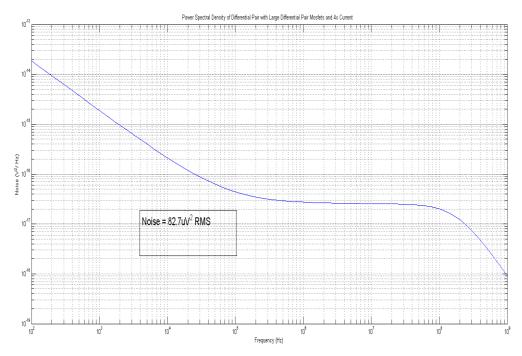

| 12.7    | Increasing Bias Current                   | 142 |

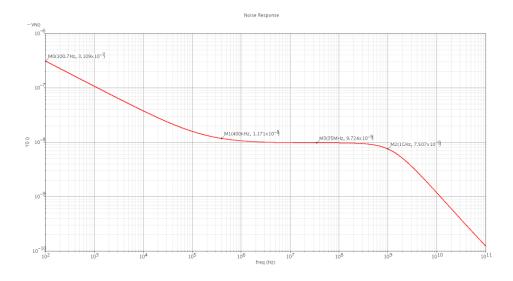

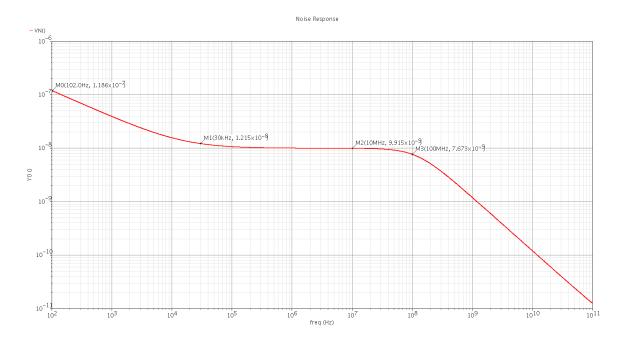

| 12. | 8  | Noise modeling of Actual Differential Pair             | . 143 |

|-----|----|--------------------------------------------------------|-------|

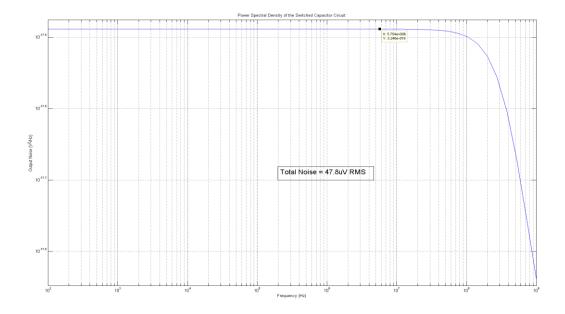

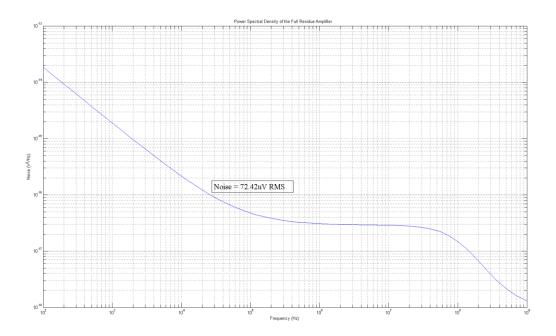

| 12. | 9  | Total Noise with Modified Circuit                      | .146  |

| 12. | 10 | Feasibility of reducing noise using current techniques | . 147 |

| 12. | 11 | Other ways to reduce 1/f Noise                         | . 147 |

| 13  | Ir | nnovation                                              | . 149 |

| 14  | С  | onclusion                                              | . 151 |

| 14. | 1  | Issues with Design                                     | .151  |

| 14. | 2  | Impact of Project                                      | . 152 |

| 15  | Т  | able of figures                                        | . 153 |

| 16  | В  | ibliography                                            | . 158 |

# **1** INTRODUCTION

The electronics world is faced with various challenges when attempting to integrate analog signals with digital and discrete systems. Therefore, the existence of a tool that enables this integration is vital to many electrical engineers in today's world. The Analog-to-Digital Converter (ADC) is not a new concept by any means, but is still a topic of interest when it comes to technology, due to its inevitable necessity in many systems being used today. Mixed Signal design engineers are always faced with important questions, such as: How can signals be converted faster, more accurately? How does one optimize systems to achieve simpler, yet smarter converters? Other issues, such as power consumption, complexity, interaction with other systems, price, and test time have spawned several different types and designs of analog-to-digital converters. Yet, the market is still open to different options. This project focuses on presenting a new option among the many present, with distinct features that are aimed to satisfy various applications for analog-to-digital converters.

# 1.1 GOALS AND SPECIFICATIONS

The goal of this project is to design, layout and complete extracted simulations of a Split Non-Linear Cyclic ADC, resulting in a design that is able to use a digital background calibration algorithm to correct for non-linearity inherent in the residue amplifier and manufacturing non idealities. The specifications of this Cyclic ADC are shown below.

| Гable 1 · | Specifi | cations |

|-----------|---------|---------|

|-----------|---------|---------|

| Specifications              |                    |  |  |  |  |

|-----------------------------|--------------------|--|--|--|--|

| Circuit Type                | Integrated Circuit |  |  |  |  |

| Maximum Size                | 1 mm <sup>2</sup>  |  |  |  |  |

| Process Type                | 0.18 μm            |  |  |  |  |

| Resolution                  | 12 Bits            |  |  |  |  |

| Throughput                  | 1 Msps             |  |  |  |  |

| <b>Other Specifications</b> | Fully Differential |  |  |  |  |

The project is sponsored by the New England Center for Analog and Mixed Signal Design (NECAMSID) located at WPI. This Integrated Circuit was designed using Cadence's ICFB (Integrated Circuit Front to Back design simulator) and the simulation models used are from Jazz Semiconductor's model library.

# 1.2 PROJECT MOTIVATION

This project is an extension of a MQP completed by in 2009 by Shant Orchanian, Alvaro Soares Jr. and Gentian Rrudho in which fundamental blocks for a Cyclic ADC was designed. This project was suggested to the group by Professor John McNeill, who had previously worked in a similar Cyclic ADC which employed a linear gain phase and used a digital calibration algorithm to correct for mismatch errors and doping gradients in the IC manufacturing process. This project shows itself to be unique due to a combination of characteristics.

# 1.2.1 NON-LINEARITY

One of the most interesting aspects of this design is that a linear input and output relationship within the chip's differential amplifier is not necessary. This concept is very appealing to integrated circuit designers because it removes a requirement that is often tough to comply without complicated circuitry [1].

# 1.2.2 DIGITAL CALIBRATION

Another attractive feature of the circuit is that its calibration is expected to be completed entirely in the digital domain which is a favorable feature because it allows for the chip to be smaller, due to the reduced complexity in the analog domain and the high digital densities that can be attained in CMOS processes. Because of this relaxation of the analog specifications, laser trimmed resistors, burnable fuses or other components needed to manually calibrate the IC can be omitted. An example of when this feature is useful, is an application where several ADCs are needed to be run simultaneously and are connected to a central processor.

The digital calibration will be done by a field-programmable gate array (FPGA) via an algorithm created specifically for this ADC. The scope of this thesis includes the integrated circuit design, layout and extracted simulation of this cyclic ADC and the digital algorithm was created simultaneously by Hattief Spetla, a graduate research student at New England Center for Analog and Mixed Signal Design (NECAMSID) at Worcester Polytechnic Institute. Hattie's thesis (1) includes details of the algorithm's functionality.

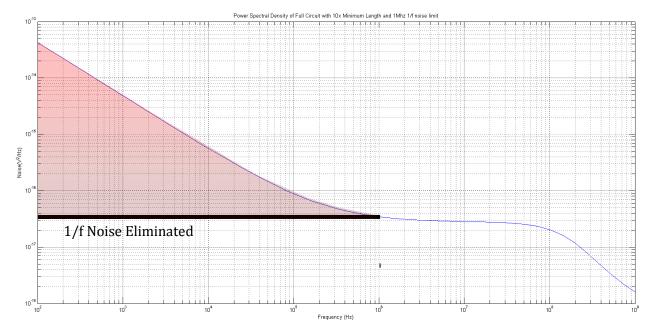

# 1.2.3 SIMPLICITY AND INNOVATION

Cyclic ADCs have a few advantages when compared to other types of converters – the first being that it generally involves less complex circuitry as a consequence of the digital calibration algorithm and the lack of a strictly linear differential amplifier. More importantly, in the realm of analog-to-digital converters, cyclic ADCs have not been used as often as others, leaving more room for innovation and significant contributions to the field.

The purpose of this document is to provide detailed understanding of the design of the Cyclic ADC and its components.

# 2 PREFACE

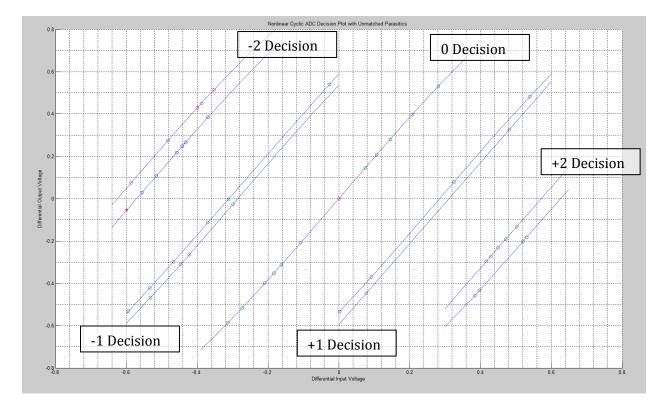

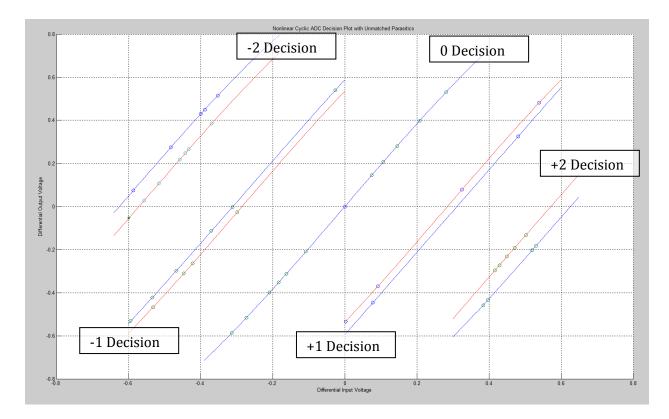

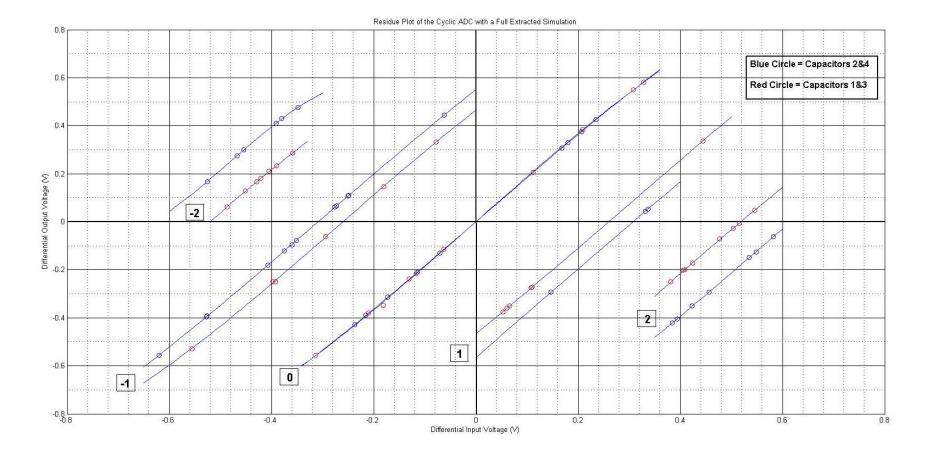

This thesis is a continuation of my Major Qualifying Project (MQP), A Non-Linear Cyclic Analog-to-Digital Converter (1). In this MQP I worked in a group with two other students to create the fundamental building blocks of this converter. Design blocks that were completed in the MQP include the residue amplifier, switched capacitor network, and the comparators. The first goal of this thesis was to modify the timing of all the individual blocks previously created to enable them to work together creating a successful simulation of a conversion. Once completed, the residue plot (input output characteristic) was created and analyzed to verify functionality of the design. After verification, the layout of each ADC design block was designed and tested for functionality. Next, a full extracted simulation was completed to ensure all the blocks function together properly and a final residue plot was made to prove functionality of the ADC.

Parts of this report have been taken from my Major Qualifying Project (1) and I would like to extend a special thanks to my undergraduate capstone project partners Alvaro Soares and Gentin Rrudho for all their hard work and late nights spent working on our MQP. I would also like to thank Professor John McNeill for his insight, guidance and his specific questions designed to challenge my understanding of the material and reinforce my confidence throughout both my MQP and Thesis. I also want to thank my thesis committee members Professor Stephen J. Bitar and Professor Andrew G. Klein for their insight and input and my colleagues, Chris David, Cody Brenneman and Tsai Chen for all their help with Cadence's ICFB.

# 3 BACKGROUND

The purpose of this section is to provide the reader enough background information to make design choices and configurations easier to understand. The materials and fields of study obtained and the design principles and theories shall all be introduced in this section.

# 3.1 ANALOG-TO-DIGITAL CONVERTERS

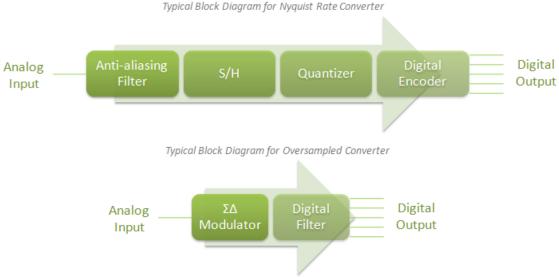

Analog-to-digital converters are devices used to transfer continuous real-world signals into the discrete digital domain. The use of these converters is advantageous to society because they allow signals present in nature to be represented digitally. Since the ultimate goal of this project is to create an analog-to-digital converter (ADC), the different types of ADC's must be defined. A common way to categorize these ADCs relates to the sampling frequency of the converter. The two most commonly used ADC types are Oversampling converters and Nyquist converters.

# 3.2 ADC PERFORMANCE METRICS

Before characteristics and features of integrated circuits and ADCs can be discussed, key terminology and performance metrics must be defined to develop specifications for such circuits. This section will define and briefly explain some important metrics and terms used in ADC design (definitions provided by (2), (3), (4), (5), and (6)).

# Acquisition time (t<sub>acq</sub>)

Acquisition time is the time during the sample stage in a sample-and-hold circuit output to experience a full-scale transition and settle within a specified percentage of its final value.

# **Dynamic Range**

Dynamic Range is the ratio of the maximum allowable input swing to the minimum input level that can be sampled with a specified level of accuracy.

# Spurious-Free Dynamic Range (SFDR)

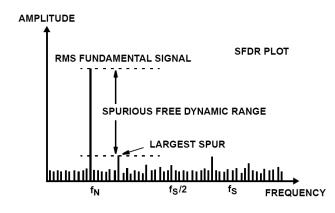

Sometimes referred to as a measurement of fidelity for circuits, the SFDR is the ratio of the RMS value of the peak signal amplitude to the RMS value of the amplitude of the peak spurious spectral component, over the specified bandwidth.

Figure 1 - Spurious-Free Dynamic Range Illustration (7)

#### **Effective Number of Bits (ENOB)**

It is a measure of the true dynamic performance level of a data converter. ENOB is calculated from the measured SNR based on the equation (2):

$$ENOB = \frac{(SNR + Distortion) - 1.76 + 20 \log \left[\frac{Full Scale Amplitude}{Actual Input Amplitude}\right]}{6.02}$$

Eq. 1

#### Signal-to-Noise Ratio (SNR)

The ratio of the signal power to the noise power at the output is known as SNR. Mathematically it can be described simply as

$$SNR = \frac{rms \ Signal}{rms \ Noise}$$

Eq. 2

However, SNR has also a relationship with the effective number of bits, shown below:

$$SNR(dB) = 6.02(ENOB) + 1.76$$

Eq. 3

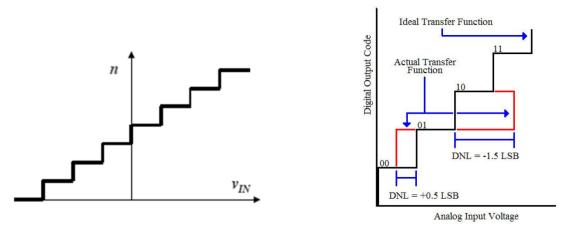

#### **Differential Non-Linearity (DNL)**

The difference between the actual step and the ideal step length of the ADC's output is known as differential non-linearity (4). For an ADC, DNL is the measure of variation in the digital output code, normalized to full scale, associated with a 1 least significant bit (LSB) change in the input code (2).

Figure 2 - Ideal (left) and Non-Ideal (right) Examples of ADC Transfer Function (4)

A change resulting in an error greater than 1 LSB results in lost bits.

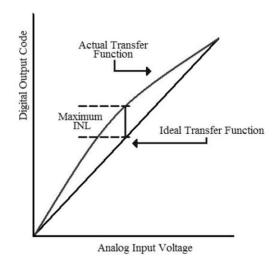

#### Integral Non-Linearity (INL)

Differently from DNL, the integral non-linearity relates to the maximum difference between the converter's output from its ideal value. The ideal value can be described as a theoretical straight line drawn from minus full scale to positive full scale (2). The figure below shows a graphical representation of this concept:

Figure 3 - Integral Non-Linearity Example (4)

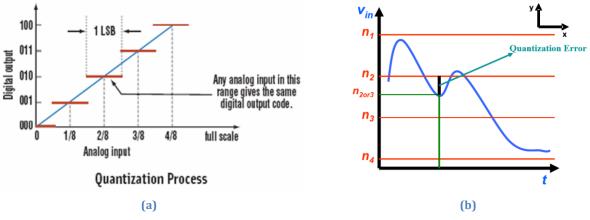

#### **Quantization Error**

When a conversion is made, the analog voltage is quantized to a finite number of discrete values. The error associated with this process is known as quantization error.

Figure 4 - (a) Quantization Process (8) and (b) Quantization Error Illustrations (right) (4)

As Figure 4 shows, an analog input is quantized to a digital value. However, as Figure 4 indicates, there is always a margin where the input value falls between two quantization levels, giving the ADC its quantization error. Reducing this margin correlates to an increase in the ADCs resolution.

#### **Total Harmonic Distortion**

The concept of total harmonic distortion (THD) is a method to characterize the nonlinearity of systems where the spectral power is present in the fundamental frequency as well as its harmonics. This presence of power in other frequencies other than the original, fundamental frequency contributes to THD. In general, total harmonic distortion is defined as the ratio of the power of all harmonics generated the power of the original signal pure sin wave (5). Mathematically it is mainly expressed in units of dB by the following relationship (9),

$$THD = 10\log\left(\frac{V_{h2}^2 + V_{h3}^2 + V_{h4}^2 + \cdots}{V_f^2}\right)$$

Eq. 4

where  $V_{hn}$  is the voltage corresponding to the n-th harmonic of the signal and  $V_f$  is the fundamental's voltage.

THD can also be represented as a percentage,

$$THD = \frac{\sqrt{V_{h2}^2 + V_{h3}^2 + V_{h4}^2 + \dots}}{V_f} \times 100$$

Eq. 5

Total harmonic distortion is especially important in ADCs when building the input and sampling blocks, as this report will further detail in its design section.

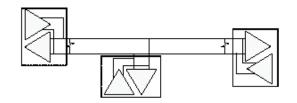

## 3.3 OVERSAMPLING CONVERTERS

As mentioned in Section 3.1, one of the major types of converters is the oversampling ADC, which exists in many variations. Oversampling ADCs are characterized as such due to having their sampling frequency being much greater than twice the bandwidth of the signal, i.e.  $f_n > 2 \cdot (Bandwidth_{signal})$ . These types of circuits are implemented when attempting to obtain very high accuracy. This precision is possible because the complex and precise analog circuitry is substituted by the oversampling ADC's use of digital signal processing techniques. The sacrifice that is made in this case is the throughput that can be achieved (3).

One of the advantages of oversampled ADCs is that aliasing is much less of a concern, in comparison with Nyquist ADCs (3). That is because the signal's frequency spectrum has frequencies much more widely spaced, since the sampling rate is much greater than the signal's bandwidth. A disadvantage of oversampling converters is that a large amount of samples are require to perform a conversion to a desired accuracy, versus the Nyquist ADCs, in which every conversion yields an individual result.

Oversampled ADCs are a good option for converters where the signal is band limited, like music systems, etc. Since this project is not an oversampling converter, these types of ADC's will not be explored further.

16

Figure 5 - Block Diagrams for Nyquist and Oversampled ADCs

# 3.4 NYQUIST CONVERTERS

A Nyquist ADC is a type of ADC that can resolve signals with frequencies up to  $\frac{1}{2}$  the sampling frequency of the converter. This is the sampling rate adequate for recovering the original signal according to the Nyquist theorem, i.e.  $f_n = 2 \cdot (Bandwidth_{ADC})$ , where  $f_n$  is the sampling frequency of the converter. There are several types of Nyquist ADCs in the analog design world. Johns and Martin (9) compares the present ADC types with their common uses in terms of speed and accuracy, shown below:

| Low-to-Medium Speed,<br>High Accuracy | Medium Speed,<br>Medium Accuracy | High Speed,<br>Low-to-Medium Accuracy |  |

|---------------------------------------|----------------------------------|---------------------------------------|--|

|                                       |                                  | Flash                                 |  |

| Integrating                           | Successive Approximation         | Two-Step                              |  |

|                                       |                                  | Interpolating                         |  |

|                                       |                                  | Folding                               |  |

| Oversampling                          | Cyclic                           | Pipelined                             |  |

|                                       |                                  | Time-Interleaved                      |  |

Table 2 - Speed and Accuracy Correlation with ADCs

In the background portion of this paper, three types of converters that have been recently used in the NECAMSID Lab will be explored: Pipelined, Successive Approximation, and Cyclic.

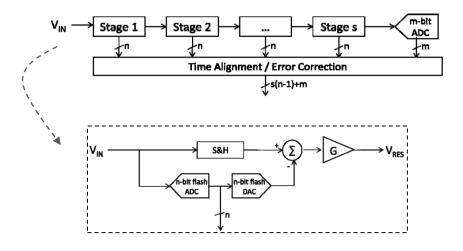

#### 3.4.1 PIPELINED ADCS

A common ADC structure, the pipeline converter receives its name from its multistage nature.

Figure 6 - Block Diagram of a 16-bit Pipelined ADC (8)

As Figure 8 shows, the analog input voltage  $V_{IN}$  is sampled and enters the ADC. Each stage of the converter is responsible for the quantization of a range of bits. Once a stage is completed, its output residue voltage of becomes the next block's input. A final block, containing an n-bit ADC resolves the less significant bits of the converter. Finally a digital block receives each block's output and corrects for time and errors. The final decision is then composed.

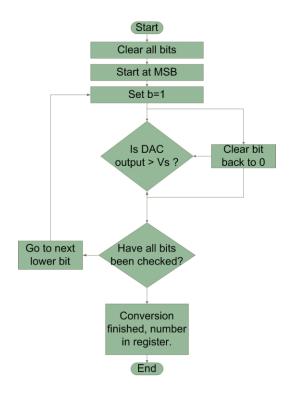

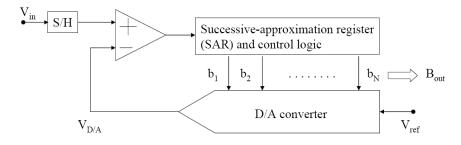

#### 3.4.2 SUCCESSIVE APPROXIMATION ADCS

Successive-approximation ADCs are one of the most popular techniques for analog-to-digital conversion since they are fairly quick in terms of conversion time, while having moderate circuit complexity. There are several configurations that would qualify as successive-approximation converters. For brevity of this report, the successive-approximation converter concept and a few variations will be discussed in detail. For more complete descriptions of different types of successive-approximation ADCs refer to (9).

Some authors recommend that the reader compare the functionality of a basic successiveapproximation converter as a "binary search" algorithm (9). An interesting way to think about this algorithm is to imagine a book with 256 pages, in which you have to guess the page number containing a specific event in the novel. However, you are only allowed to ask "yes/no" questions. Therefore, using the binary search algorithm, one would try to approximate the number by first asking the owner of the book if the event occurs on a page number greater than 128. If the answer is no, then the next question would then address if the event occurs on a page number greater than 64. If so, then the remaining page range would then be divided by two and the same process would be repeated. A flow chart presented by (10) is shown below:

Figure 7 - Flow Chart of Successive-Approximation Approach

The successive-approximation approach is similar to the anecdote above. The ADC works by successively determining the bits of the output starting from the most significant bit (MSB) and then checking the next bits. However, this method is very primitive for the world class types of ADCs found today. Therefore, many improvements to that concept have been added, such as a digital-to-analog converter (DAC) based approximation, using a block known as the Successive-Approximation Register (SAR). A simple diagram of this functionality is shown below:

Figure 8 - DAC-based Successive-Approximation Converter (9)

In this case, a sample-and-hold block is usually needed so that the value being converted remains constant through the conversion. The SAR is entirely digital and the DAC's specifications will mostly determine the speed and accuracy of the converter.

# 3.4.2.1 Charge Redistribution ADC

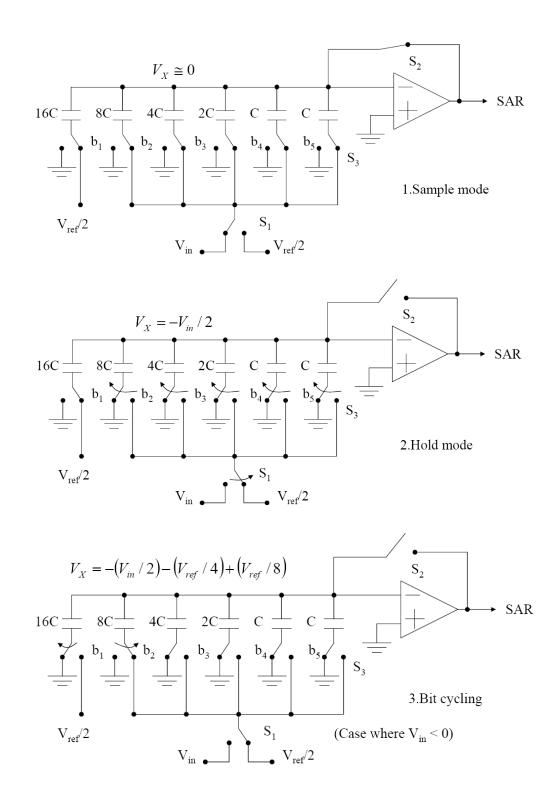

Shown in Figure 9 is an example of a charge-redistribution ADC (9). In this case, an array of capacitors is used. Its advantage is that the sample and hold, DAC, and comparator blocks are all combined into one block. The following chart explains the operation of Figure 9:

| Operation<br>Mode | Description                                                                                                                                                                                                                                |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample            | <ul> <li>All but the largest capacitor are charged to input voltage V<sub>in</sub> while comparator is being reset.</li> <li>The largest capacitor is set to V<sub>ref</sub>/2</li> </ul>                                                  |

| Hold              | <ul> <li>Comparator is taken off reset mode.</li> <li>Capacitors are switched to ground, with the exception of largest capacitor, causing voltage on negative terminal of comparator V<sub>x</sub> to become -V<sub>in</sub>/2.</li> </ul> |

| Bit Cycling       | <ul> <li>If V<sub>in</sub> is negative, the largest capacitor is switched to ground.</li> <li>If V<sub>in</sub> is positive, the largest capacitor is remains at V<sub>ref</sub>/2.</li> </ul>                                             |

#### Table 3 - Charge-Redistribution (Figure 9) ADC Explanation

Johns and Martin (9) catalogue other more complex types of SAR ADCs, which include calibration and error correction blocks.

Figure 9 – 5-bit Charge-Redistribution ADC (9)

#### 3.4.3 THE CYCLIC ADC

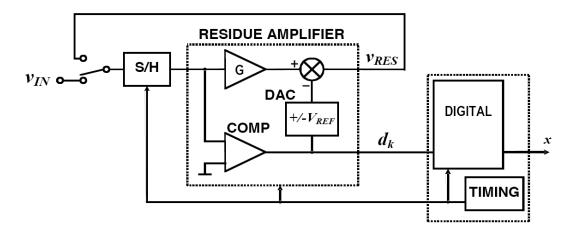

A Cyclic converter, also known as an Algorithmic converter, is similar in operation to the successive approximation converter. However, in the case of the Cyclic ADC, the reference voltage is not altered. Instead, the error (or residue) of the amplifier is doubled (9).

Figure 10 – High Level Block Diagram of a Cyclic Converter (11)

As the block diagram above outlines, the operation of the cyclic converter functions in the following manner: First, the input voltage is sampled by the sample-and-hold block. That value is then compared to a threshold voltage, upon which a digital decision is made, determining a bit value in the final sequence of the number sampled. A reference voltage is generated by a 1-bit digital-to-analog converter which is dictated by the digital decision previously made. At the same time, the input value is amplified by a factor two (ideally). The amplified value is then summed to a reference voltage +/- V<sub>REF</sub>, leaving a residue voltage. The residue voltage then becomes the input of the residue amplifier. This cycle is repeated enough times required to achieve the desired resolution, earning the device its name. The sequence of decisions corresponds to the output value of the ADC.

#### 3.4.3.1 Understanding the Residue Amplifier

A major part of the cyclic ADC is the residue amplifier. Therefore, in order to better comprehend the operation of the ADC, a mathematical approach can be taken to explain this concept (11). The equation below shows the relationship between the residue amplifier's input and output:

$$v_{res_{out}} = G \cdot v_{res_{in}} - d \cdot V_{ref}$$

Eq. 6

where *G* is the gain of the amplifier and *d* is the digital decision.

Assuming ideal conditions, after performing N cycles, the amplifier exhibits the following negative feedback loop relationship:

$$v_{res_{out}(N)} = [G^N \cdot v_{res_{in}}] - [G^{N-1}d_1 + G^{N-2}d_2 + \dots + G^0d_N] \cdot V_{ref}$$

Eq. 7

The output code of the ADC can be predicted by rearranging Eq. 7 into the following form (11):

$$\frac{\nu_{res_{in}}}{V_{ref}} = \left[\frac{1}{G}d_1 + \frac{1}{G^{N-1}}d_2 + \dots + \frac{1}{G^N}d_N\right] - \left[\frac{1}{G^N}\frac{\nu_{res_{out}}(N)}{V_{ref}}\right]$$

Eq. 8

The  $\left[\frac{1}{G^N} \frac{v_{res_{out}(N)}}{v_{ref}}\right]$  term of the equation can be redefined as the quantization error, and the first term as the output code x:

$$x = \left(\frac{1}{G}\right) d_1 + \left(\frac{1}{G}\right)^2 d_2 + \dots + \left(\frac{1}{G}\right)^N d_N$$

Eq. 9

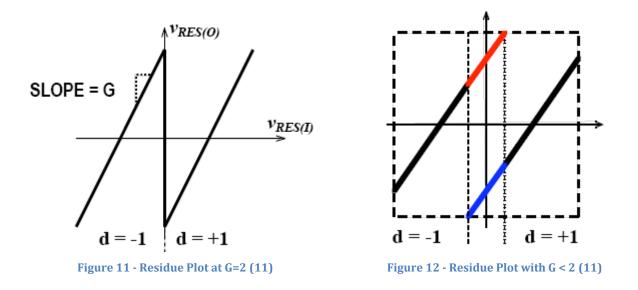

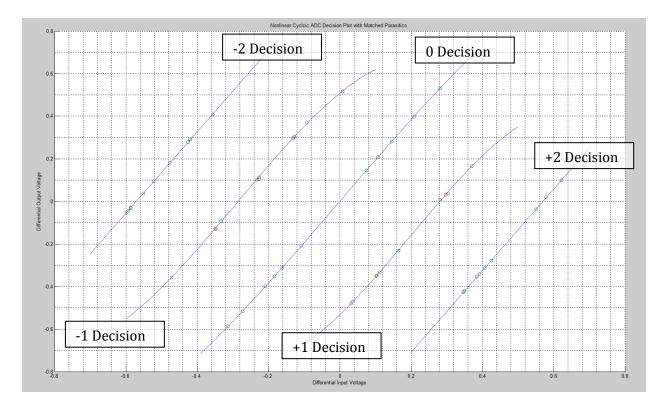

A plot relating the residue amplifier's input and output can be created, as shown below:

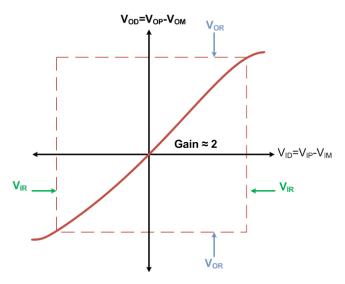

However, maintaining a constant gain of 2 may be challenging. Therefore, when G < 2, the residue plot would look like Figure 12. This event makes it possible for two possible decisions for the same input value, adding redundancy to the ADC. However, at the same time, it adds a level of complexity to the calibration of the converter, which will be discussed in a further section of the document.

## 3.5 THE ROLE OF CAPACITORS

As the previous section has outlined, the used of capacitors for ADCs is very common. As the design sections of this paper will indicate, this ADC relies heavily on the use of multiple capacitors that will be switched constantly to perform the cyclic function of the ADC. Therefore an understanding of how the capacitors will affect this circuit and what constraints there are when choosing the correct capacitors for our circuit is crucial.

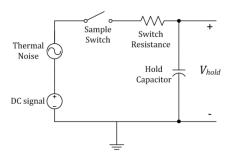

#### 3.5.1 THERMAL NOISE

Thermal noise is inherent to all electronic circuits and it is caused by a random motion of electrons in a conductor. It is a function of temperature and is constant over all frequencies. When designing an analog to digital converter, this noise must be accounted for in the design of the sampling capacitors in the sample-and-hold amplifier (SHA) in order to achieve a desirable signal-to-noise ratio. Since the SNR is the integral of all the noise in a system, the lower the noise bandwidth, the less noise is sampled by the ADC. Figure 13 below shows a model of a sample and hold switch with a dc input and a thermal noise.

Figure 13- Diagram of Hold capacitor with Thermal Noise

When the sample switch is opened, the voltage on the capacitor is the DC signal plus the thermal noise at the instant the switch is opened. Since the characteristic of the sample and hold circuit is a low pass filter, the noise above the corner frequency of this low pass filter is attenuated. In order to reduce the bandwidth of the noise the hold capacitor must be sized according to the SNR needed.

The equation below shows the relationship of capacitance and temperature to the RMS noise of a system, which is the ratio of capacitor size to the total thermal noise power of the RC circuit.

$$RMS \ noise = \sqrt{\frac{KT}{C}}$$

Eq. 10

# 3.6 OPTIONS FOR OUTPUT DRIVING

Every analog-to-digital converter has to interact with an off-chip digital domain, usually an FPGA or a computer. Although sometimes designers may choose additional output drivers in their circuit at the expense of simplicity, there are methods used to improve output performance. In this case, various methods were researched. One particular method, known as Low Voltage Differential Signaling (LVDS), showed itself to be a promising option for the circuit. Section 3.6 outlines the existing configurations and applications of LVDS.

## 3.6.1 UNDERSTANDING LVDS

Usually used for output blocks of ADCs, Low-Voltage Differential Signaling is a technology that was officially introduced in 1994 by National Semiconductor. It was born out of the necessity to create high performance solutions that consume little power and are susceptible to less noise than the common techniques of the time, while being cost-effective, such as RS-442 and RS-485 standards. A competing technology was Emitter Coupled Logic (ECL). However, it is incompatible with standard logic levels, uses negative power rails, and leads to high chip-power dissipation (12).

| Parameter            | RS-422                      | RS-485                                    | ECL                                       | LVDS                        | M-LVDS                                    |

|----------------------|-----------------------------|-------------------------------------------|-------------------------------------------|-----------------------------|-------------------------------------------|

| Bus                  | Point-to-Point<br>Multidrop | Point-to-Point<br>Multidrop<br>Multipoint | Point-to-Point<br>Multidrop<br>Multipoint | Point-to-Point<br>Multidrop | Point-to-Point<br>Multidrop<br>Multipoint |

| Termination          | 100 Ω                       | 50-60 Ω                                   | depends                                   | 100 Ω                       | 50 Ω                                      |

| Signal Swing         | 2 V min                     | 1.5 V min                                 | 0.8 – 1 V                                 | 250-450 mV                  | 480-680 mV                                |

| Threshold            | +/-200 mV                   | +/-200 mV                                 | +/-200 mV                                 | +/-100 mV                   | +/-50 mV                                  |

| Common<br>Mode Range | +/-7 V                      | -7 to +10 V                               | depends                                   | +/-1 V                      | +/-2 V                                    |

| Standard             | TIA/EIA-422-B               | TIA/EIA-485-A                             | none                                      | TIA/EIA-644-A               | TIA/EIA-899                               |

| Power                | moderate                    | moderate                                  | high                                      | very low                    | low                                       |

| Speed                | < 10 Mbps                   | < 10 Mbps                                 | < 2 Gbps                                  | < 2 Gbps                    | < 500 Mbps                                |

#### Table 4 - Comparison Table of Differential Standards

# 3.6.2 The Concepts behind LVDS

LVDS, as the name suggests, is differential – meaning that it makes use of two signals to function. At the cost of using an extra trace, space, and power, noise is considerably reduced through commonmode rejection. As a consequence, many improvements can be made to the design, such as:

- Signal swing can be dropped to only a few hundred millivolts due to signal-to-noise rejection improvement

- Rise time is shorter, resulting in faster data rates

- Very low power consumption across a wide range of frequencies due to low swing and current-mode driver outputs

- Digital crosstalk onto analog circuitry is reduced

# 3.6.3 DIFFERENT TYPES OF LVDS

The table below shows the different variations of LVDS found in the market today:

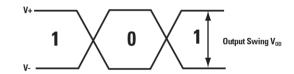

|        | Industry Standard | Maximum Data Rate | Output Swing (V <sub>OD</sub> ) | Power Consumption |

|--------|-------------------|-------------------|---------------------------------|-------------------|

| LVDS   | TIA/EIA-644       | 3.125 Gbps        | ± 350 mV                        | Low               |

| LVPECL | N/A               | 10+ Gbps          | ± 800 mV                        | Medium to High    |

| CML    | N/A               | 10+ Gbps          | ± 800 mV                        | Medium            |

| M-LVDS | TIA/EIA-899       | 250 Mbps          | ± 550 mV                        | Low               |

| B-LVDS | N/A               | 800 Mbps          | ± 550 mV                        | Low               |

#### Table 5 - Industry Standards for Various LVDS Technologies (13)

While the concept of LVDS is the foundation of the standards found in the table above, there are various applications for each one. Power consumption, performance, and target application are among the differences listed above. For brevity, we will analyze the typical LVDS standard and how it applies to this project. If applicable, the other technologies may be explored.

#### **Different Configurations of LVDS**

There are three common Bus types of LVDS configurations. They are:

- Point-to-Point

- Multidrop

- Multipoint

# 3.6.3.1 Point-to-Point

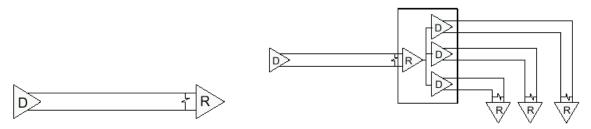

Being the simplest configuration, Point-to-Point offers a direct path from the transmitter to the receiver. This is favorable for use in the highest data rates, due to the simple path. A variation of this configuration can be seen in Figure 15. All figures in this section are extracted from (12).

Figure 14 - Point-to-Point Configuration Figure 15 - Data Distribution Using Point-to-Point Configuration

### 3.6.3.2 Multidrop

Multidrop is most efficient when various parts of a circuit need to receive the same information. There is one driver and two or more receivers along the bus, as the figure below illustrates:

**Figure 16 - Multidrop Configuration**

#### 3.6.3.3 Multipoint

A multipoint configuration uses various drivers and receivers. The advantage to this circuit is that it can send information from multiple areas of the circuit, if necessary. However, this configuration can get quite complex and speeds are generally lower than the other simpler configurations.

Figure 17 - Example of a Three-Node Multipoint Configuration

# 3.6.4 CONTRASTING LVDS TYPES AND CONFIGURATIONS

The article released by National Semiconductor entitled "The Many Flavors of LVDS" (12) summarizes the available technologies with the configurations used by them. This matrix is shown below:

| Bus Configuration | LVDS | BLVDS | M-LVDS | GLVDS | LVDM |

|-------------------|------|-------|--------|-------|------|

| Point-to-Point    | *    | ★     | *      | ×     | *    |

| Multidrop         | *    | ★     | *      |       | X    |

| Multipoint        |      | ★     | *      |       | ×    |

| Multipoint        |      | ★     | *      |       |      |

| (Backplane)       |      |       |        |       |      |

<sup>\* =</sup> full support

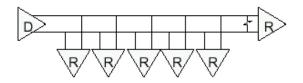

# 3.6.5 A TYPICAL LVDS CIRCUIT

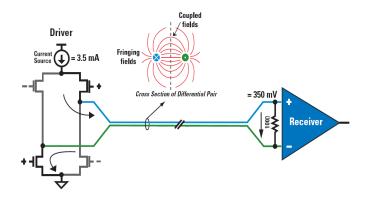

The following picture illustrates a high-level configuration for a LVDS circuit. Notice the detail showing the reduction in interference due to the interaction in electric fields between the wires, which are usually placed as a twisted pair.

Figure 18 - LVDS Driver and Receiver (13)

In the driver-receiver configuration shown in Figure 18, a 3.5mA current source is found in the driver. Due to the high impedance "op-amp characteristic" of the receiver, all of the current flows through the 350mV resistor in place. When the driver makes a switch, the current changes direction of flow across the resistor and results in a logic state "one" or "zero." Figure 19 illustrates this concept.

**Figure 19 - Digital Signaling Model**

# 3.6.6 APPLICATIONS

There are various applications for LVDS. As previously mentioned, the advantages presented by LVDS make it a popular technology. Listed below are three common applications of LVDS within integrated circuits.

- Line drivers/receivers Commonly used to convert single-ended signals into formats for transmission over a cable or backplane.

- **SerDes** Serializer/deserializer pairs are used to multiplex a number of low-speed CMOS lines and to transmit them as a single channel running at a higher data rate.

- **Switches** Used instead of bus architectures for high data rates. Commonly used for clock distribution. LVDS is one of the most suitable signaling standards for clocks of any frequency because of reliable signal integrity.

# 3.6.7 Assessing LVDS in the ADC Design Process

There are various factors to consider when choosing a signaling standard, such as:

- Required bandwidth

- Ability to drive cables, backplanes, or long traces

- Power budget

- Network topology (point-to-point, multidrop, multipoint)

- Serialized or parallel data transport

- Clock or data distribution

- Compliance to industry standards

- Need or availability of signal conditioning

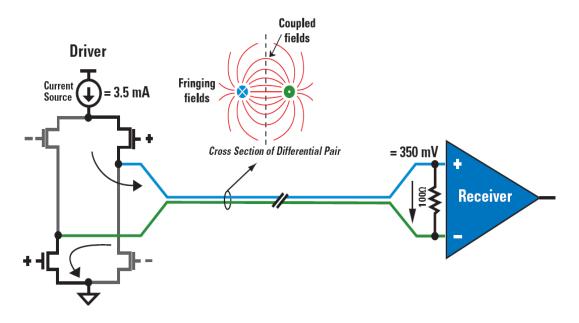

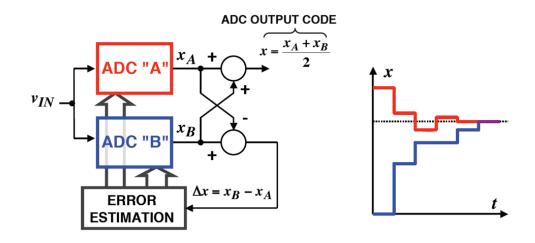

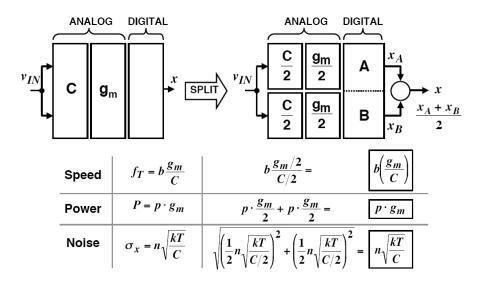

### 3.7 THE SPLIT-ADC CONCEPT

One of the key characteristics in this project is the Split-ADC architecture. The figure below illustrates the basic principle of the split-ADC. Instead of using one converter, the chip will have two ADCs performing the same steps over the same input. The output then becomes the average of both results. The difference of each ADC's output is then sent to the error estimation block, which is located off chip, in the digital realm (14).

Figure 20 - Illustration of Split-ADC Concept (11)

Ideally, the concept behind the split-ADC architecture is simple to comprehend: when the difference between outputs  $x_A$  and  $x_B$  is zero, the calibration has occurred. This concept is important because it will reduce the circuit's calibration time significantly, as explained in (11). The following graph contrasts the single ADC approach versus a split architecture.

Figure 21 - Split ADC Characteristics in Contrast with Single ADC Approach

As Figure 21 shows, the trade off in complexity is small compared to the advantages in calibration. At the same time, the general speed, power and noise of circuit remains the same. This is because the same parts are used but in proportions of one half the original size.

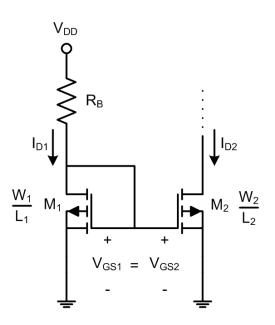

### 3.8 THE CURRENT MIRROR

Biasing is very important to this project, making the necessity to build current sources imminent. One of the most common forms of creating a current source is by using a MOSFET current mirror. The current mirror relies on the assumption that transistors are closely matched, meaning that they are fabricated under the same conditions, matching closely the values of the transistors' threshold voltages, mobility, and oxide capacitance. Therefore, since this level of matching and precision can only be achieved in integrated circuits, the current is not commonly realized with discrete components. Figure 22 shows a basic configuration for a current mirror.

Figure 22 - Current Mirror Example

According to the MOSFET Square Law, the current in the transistors can be defined as (3):

$$I_D = \frac{\mu_n C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2$$

Eq. 11

where  $I_D$  is the MOSFET drain current,  $C_{ox}$  is the capacitance of the oxide, W is the width of the transistor, L is the length,  $V_{GS}$  is the gate to source voltage and  $V_{th}$  is the threshold voltage of the transistor. Therefore for the current  $I_{D1}$  in transistor  $M_1$ ,  $V_{GS1}$ , can be solved.

$$V_{GS1} = \sqrt{\frac{2 \cdot I_{D1} \cdot L_1}{\mu_n C_{ox} W_1}} + V_{th1}$$

Eq. 12

As shown in Figure 22, by tying the MOSFET gates together, the following relationship is attained:

$$V_{GS1} = V_{GS2}$$

Using the value for  $V_{GS1}$  into the current of the second transistor:

$$I_{D2} = \frac{\mu_{n2}C_{ox2}}{2} \frac{W_2}{L_2} \left( \sqrt{\frac{2 \cdot I_{D1} \cdot L_1}{\mu_n C_{ox} W_1}} + V_{th1} - V_{th2} \right)^2$$

Assuming the transistors are properly matched, the following assumptions can be made:

$\mu_{n1} = \mu_{n2}$  $C_{ox1} = C_{ox2}$  $V_{th1} = V_{th2}$

Simplifying the results to

$$I_{D2} = I_{D1} \left[ \frac{\left(\frac{W_2}{L_2}\right)}{\left(\frac{W_1}{L_1}\right)} \right]$$

Eq. 13

When comparing the current mirror to an ideal current source, the model falls short in a few aspects. For example, an ideal source has infinite AC impedance, while a MOS mirror has finite impedance. Also, the current mirror will have frequency limitations due to capacitive and inductive parasitics.

#### 3.9 THE DIFFERENTIAL PAIR

The differential pair, sometimes referred to as the differential amplifier, is a vital part of this circuit. According to Sedra and Smith, "the differential pair is the most widely used building block in analog integrated-circuit design." This is because differential amplifiers are less susceptible to noise than their single-ended counterparts and they also allow for biasing of an amplifier without the use of bypass and/or coupling capacitors, saving space on the chip being manufactured (15). As with the current mirror, in integrated circuits, the differential pair relies largely on the ability to match components.

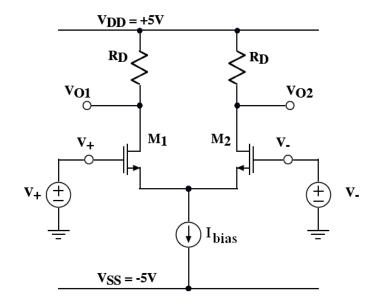

The differential pair can be used in various configurations. In this section two modes of operation will be explored: common-mode and differential gain modes. An example of a differential pair is shown below:

Figure 23 - Differential Amplifier Example (16)

33

The differential pair consists of a symmetrical system of two MOSFETS sharing the same bias current. The parameters in each transistor can be extracted using the square law equation, seen in Eq. 11:

$$I_D = \frac{\mu_n C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{th})^2$$

where the currents at each transistor are equal to  $\frac{I_D}{2}$ .

### 3.9.1 BARTLETT'S BISECTION THEOREM

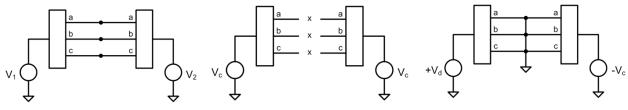

The functionality of the system can be explored using Bartlett's Bisection Theorem, which is based on the symmetry of circuits and explores the fact that any two inputs can be represented in a common mode and a differential mode.

Figure 24 - Amplifier Model

Figure 25 - Common Mode Model

Figure 26 - Differential Mode Model

The common-mode voltage can be defined as:

$$V_c = \frac{V_1 + V_2}{2}$$

Eq. 14

And the differential voltage as:

$$V_d = V_2 - V_1$$

Eq. 15

Using this concept, it can be verified that:

$$V_1 = V_c - \frac{V_d}{2}$$

Eq. 16

and

$$V_2 = V_c + \frac{V_d}{2}$$

Eq. 17

The half circuit of each circuit model for the example in Figure 23 can be represented using the bisection theorem, as shown below:

Figure 27 - Half-Circuit Model of the Common Mode

Figure 28 - Half-Circuit Model of the Differential Mode

35

A graph of the large signal characteristics of the differential pair is shown below:

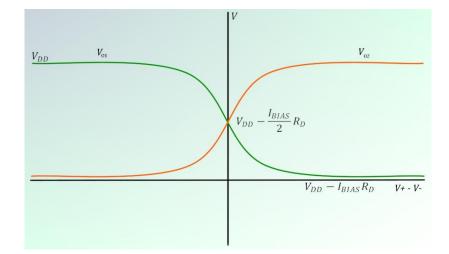

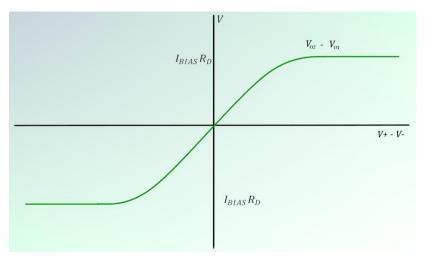

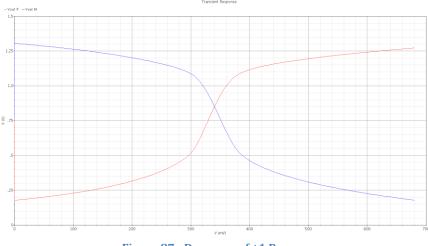

Figure 29 - Signal Input-Output Characteristics of the Differential Input to Each Output

To simplify calculations and circuitry it is common practice to attempt to operate with the linear areas of the curves shown above. As was said in the introduction, the ingenuity of this project is that the non-linearity is not as much of a pertinent issue in this circuit as will be explored in later sections of this document.

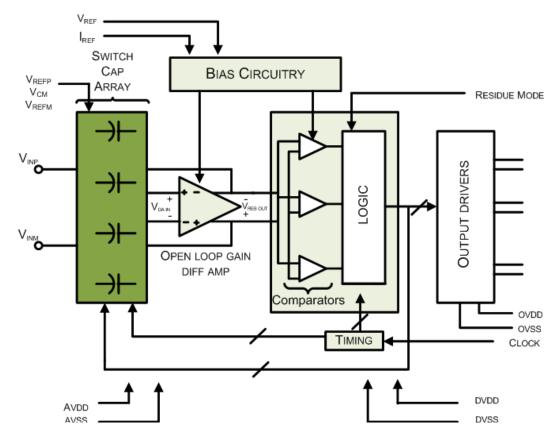

# 4 HIGH-LEVEL DESIGN

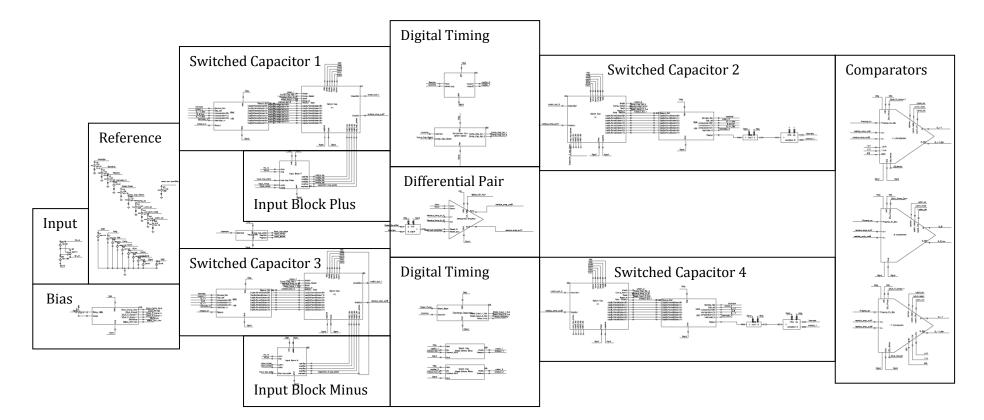

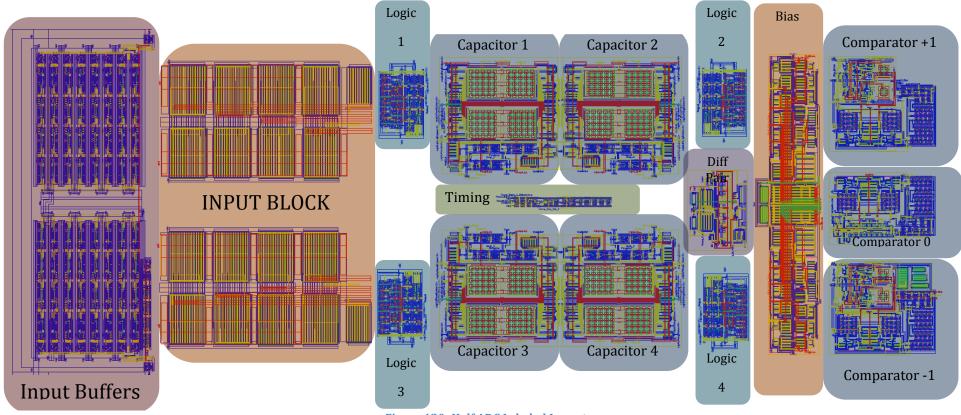

The objective of this section is to give a brief high level overview of the integrated circuit being designed for this project.

## 4.1 BLOCK DIAGRAM

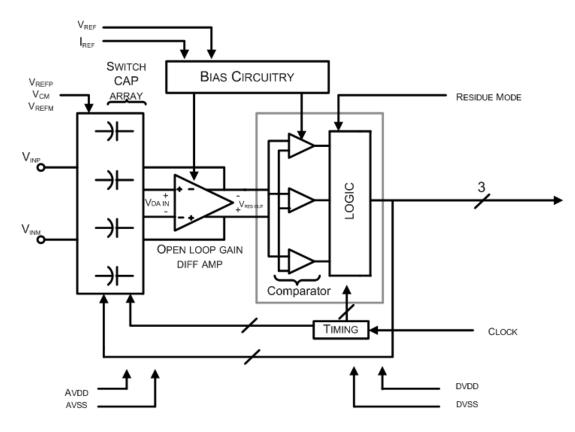

The figure below displays a proposed block diagram for the device. Several sub blocks are displayed in the diagram. This approach gives us a modular idea of the design.

They main blocks found in this design are:

- Switch Capacitor Array

- Open Loop Differential Amplifier

- Bias Circuitry

- Comparator Network

- Logic Sub Block

- Output Drivers

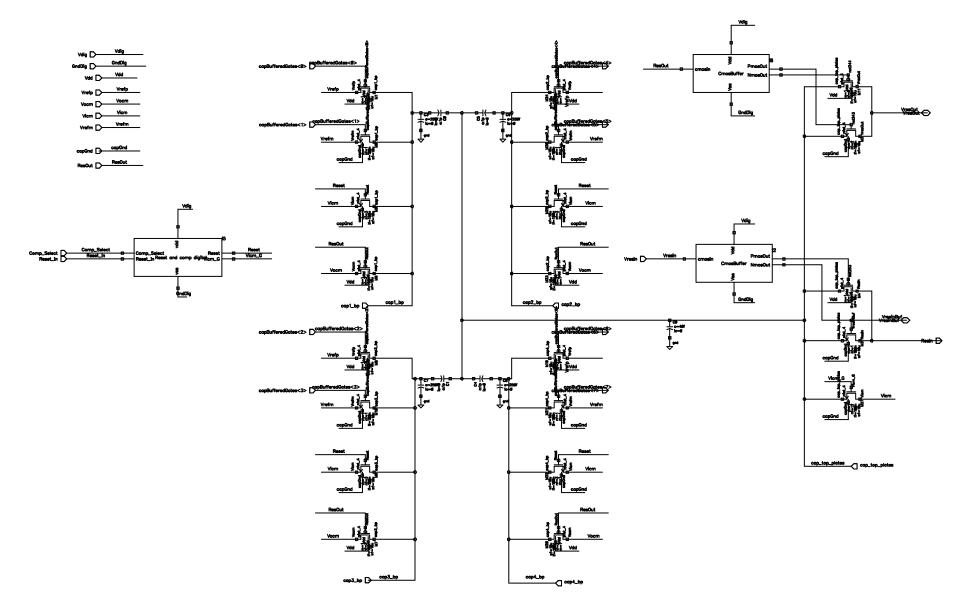

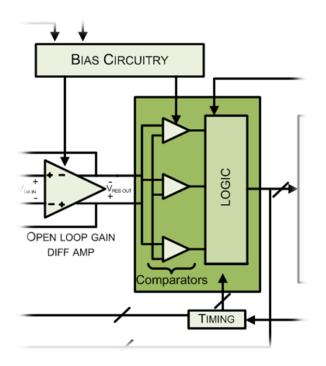

Figure 31 - Block Diagram

37

The next sections of the report will dissect each of the blocks mentioned above and will outline how each portion has been implemented.

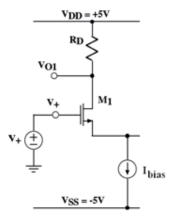

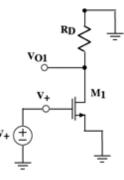

# 5 THE INPUT BLOCK

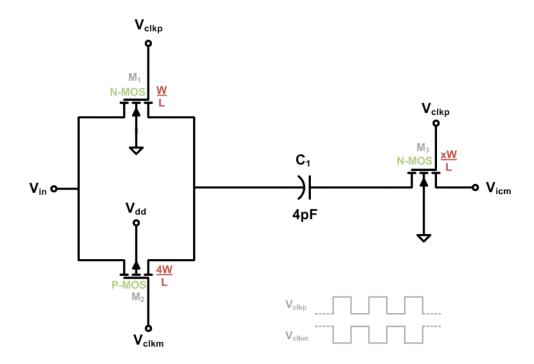

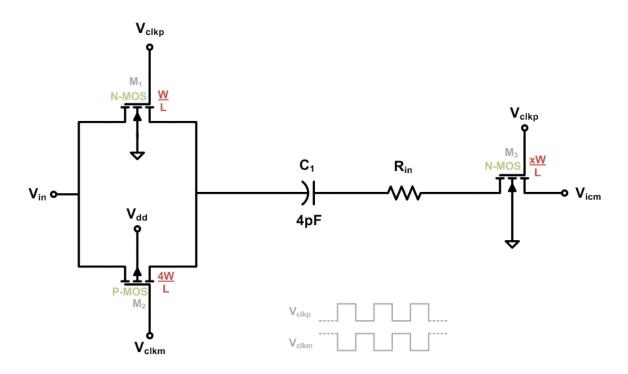

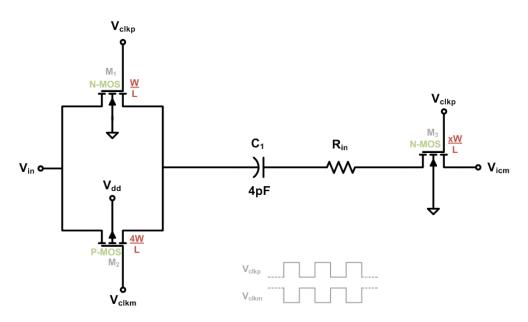

The input of this ADC is composed of a sample-and-hold circuit which is used to obtain the input signal onto the capacitors. This input block can appear quite complex because of the use of multiple capacitors. Therefore, for simplicity a basic concept for the input block is shown below:

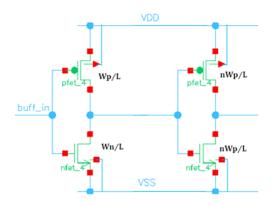

Figure 32 - Schematic of Input Block

As the figure above shows, in this simplified version of the input block, the input voltage  $V_{in}$  is sampled onto capacitor C<sub>1</sub>. It is done so through a CMOS transmission gate, a configuration involving a pair of opposite type MOSFETs. The use of transmission gates eliminates the undesirable threshold voltage effects which give rise to loss of logic levels (3). The capacitor is sampled at every positive of edge of the clock cycle, indicated in this case as V<sub>clkp</sub>, and at every negative edge of its inverted version, V<sub>clkm</sub>, to bias the p-channel transistor.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Note: Biasing for transistor  $M_3$  is simplified. In actual implementation, the gate voltage on  $M_3$  in Figure 32 is delayed slightly to reduce charge injection.

## 5.1 TRANSISTOR SIZE OPTIMIZATION

Transistors in the input block need to be properly sized to accommodate the circuit. This task is more important than it seems. The transistor sizes will help determine and/or improve several factors of the ADC, such as spurious-free dynamic range and total harmonic distortion. Therefore, an optimization exercise was necessary to determine the correct widths of the transistors which would meet the goals for distortion and acquisition time.

#### 5.1.1 DEALING WITH THE PRESENCE OF DISTORTION

One might wonder why distortion is such an important issue to such a simple circuit, like an input block. The key is that distortion is present due to variations on the gate voltage. Below shows the equation for the "on" resistance of the MOSFET:

$$R_{DS_{on}} = \frac{V_{DS}}{I_D} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})}$$

Eq. 18

All of the values in Eq. 18 are mostly constant, with the exception of the voltage from gate to source, which changes due to the varying source voltage due to the input signal. This change in  $V_{GS}$  causes the internal resistance of the transistors to change as well. When the input block is tracking an AC signal such as a sin wave, the on resistance of the MOSFET changes throughout the period of the wave. This change in resistance dynamically changes the phase delay of the circuit creating harmonics. One way to reduce the total harmonic distortion is to increase the size of the MOSFETS in the circuit which reduces the total resistance thus lessening the effect the change in resistance due to input voltage fluctuation has on the input.

#### 5.1.2 Performing a Parametric Analysis

The goal for this analysis was to determine the appropriate input block's transistor widths. From previous design experience, professor McNeill recommended the following assumptions:

- The p-channel (M<sub>2</sub>) transistor will have a width that is 4 times larger than its n-channel MOSFET equivalent

- The n-channel MOSFET (M<sub>3</sub>) on the top plate of the capacitors should have a width proportional (by a factor of *x*), but not necessarily equal, to the n-channel MOSFETs (M<sub>1</sub>) on the bottom plate

This optimization can be thought of as the total area used by the entire input block. Therefore, the total area can be found by determining the total width,  $W_{Total}$ , as a function of M<sub>1</sub>'s width, as shown below:

$$W_{Total} = W_{Q_1} + W_{Q_2} + W_{Q_3} = W + 4W + xW$$

Eq. 19

$W_{Total} = (5 + x) \cdot W$

Rearranging,

$$W = \frac{W_{Total}}{(5+x)}$$

Eq. 20

As a result, a series of graphs were created where the values for *x*, *W*, and  $W_{Total}$  were swept, to find the smallest transistors that would fit the parameters. The two main characteristics that relate to these values are acquisition time and total harmonic distortion. To deliver values for those attributes, several parametric analyses have been completed in ICFB. The following table indicates the values that were simulated:

#### **Table 7 - Swept Attributes**

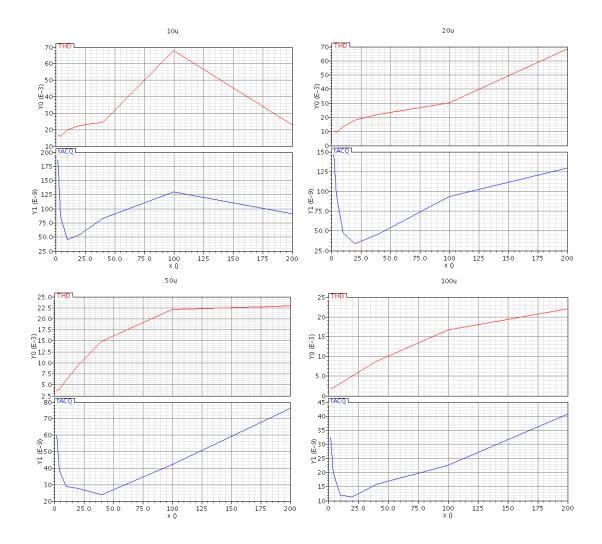

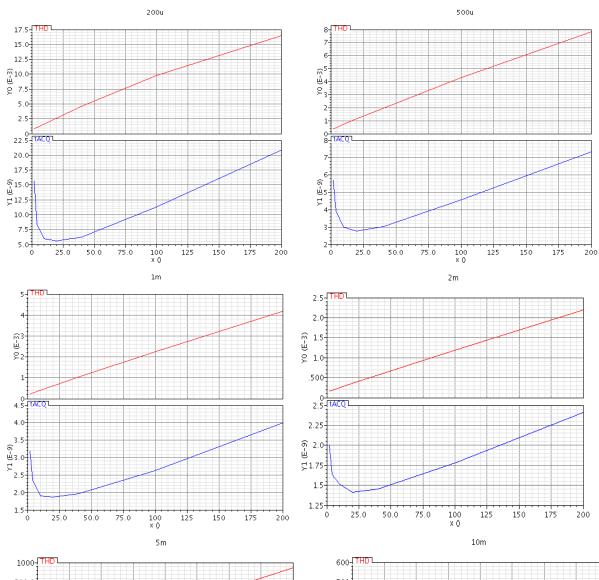

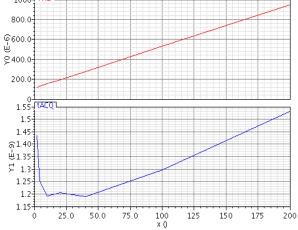

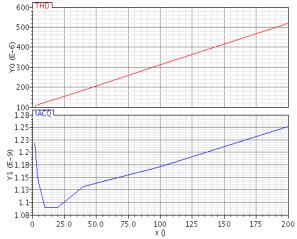

The title of each graph indicates the values used for  $W_{Total}$ . On the y-axis, the red lines indicate THD and the blue lines indicate acquisition time. The x-axis indicates the value of x.

*Note: The values of x are scaled by a factor of 20, in order to accommodate simulation criteria in Cadence.*

The results are summarized in the table below:

| W <sub>Total</sub><br>[μm] | x    | t <sub>ACQ</sub><br>[ns] | THD<br>[%] |

|----------------------------|------|--------------------------|------------|

| 10                         | 0.25 | 85                       | 1.8        |

| 20                         | 0.5  | 50                       | 1.0        |

| 50                         | 0.5  | 30                       | 0.6        |

| 100                        | 0.5  | 12                       | 0.3        |

| 200                        | 0.5  | 6                        | 0.15       |

| 500                        | 0.5  | 3                        | 0.06       |

| 1000                       | 0.5  | 1.9                      | 0.035      |

| 2000                       | 0.5  | 1.5                      | 0.025      |

| 5000                       | 0.5  | 1.1                      | 0.016      |

| 10000                      | 0.5  | 1.09                     | 0.012      |

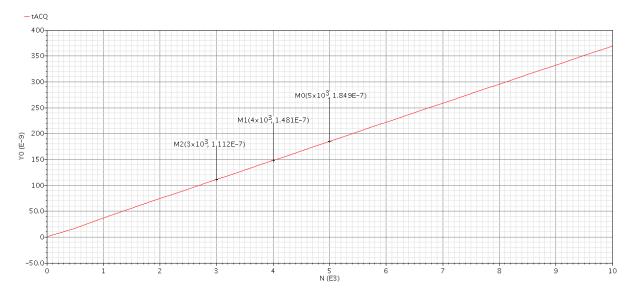

Table 8 - Summarized Optimization Results of tACQ and THD

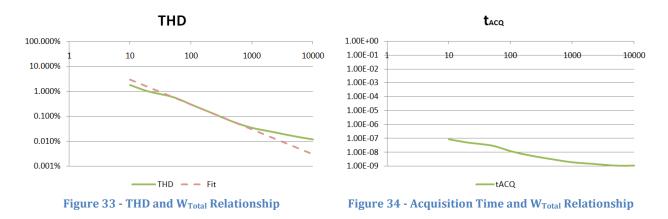

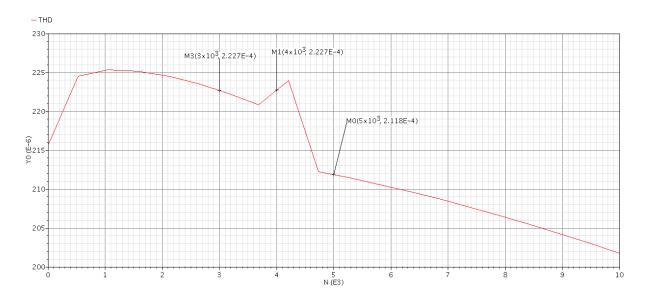

The values chosen were dictated by minimum of THD, which happened at the lower side of acquisition time curve. It can be observed that there is a relationship between the total width of the transistors and the parameters simulated. This relationship is shown below in Figure 33 and Figure 34.

As the figures above indicate, the larger widths will give us better performance. However, the die area must also be accounted for because of the rather large percentage of the final IC the input block uses. This meaning that a compromise will be made. As a result, the next step was to set goals for distortion and acquisition time that will establish the basis for this compromise.

#### **5.1.2.1 Goals for Parameters**

To ensure that the design is competitive, Professor McNeill has indicated that from experience, the level of total harmonic distortion should be less than 0.01%. Once again, the Professor's experience in analog integrated circuit design served as a guide for a harmonic distortion goal. As defined in the introduction of the paper, the ADC will perform one million samples per second, translating into 1 conversion per microsecond. Therefore, twenty percent of this time has been allocated for sampling the input for reasons which will be discussed later. Because of this, the goals for this ADC input parameters are as follows:

#### **Table 9 - Parameter Goals**

| Parameter                        | Goal     |

|----------------------------------|----------|

| <b>Total Harmonic Distortion</b> | < 0.01%  |

| Acquisition Time                 | < 200 ns |

As the graphs show, the acquisition time is not an issue for us, since all measurements met the required goal. The reason for such a loose acquisition time goal will be explained in a further subsection.

#### 5.1.3 CHOOSING TOTAL WIDTH

When looking at the simulation results, the total harmonic distortion levels found were not below the expected mark of 0.01%. The reason for this is inferred to be the limitations of the simulator. The simulations were done under various conditions and yielded different results. However, when looking at Cadence's description of the THD formula, some parameters were not easily editable. As a result, an assumption was made that the total harmonic distortion levels are low enough at a very safe margin at a  $W_{Total}$  value of 5mm.

As stated in Eq. 20, the equation derived gives the parameters for width is:

$$W = \frac{W_{Total}}{(5+x)}$$

Since it has been established that the total width for the input block is 5mm, the total with W from Table 9 is 909um as seen below.

$$W = \frac{5mm}{(5+0.5)}$$

$$W = 909\mu m$$

Summarizing the new transistor widths:

**Table 10 - Values for Transistor Widths**

|            | <b>M</b> 1 | $M_2$   | <b>M</b> 3 |

|------------|------------|---------|------------|

| Expression | W          | 4W      | xW         |

| Value      | 909 µm     | 3.63 mm | 454.5 μm   |

## 5.2 REDUCING THE NOISE FLOOR

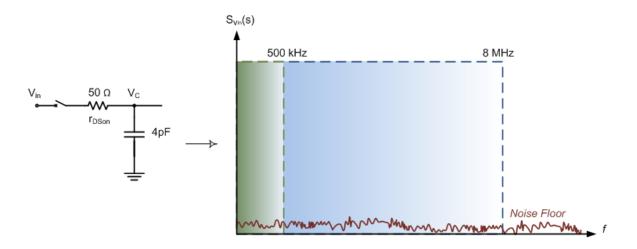

Until this point in the design of the input block, acquisition time has been a specification easily met and one might wonder why so much time has been allotted for the input and not used to increase accuracy of conversion. The reason for which 200ns was allotted for the ADC to sampling is related to spectral noise reduction and SNR. In order words, the internal "on" resistance of the MOSFETs, combined with the input capacitor, create a low pass filter. The lower the "on" resistance of the MOSFET is, the higher the roll off frequency of the filter.

The picture below shows an example of this case.

Figure 35 - Motivation for Noise Floor Reduction

If  $r_{DSon}$  takes on a value of 50  $\Omega$ , the frequency roll off,  $f_h$ , will be found at 8 MHz, or in theory,

$$f_h = \frac{1}{2\pi \cdot RC}$$

Eq. 21

The blue shading indicates the location of the frequency roll-off. However, since the ADC's bandwidth is 500 kHz, the amount of noise aliased into the ADC can be reduced by simply adding a series resistance to the circuit, as shown in Figure 36.

Figure 36 - New Input Circuit Model with Added Resistor

To find the correct value for this resistance, the acquisition time must be taken into account to obtain the precision desired for the ADC. Since this converter should be 16-bit linear, the input accuracy must be within ½ a Least Significant Bit of the ADC, as shown below:

$$t_{allow} = \ln(2^{17}) \cdot \tau \qquad \qquad \text{Eq. 22}$$

where  $\tau$  is the RC circuit's time constant and  $t_{allow}$  is the value pre-determined as the input sampling duration. Restructuring the equation, we'll have:

$$\tau = \frac{t_{allow}}{\ln(2^{17})} \approx \frac{200 \, ns}{12} = 16 \, ns$$

Knowing that  $\tau = RC$  time constant is 16ns, the resistor size can be solved since the capacitor value has been set to be 4pF on C1,

$$R = \frac{16 \text{ nsec}}{4pF}$$

#### $R = 4k\Omega$

As expected, the input block will now have its acquisition time increased drastically. However, since there is 200ns allotted for the sampling of the circuit there room for this increase. To ensure the acquisition time is under 200ns, the figure below shows the acquisition time according to the different resistance values from 0 to  $10k\Omega$ :

Figure 37 - Acquisition Time Dependence after Adding New Resistor

## 5.2.1 RESISTOR TOLERANCE

According to the JAZZ library help files, the resistor tolerances will vary approximately by 25%. That assumption is made based on the following documentation:

| Salicided poly sheet resistance-Rs* | 4.46 | 5.95 | 7.44 | Ω/ 🗆 |

|-------------------------------------|------|------|------|------|

|-------------------------------------|------|------|------|------|

Therefore, once can see that this circuit may have a higher acquisition time than expected with a  $5k\Omega$  resistor. However, even with a 25 percent increase of resistance the acquisition time is still below the 200ns mark.

|                  | -25%     | Expected | +25%                |

|------------------|----------|----------|---------------------|

| Value            | 3 kΩ     | 4 kΩ     | $5 \text{ k}\Omega$ |

| t <sub>ACO</sub> | 111 nsec | 148 nsec | 185 nsec            |

t<sub>ACQ</sub>

Table 11 - Effect of Tolerances

To see the variation, the THD was also simulated. It can see that the swing in distortion does not vary much when the resistor is varied, as shown in Figure 38.

**Figure 38 - THD Dependence on Resistor Variation**

Using Eq. 21, the roll-off frequency will now be

$$f_h = \frac{1}{2\pi \cdot RC} = \frac{1}{2\pi \cdot 16ns} = 9.95 \text{ MHz}$$

$$f_h \approx 10 \text{ MHz}$$

As stated in Section 3.5.1, the SNR of ADC is the integral of all the noise in a system. Therefore, by reducing total bandwidth of the input of the ADC the signal-to-noise ratio is reduced as well.

## 5.2.2 IMPLEMENTATION OF INPUT BLOCK

In the actual input block designed for this ADC, a 4 capacitor implementation chosen with a capacitor size of 1pF. Therefore all transistors need to be sized accordingly. The next page shows a diagram of this concept.

9

## 5.2.3 LAYOUT OF THE INPUT BLOCK

When creating the layout of this input block it was imperative to have a low resistance path to charge and discharge the gates of the MOSFET's. This is due to the extremely high gate capacitance inherent in the large size of the MOSFET's. The large gate capacitances create high surge currents when switching and to increase the speed of switching large metal runs are needed between the input buffers and the input MOSFET's. Figure 39 below shows the layout of the input block of the Cyclic Converter.

Figure 39 - Layout of Input Block

50

## **6** The Switched Capacitor Network

One of the key characterisitcs of the Cyclic ADC is that it is able to use sampled values after a decision has been made and apply those values to the residue amplifier. The ability to do analog math with these values and sample the input with ease comes from the switch capacitor array.

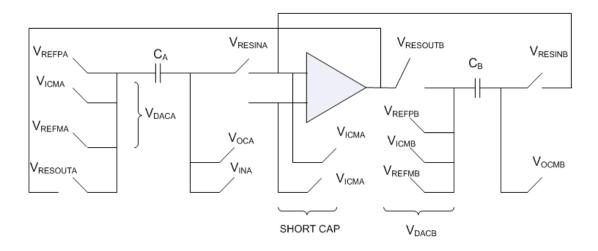

Figure 40 - Switch Capacitor Array Block and its Interaction with other Blocks

The switch capacitor network interacts with every block of the design, since the values on the capacitor dictate the input and output values of the ADC.

It is not surprising that an extensive amount of time was spent in this network. This section will serve to explain the various switch capacitor designs create and the reasons why those designs were discontinued.

## 6.1 DEFINING THE CORRECT NUMBER OF CAPACITORS FOR THE NETWORK

A crucial part of the design of the Cyclic ADC is to decide how many capacitors will be used in the DAC. More capacitors allow for more configurations but adds to the level of complexity by using additional transistors for switching and transmission.

## 6.1.1 USING ONE CAPACITOR

Using one capacitor as seen by the figure below means that there is one capacitor on each input and one capacitor on each output of the differential amplifier. The differential counterpart is not considered in this example for simplicity. One capacitor means that the amplifier's input will have one capacitor and the amplifier's output will have one capacitor as well. This number is doubled for the differential functionality.

Figure 41 - Example of Using One Capacitor

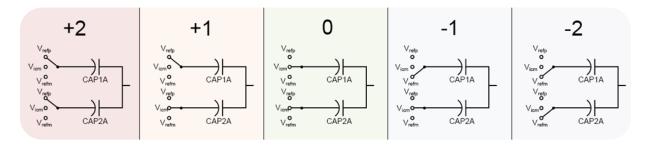

Although the approach of using one capacitor makes the circuit's functionality very simple, this approach proved to be ineffective immediately. This is due to a simple factor. Symbolized in the graph as  $V_{DAC}$  is the block responsible for choosing a decision based on a previous block. The decision created by this block results in the switching to its respective voltage reference. However, since the differential amplifier does not have a perfect gain of 2, two additional decisions need to be made. With this design, two additional voltage references would need to be created. Since industry standards and common practice usually limit the amount of off-chip reference voltages, it was necessary to introduce an extra capacitor to incorporate decisions -2, -1, 0, +1, and +2.

#### 6.1.2 USING TWO CAPACITORS

To incorporate the desired decisions, the use of 2 capacitors was then implemented. Since there is a positive, negative, and common mode reference voltage available for each capacitor, the resulting decision would be represented as the diagram below indicates:

Figure 42 - Diagram of Decisions with 2 Capacitors

Figure 42 shows the position of the references in each of the 5 decisions. The voltages  $V_{refp} V_{refm}$  and  $V_{icm}$  can be thought of "+2", "-2" and "0" respectively due to the fact that  $V_{icm}$  is the zero reference and  $V_{refp}$  and  $V_{refm}$  are ±0.34V away from  $V_{icm}$  it can be proven that these switching modes will produce the equivalent reference of ±0.17V away from  $V_{icm}$ . Since each capacitor is ½ the size as in the original one capacitor implementation the total capacitance does not change.

$$Plus \ 1 = \frac{(V_{refp} + V_{icm})}{2}$$

Eq. 23

Plus

$$1 = \frac{(1.43V + 1.09V)}{2} = 1.26V$$

Minus  $1 = \frac{(V_{refm} + V_{icm})}{2}$  Eq. 24

Minus

$$1 = \frac{(0.77 V + 1.09V)}{2} = 0.93V$$

Eq. 25

The voltages 1.26V and 0.93V correspond to the  $\pm 1$  decision voltage levels.

### 6.1.3 TESTING THE TWO CAPACITOR SYSTEM

As the testing indicated, implementing the  $\pm 1$  decisions was now possible, but not as effective as expected. The circuit used for testing this decision is shown below:

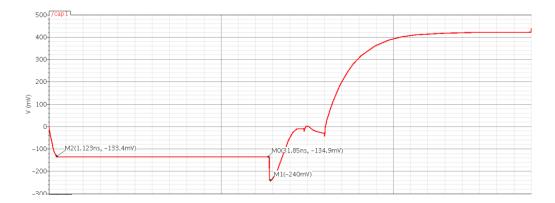

Figure 43 - Test Circuit for +/- 1 Decision

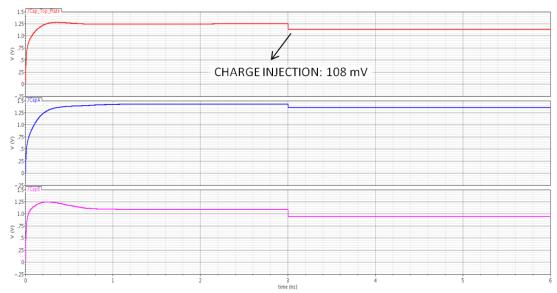

In other decisions, no charge is redistributed into the capacitors before switching. However, in this case, the issue lies with the fact that in the  $\pm$  1 decision mode, there is a 0.34V difference on the top plates of the capacitors. Since the top plates are connected to eachother, charge flows from one capacitor into another implementing the avereging function. This DAC decision must be done in less than a nanosecond in order to give the differential amplifier enough time to settle itself. In order for this to be done the resistance of the switches connecting the bottom plates to V<sub>icm</sub>, V<sub>refp</sub> and V<sub>refm</sub> must be sufficiently low. The main problem with this design was that the MOSFET switch controlling V<sub>icm</sub> had a very low overdrive voltage causing the transistor to stay in the saturation region only allowing a small amount of current to flow. This caused the N<sub>mos</sub> transistor connecting V<sub>icm</sub> to the bottom plate of the capacitor to be sized 20 times as large as the V<sub>refm</sub> transistor. This caused a substantial amount of charge from the channel of the MOSFET to be forced into the 2pF capacitor when the transistor was turned off, causing a large change in voltage in the capacitors holding voltage information of the previous cycles. Figure 44 shows this charge injection affecting the input.

Figure 44- Example of Charge Injection: Capacitor being Switched between a 500µm PMOS and a 250µm NMOS

As the transient response above shows, the charge forced into the capacitor changes the voltage across the capacitor by over 100mV as indicated by point M1. Therefore a new alternative had to be created that did not use V<sub>icm</sub> to make critical DAC decisions.

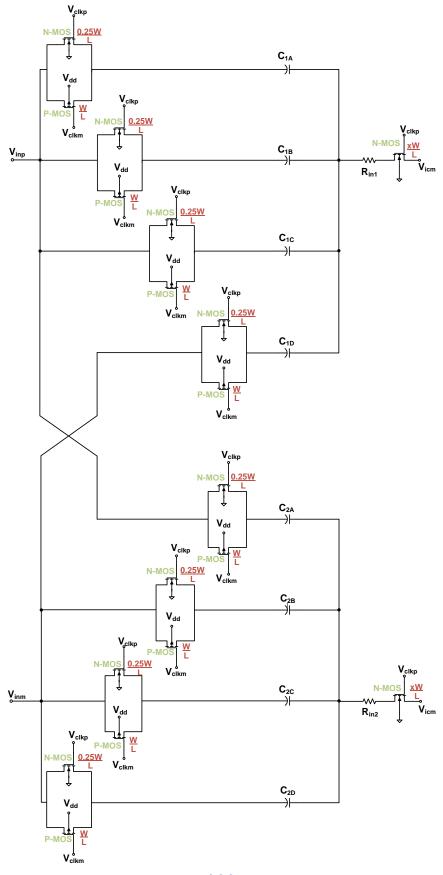

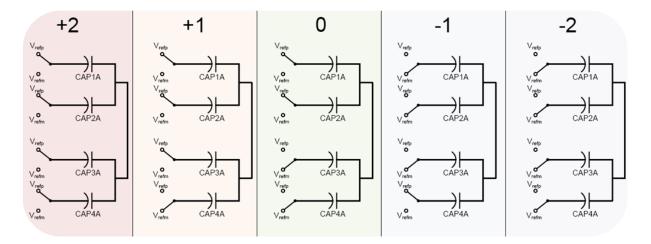

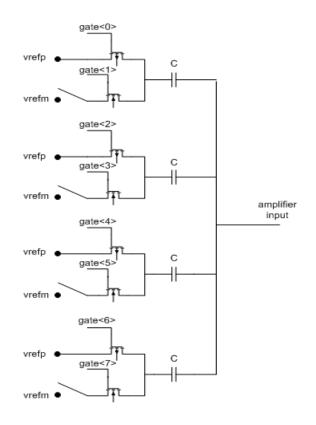

## 6.2 THE FINAL SWITCH CAPACITOR DESIGN: FOUR CAPACITORS

The approach in resolving this issue was to try to minimize avoid the use of  $V_{icm}$  for decisions that needed charge redistribution. Instead four capacitors would be used to achieve the same result of the 5 DAC decisions while avoiding  $V_{icm}$ . In this model each capacitor would have  $\frac{1}{4}$  of the original capacitance causing die area to not increase by a substantial amount. The four capacitor model enabled the decisions to be made to make the decisions as seen in Figure 45.

Figure 45 - Method for Using 4 Capacitors

Using this design the  $\pm 1$  decisions will be made without the use of V<sub>icm</sub> as follows.

$$Plus \ 1 = \frac{(3*V_{refp} + V_{refm})}{4}$$

Eq. 26

$$Plus \ 1 = \frac{(3*1.43V + 0.77V)}{4} = 1.265V$$

$$Minus \ 1 = \frac{(3*V_{refm} + V_{refp})}{4}$$

Eq. 27

$$Minus \ 1 = \frac{(3*0.77V + 1.43V)}{4} = 0.935V$$

It can be seen that the 4 capacitor implementation yields a similar result as the 2 capacitor approach as seen in the table below.

#### **Table 12 - Comparison of Decisions**

| Decision | 2 Capacitor<br>Implementation | 4 Capacitor<br>Implementation |

|----------|-------------------------------|-------------------------------|

| +2       | 1.43V                         | 1.43V                         |

| +1       | 1.26V                         | 1.265V                        |

| 0        | 1.09V                         | 1.1V                          |

| -1       | 0.93V                         | 0.935V                        |

| -2       | 0.77V                         | 0.77V                         |

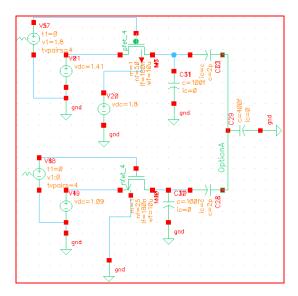

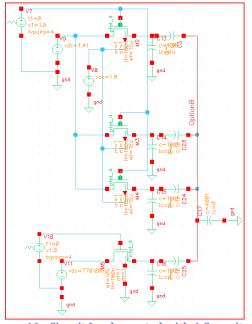

Figure 46 shows a test circuit used to simulate the 4 capacitor approach:

**Figure 46 - Circuit Implemented with 4 Capacitors**

56

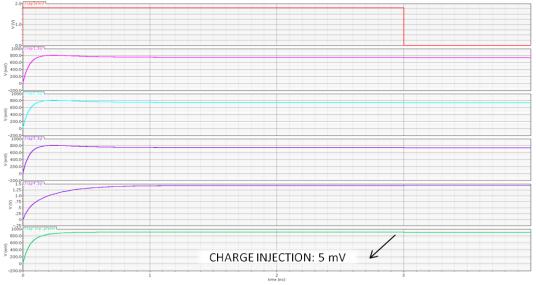

Using the 4 capacitor implementation, the overdrive voltages for the MOSFETS are much greater, reducing the Rds<sub>on</sub> of the MOSFETs allowing much smaller transistor widths to be used. Using this implementation, charge injection is reduced by a factor of about 21. Figure 47 and Figure 48 below shows a comparison of the 2 capacitor model and the 4 capacitor model for the implementation of the +1 decision.

Figure 47 - 2 Capacitor Implementation of "+1" Decision

Figure 48 – 4 Capacitor Implementation of "+1" Decision

As seen in the figures above, the charge injection is reduced from 108mV to 5mV a factor of more than 21 improvements, while still complying with the 1ns charge redistribution time. Another advantage of using the 4 capacitor design is that due to the enormous decrease in MOSFET width,

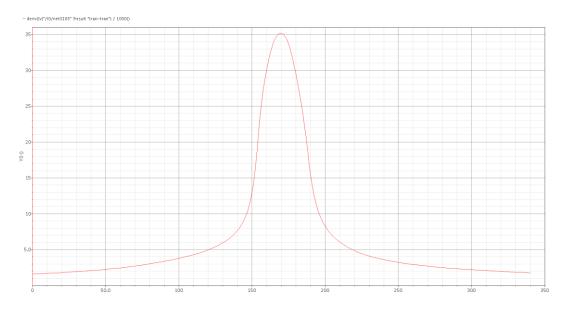

the overall die area for the design is actually reduced. Figure 49 shows a schematic representation of the switched capacitor network including a model of the parasitic on the top and bottom plates of the capacitors. Each of the 1pF capacitors has 250fF of parasitic capacitance on their bottom plates and a combined 40fF capacitance on the node connecting the top plates of the capacitors.

Figure 49- Switched Capacitor Circuit

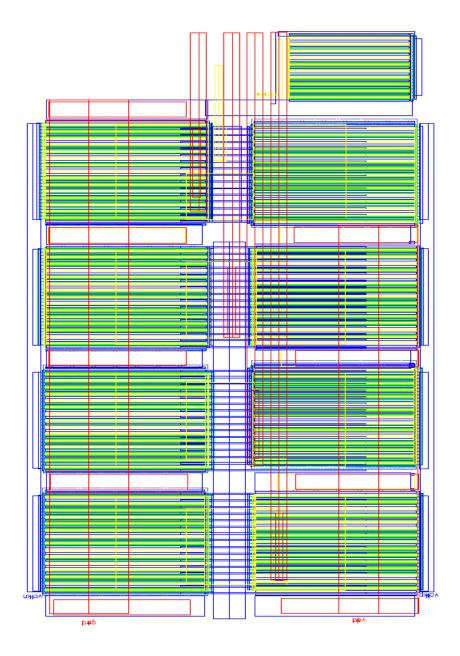

## 6.3 LAYOUT OF THE SWITCHED CAPACITOR CIRCUT

The layout of the switched capacitor circuit presented to be a challenge to create a compact design due to the 4 independent capacitors and numerous interconnects between the MOSFETs. To provide a compact design, the odd layers of metal runs were used for horizontal connections and even layers were used for vertical runs. Figure 50 below shows the layout of the switched capacitor circuit.

Figure 50- Switched Capacitor Layout

## 6.4 DETERMINING VOLTAGE REFERENCE VALUES FOR SWITCHED CAPACITORS

The voltage references being used by the ADC were originally found when using a two capacitor approach. However, the reference voltages were kept for the four capacitor approach due to the similarities in the design. The solution is based on the principle that the positive and negative reference voltages can be found when the difference between them is the common output voltage after shorting the inputs and outputs of the differential amplifier.

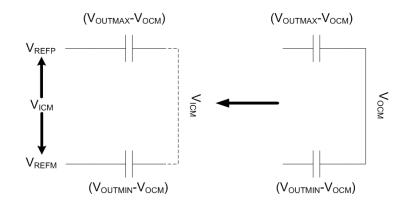

**Figure 51 - Derivation for Reference Voltages**

Therefore, the following two equations can be derived:

$$V_{refm} - (V_{outmin} - V_{ocm}) = V_{icm}$$

Eq. 28

$$V_{refp} - (V_{outmax} - V_{ocm}) = V_{icm}$$

Eq. 29

which, after some basic manipulation, will turn into:

$$V_{refm} = V_{icm} + V_{outmin} - V_{ocm}$$

Eq. 30

$$V_{refp} = V_{icm} + V_{outmax} - V_{ocm}$$

Eq. 31

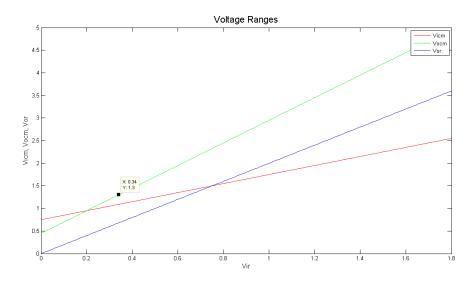

Plugging in the values (specified in section 6.6):

$$V_{refm} = 1.09V + 0.96V - 1.3V$$

$$V_{refm} = 0.75V$$

$$V_{refp} = 1.09V + 1.64V - 1.3V$$

$$V_{refp} = 1.43V$$

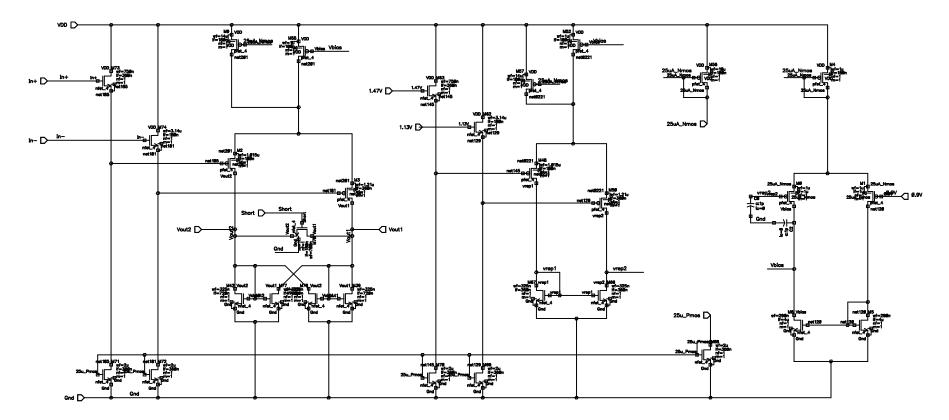

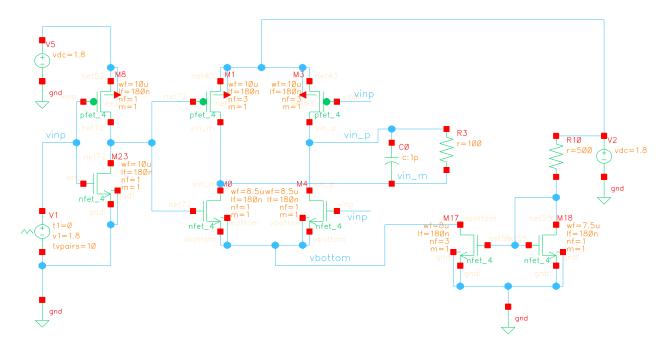

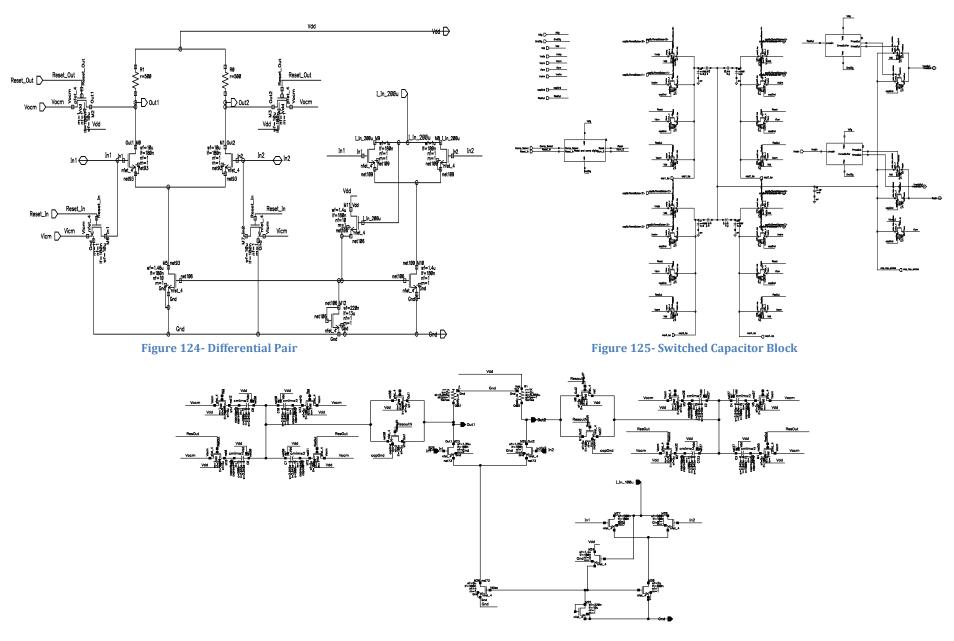

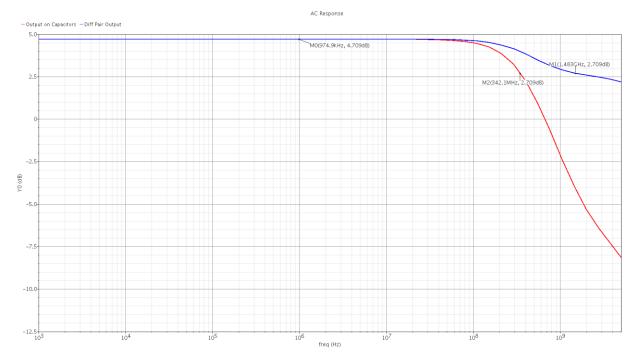

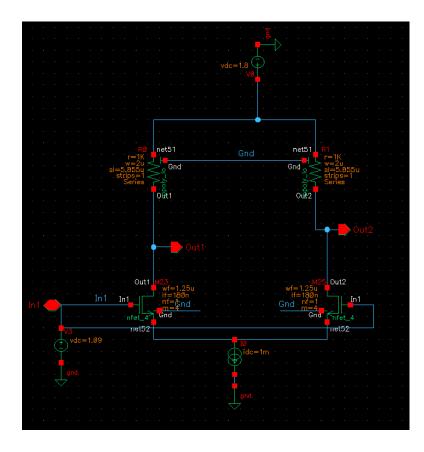

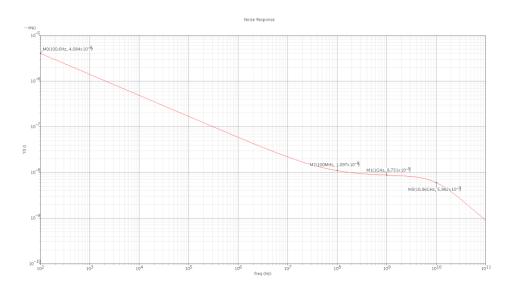

# DIFFERENTIAL AMPLIFIER

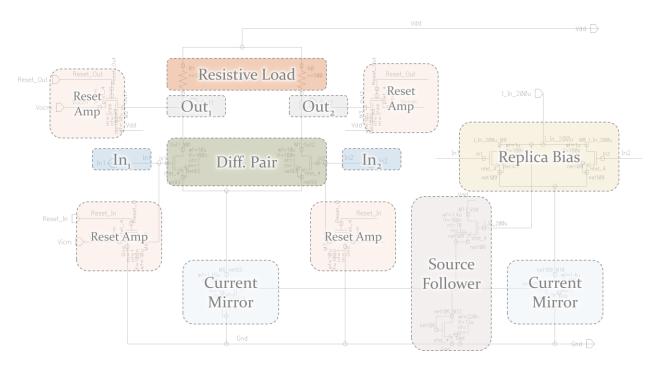

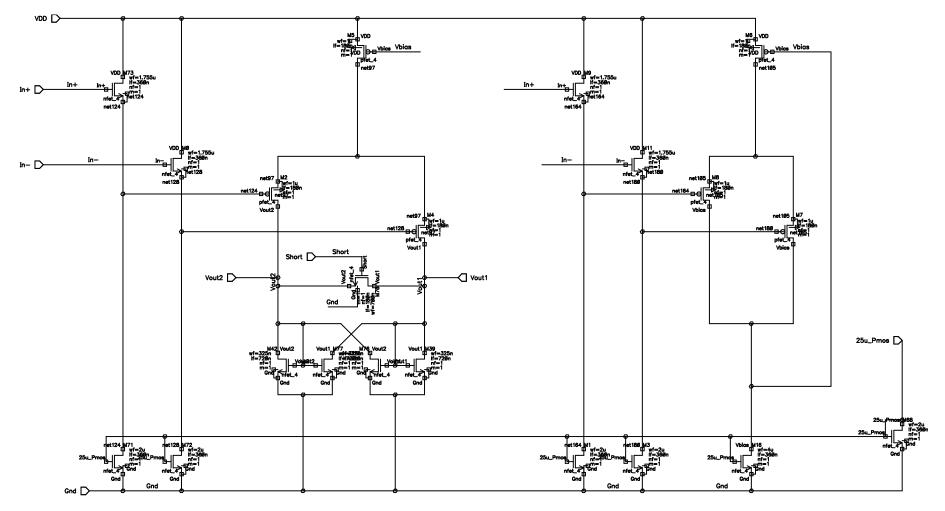

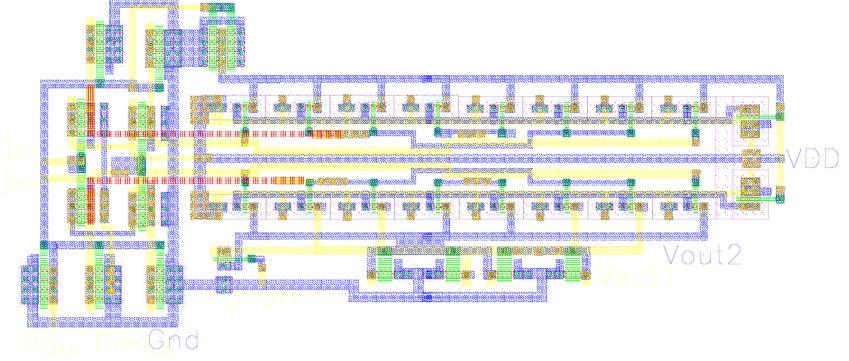

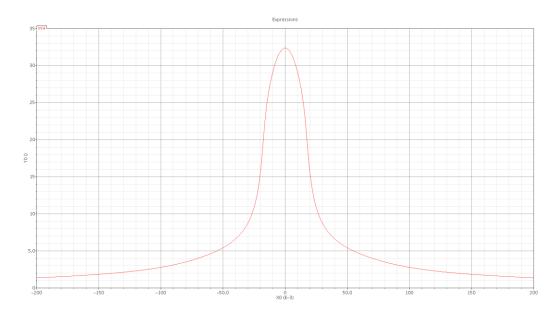

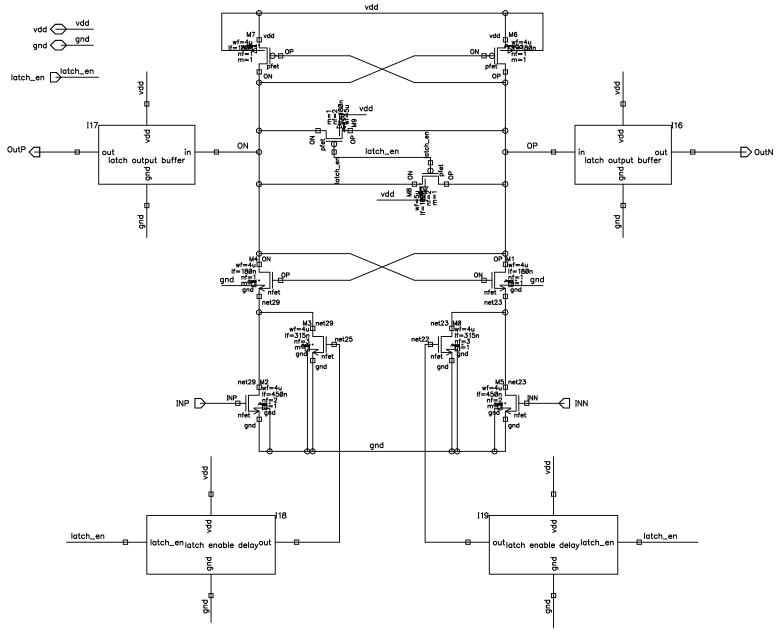

The differential amplifier block is the heart of the residue amplifier. Figure 52 shown below is the schematic of the differential amplifier and its supportive circuitry. The behavior of the differential amplifier and equations that governed its qualitative analysis was introduced previously in section 3.9. The role of each supportive component will be described in separate sections that follow. The goal regarding the design of the differential amplifier was using an open-loop differential amplifier in order to reduce the power consumption and complexity. The nonlinearity introduced by the open-loop configuration is compensated for in the off chip calibration routine.

Figure 52-Schematic Representation of Differential Amplifier

## 6.5 FUNDAMENTAL COMPONENTS OF THE DIFFERENTIAL AMPLIFIER