# DIGITALLY ASSISTED TECHNIQUES FOR NYQUIST RATE ANALOG-to-DIGITAL CONVERTERS

by

Rabeeh Majidi

A Thesis

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

in

Electrical and Computer Engineering

by

BEEHMA) D

April 29th 2015

APPROVED: Major Thesis Advisor ohn Professor Donald R. Brown

Dr Hui Wang, Sr. Principal Device Development Engineer, ON Semiconductor

#### Abstract

With the advance of technology and rapid growth of digital systems, low power high speed analog-to-digital converters with great accuracy are in demand. To achieve high effective number of bits Analog-to-Digital Converter(ADC)calibration as a time consuming process is a potential bottleneck for designs. This dissertation presents a fully digital background calibration algorithm for a 7-bit redundant flash ADC using split structure and look-up table based correction.

Redundant comparators are used in the flash ADC design of this work in order to tolerate large offset voltages while minimizing signal input capacitance. The split ADC structure helps by eliminating the unknown input signal from the calibration path. The flash ADC has been designed in 180nm IBM CMOS technology and fabricated through MOSIS. This work was supported by Analog Devices, Wilmington,MA.

While much research on ADC design has concentrated on increasing resolution and sample rate, there are many applications (e.g. biomedical devices and sensor networks) that do not require high performance but do require low power energy efficient ADCs. This dissertation also explores on design of a low quiescent current 100kS/s Successive Approximation (SAR) ADC that has been used as an error detection ADC for an automotive application in 350nm CD (CMOS-DMOS) technology. This work was supported by ON Semiconductor Corp, East Greenwich, RI.

#### Acknowledgments

It has been a great experience for me to study at Worcester Polytechnic Institute and a great honor to be a student of Professor John McNeill for almost five years. Over this period of time, I have gained experience in both teaching and doing research. His special method of guiding his students without providing them with immediate solutions for their problems helped me in becoming an independent researcher. I also was a teaching assistant for the major analog courses that Professor McNeill teaches at WPI and I think I have learned a lot from him during that time. His support for attending the International Solid-State Circuits Conference (ISSCC) which is a great conference about leading edge research in analog IC design has motivated me to pursue a high professional standard during my PhD research.

I would also like to thank my committee members, Professor Brown and Dr. Wang, for their expertise and review of this work.

My special thanks go to ON Semiconductor, East Greenwich RI, for supporting my PhD dissertation. I have been working at ON Semiconductor as an internship-Co-op employee and have taped-out the ultra-low power SAR ADC under direct supervision of Robert Davis, design manager in switching mode power supply group. I would like to thank him for his significant help in explaining the application of this ADC and all his help through implementation, tape-out and test chip evaluation. I also had the experience of working at ON Semiconductor as an Analog DFT validation Engineering Intern and have become familiar with various test methods under supervision of Andrew Laidler which gave me much insight into making a robust design. Many thanks to him for all his support on evaluating my test chip. I must say thank you to my other colleagues who were available to help me to manage this work. Thanks to: Shelby Raymond, Andrew Tarlan, Paul Gunaratnam, Alpha Diallo for the analog design advice, Wai Yung for digital design advice, Jon Buzzi for helping with the layout of SAR ADC, Justin Yerger for his help with using a microscope with laser to remove passivation layer and burn trim fuses, Betty Podgorski for bonding out the test chip, Marie Crowley for help with Mentor graphic software maintenance, Jayson Busila for his advice on PCB design, and Robert Cushing for his help with using the needle probes and all the test set up.

The Flash ADC part of this work was carried out with the support of the Analog Devices and New England Center for Analog and Mixed Signal Design at WPI under the direction of Professor McNeill. I would like to thank Professor Zain Navabi for digital design advice. I am also thankful to my colleagues at the NECAMSID lab, Christopher David and Tsai Chen, former PhD students who were always available to help me with Cadence tool maintenance, Anthony Crasso for his help on MATLAB simulation for flash ADC calibration, Jianping Gong for his help with layout the Flash ADC. I would like to thank Robert Brown and Siamak Najafi for IT support and Robert Boisse for his help in soldering the flash ADC evaluation board.

My family has been a great support throughout my entire education. I would like

to thank my husband Dr. Ali Kiapour, my dad Dr. Mohammad Majidi, my mom Mina Farazdaghi who is my best teacher and support and my sister Dr. Fatemeh Majidi, for all their love, support, advice, patience during my hard time. Without their support this dissertation would not have been written.

# Contents

| 1        | Intr                       | roduction 1                                                                                                                                           | _  |

|----------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|          | 1.1                        | Motivation                                                                                                                                            |    |

|          | 1.2                        | Goals                                                                                                                                                 | 2  |

|          | 1.3                        | Dissertation Organization                                                                                                                             | 2  |

| <b>2</b> | Bac                        | kground 4                                                                                                                                             | F  |

|          | 2.1                        | ADC Characterization                                                                                                                                  | ŀ  |

|          | 2.2                        | ADC Nonidealities                                                                                                                                     | ;  |

|          |                            | 2.2.1 Quantization Error                                                                                                                              | ;  |

|          |                            | 2.2.2 Offset and Gain Error                                                                                                                           | 7  |

|          |                            | 2.2.3 Nonlinearity Error                                                                                                                              | 3  |

|          |                            | 2.2.4 Timing Error                                                                                                                                    | L  |

|          | 2.3                        | Figures of Merit and Performance Trends                                                                                                               | ł  |

|          | 2.4                        | ADC Architectures                                                                                                                                     | ŧ  |

|          |                            | 2.4.1 Flash ADC Structure                                                                                                                             | ;  |

|          |                            | 2.4.2 Redundant Flash ADC                                                                                                                             | ;  |

|          |                            | 2.4.3 SAR ADC Structure                                                                                                                               | 3  |

|          | 2.5                        | Calibration Techniques Overview                                                                                                                       | )  |

|          |                            | 2.5.1 Flash ADC Calibration                                                                                                                           | )  |

|          |                            | 2.5.2 SAR ADC Calibration                                                                                                                             | L  |

|          |                            | 2.5.3 The Split ADC Structure                                                                                                                         |    |

| -        |                            | Previous Works                                                                                                                                        | 2  |

|          |                            | 2.6.1 Flash ADC Research                                                                                                                              |    |

|          |                            | 2.6.2 SAR ADC Research                                                                                                                                |    |

|          |                            | 2.6.3 Split ADC Research                                                                                                                              |    |

|          | 2.7                        | Summary                                                                                                                                               |    |

| 3        | FL./                       | ASH ADC Calibration 29                                                                                                                                | )  |

| J        | <b>1 1 1 1 1 1 1 1 1 1</b> | Using Split-ADC for calibration                                                                                                                       |    |

|          | $3.1 \\ 3.2$               |                                                                                                                                                       |    |

|          | 3.2<br>3.3                 | Digital Error Correction    31      Calibration    32                                                                                                 |    |

|          | э.э<br>3.4                 | LMS Procedure                                                                                                                                         |    |

|          | 3.4                        | EMS Procedure       53         Behavioral Results       33                                                                                            |    |

|          | J.J                        | Demayloral Results $\ldots \ldots 00$ | ۶. |

|          | 3.6                               | Summary                                                                                                                    | 5 |  |

|----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|---|--|

| 4        | 4 FLASH ADC Chip Implementation 3 |                                                                                                                            |   |  |

|          | 4.1                               | System Overview                                                                                                            | 7 |  |

|          | 4.2                               | Analog Blocks                                                                                                              | 8 |  |

|          |                                   | 4.2.1 Dynamic Comparator Design                                                                                            | 8 |  |

|          |                                   | 4.2.2 Reference Ladder                                                                                                     | 4 |  |

|          |                                   | 4.2.3 Analog Shift Design                                                                                                  | 5 |  |

|          | 4.3                               | Digital Blocks                                                                                                             | 7 |  |

|          |                                   | 4.3.1 Decoder Design                                                                                                       |   |  |

|          |                                   | 4.3.2 Output Buffer Design                                                                                                 |   |  |

|          |                                   | 4.3.3 Summary                                                                                                              |   |  |

|          |                                   |                                                                                                                            |   |  |

| <b>5</b> |                                   | ASH ADC Testing and Analysis 55                                                                                            |   |  |

|          | 5.1                               | ADC Test Procedure                                                                                                         |   |  |

|          |                                   | 5.1.1 PCB Design                                                                                                           |   |  |

|          | 5.2                               | Flash ADC Evaluation                                                                                                       |   |  |

|          |                                   | 5.2.1 Simulation Results                                                                                                   |   |  |

|          |                                   | 5.2.2 Measurement Results                                                                                                  | 8 |  |

|          | 5.3                               | Performance Analysis                                                                                                       | 3 |  |

|          |                                   | 5.3.1 Summary $\ldots \ldots 6$ | 4 |  |

| 6        | SAI                               | R ADC Chip Implementation 6                                                                                                | 6 |  |

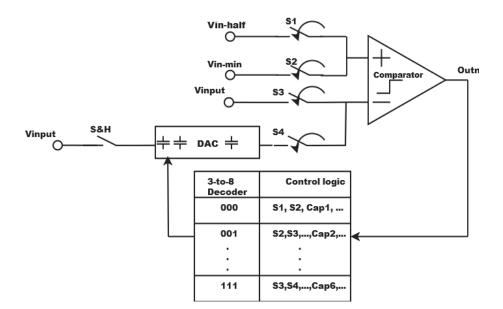

|          | 6.1                               | SAR ADC Proposed Algorithm                                                                                                 | 6 |  |

|          | 6.2                               | SAR ADC Implementation                                                                                                     | 6 |  |

|          | 6.3                               | ADC Building Blocks                                                                                                        |   |  |

|          | 0.0                               | 6.3.1 Dynamic Comparator                                                                                                   |   |  |

|          |                                   | 6.3.2 DAC Capacitor Network                                                                                                |   |  |

|          |                                   | 6.3.3 Switching Logic Network                                                                                              |   |  |

|          |                                   | 6.3.4 Sample and Hold                                                                                                      |   |  |

|          |                                   | 6.3.5 Refference Volatges                                                                                                  |   |  |

|          |                                   |                                                                                                                            |   |  |

|          |                                   | 6.3.6 Summary                                                                                                              |   |  |

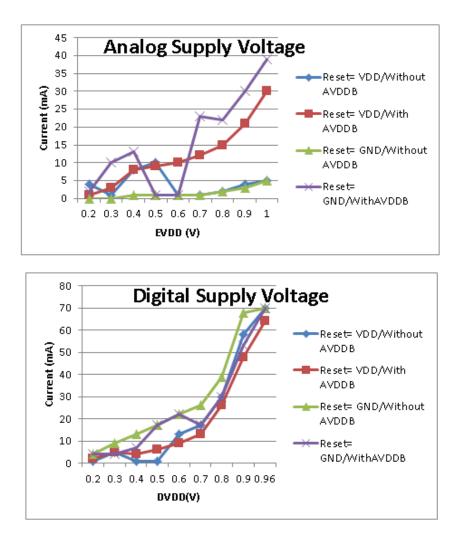

| <b>7</b> | SAI                               | R ADC Testing and Analysis 74                                                                                              | 5 |  |

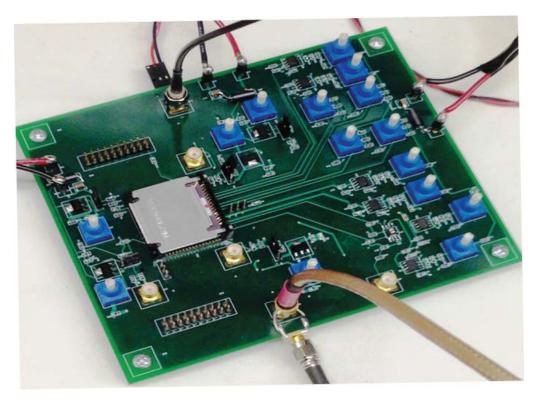

|          | 7.1                               | PCB Design                                                                                                                 | 6 |  |

|          | 7.2                               | Static Performance                                                                                                         | 8 |  |

|          | 7.3                               | Dynamic Performance                                                                                                        | 9 |  |

|          | 7.4                               | summary                                                                                                                    | 9 |  |

| 8        | Cor                               | aculsions 8                                                                                                                | 1 |  |

|          | 8.1                               | Future Work                                                                                                                |   |  |

|          |                                   |                                                                                                                            |   |  |

| $\mathbf{A}$ | Glossary |                                                      |    |

|--------------|----------|------------------------------------------------------|----|

|              | A.1      | Acronym                                              | 82 |

|              | A.2      | Flash ADC decoder design, verilog code               | 83 |

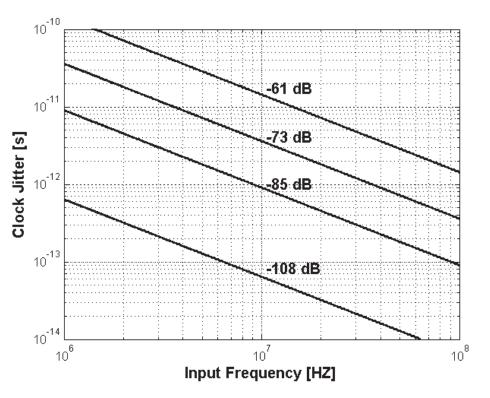

|              | A.3      | Sampling jitter at different SNR and input frequency | 89 |

|              | A.4      | Flash ADC, DNL/INL plot, MATLAB code                 | 90 |

|              | A.5      | SAR ADC, DNL/INL plot, MATLAB code                   | 91 |

|              | A.6      | SAR ADC, fft plot, SNR calculation MATLAB code       | 92 |

# List of Figures

| 2.1          | Ideal ADC transfer function                                                    | 5       |

|--------------|--------------------------------------------------------------------------------|---------|

| 2.2          | Quantization Error as a function of input voltage [1]                          | 7       |

| 2.3          | ADC Offset error                                                               | 8       |

| 2.4          | ADC Gain error                                                                 | 9       |

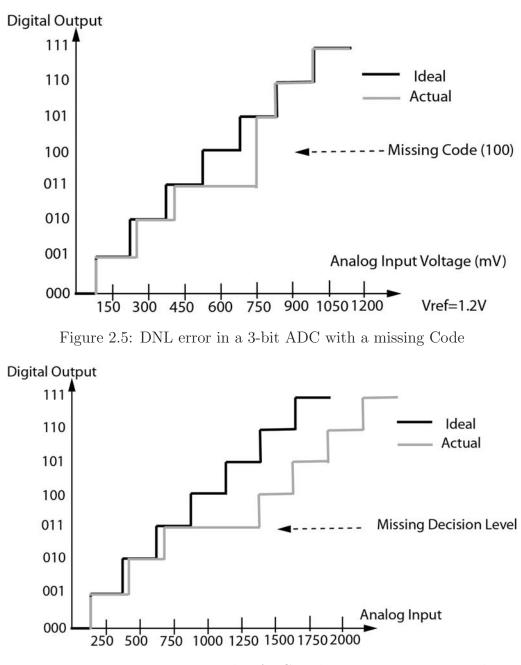

| 2.5          | DNL error in a 3-bit ADC with a missing Code                                   | 10      |

| 2.6          | DNL error in a 3-bit ADC with missing Decision Levels                          | 10      |

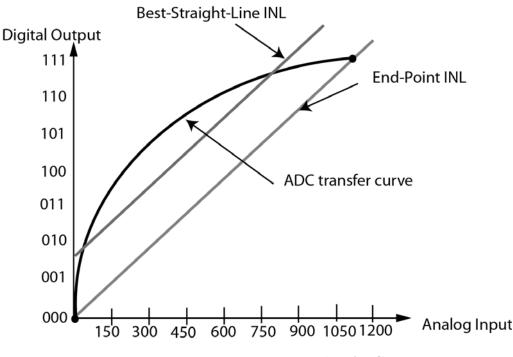

| 2.7          | INL error in a 3-bit ADC                                                       | 11      |

| 2.8          | Sampling Jitter at different SNR and input frequency $[2]$                     | 13      |

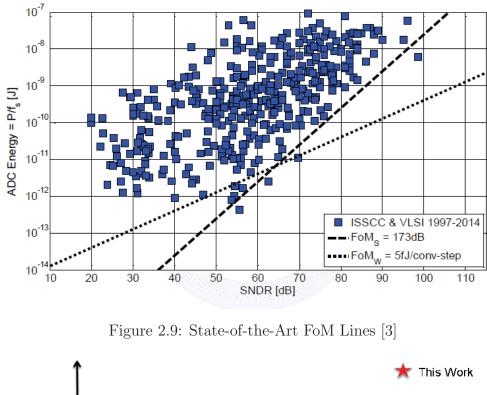

| 2.9          | State-of-the-Art FoM Lines [3]                                                 | 15      |

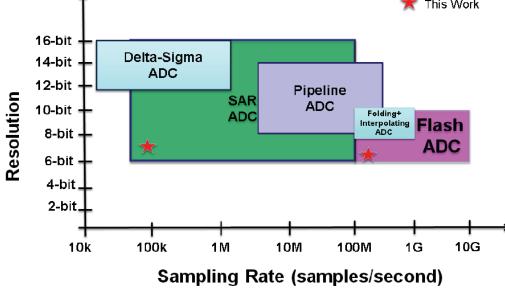

| 2.10         | Different ADC architectures comparison [4]                                     | 15      |

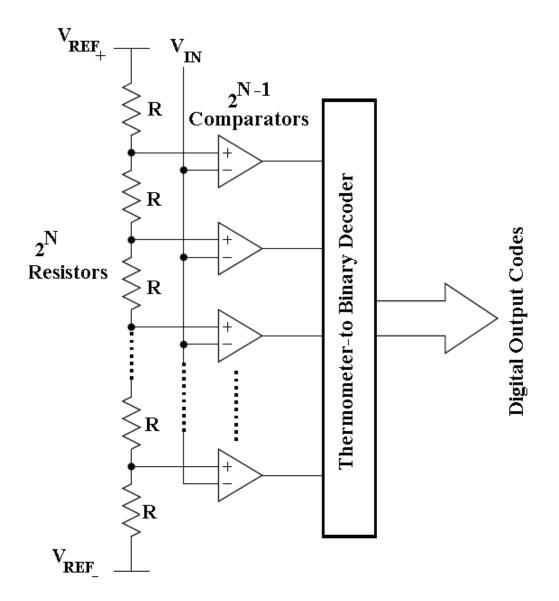

|              | Block diagram of a flash ADC                                                   | 17      |

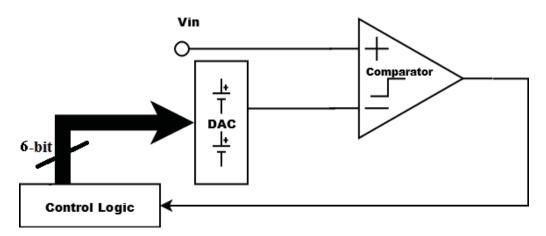

|              | SAR ADC architecture                                                           | 18      |

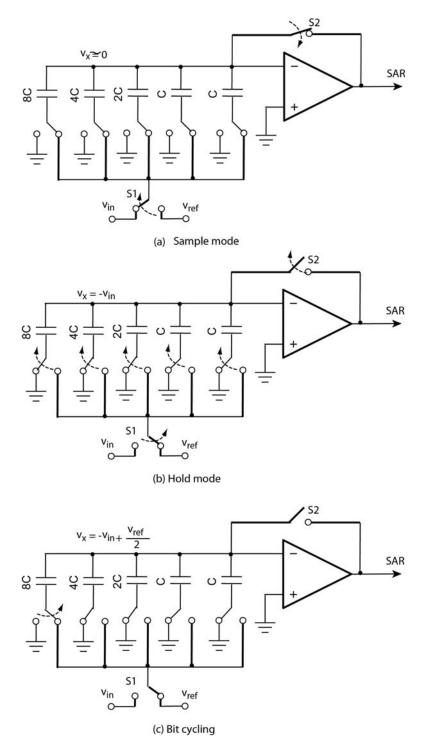

|              | A 4-bit charge-redistribution SAR ADC [5]                                      | 19      |

|              | Split ADC Architecture [6]                                                     | 22      |

| 2.15         | The basic principle of redundancy method [7]. Selected comparators             |         |

|              | are highlighted                                                                | 23      |

|              | Survey of Flash ADCs.                                                          | 24      |

|              | Survey of SAR ADCs.                                                            | 25      |

| 2.18         | Survey of ADCs using "Split ADC" approach                                      | 26      |

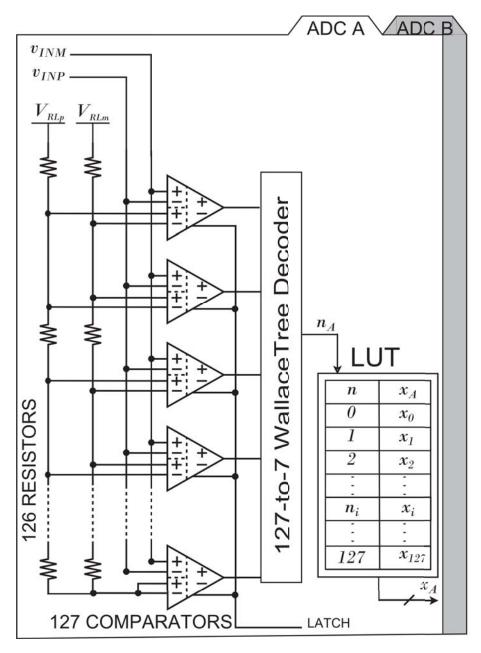

| 3.1          | Block diagram of split redundant flash ADC                                     | 30      |

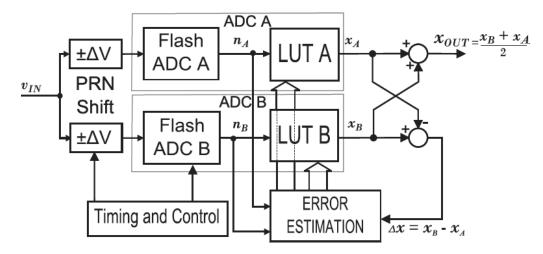

| 3.1<br>3.2   | System block diagram                                                           | 31      |

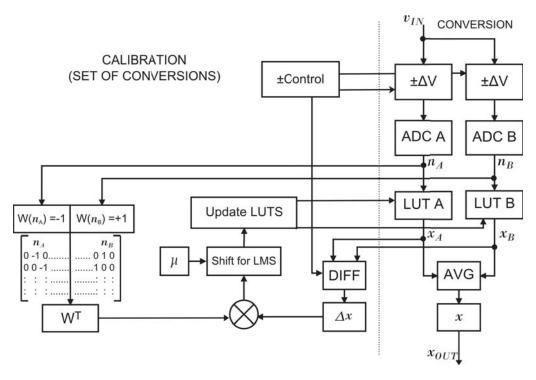

| 3.2<br>3.3   | Calibration block diagram                                                      | 34      |

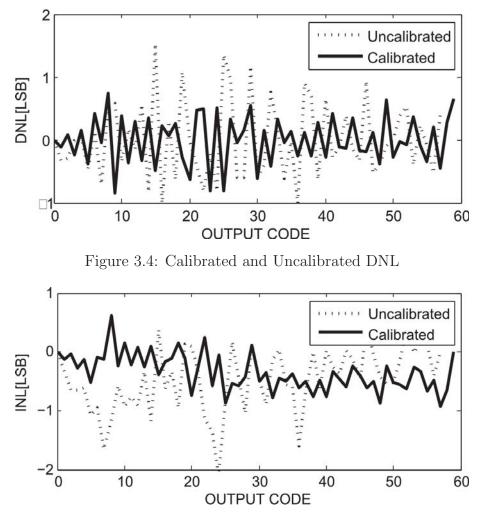

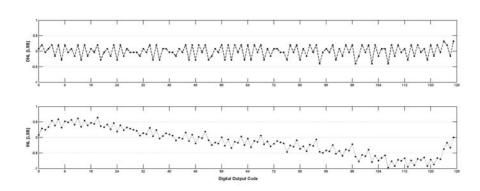

| 3.4          | Calibrated and Uncalibrated DNL                                                | 35      |

| $3.4 \\ 3.5$ | Calibrated and Uncalibrated INL                                                | 35 - 35 |

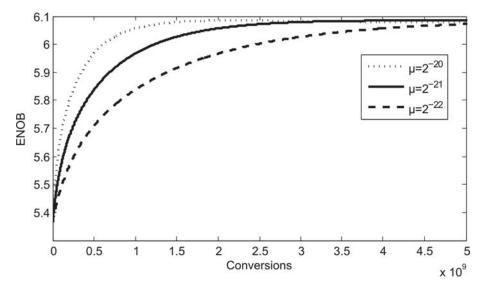

| 3.6          | Calibration Convergence                                                        | 36      |

| 0.0          |                                                                                | 50      |

| 4.1          | Block diagram of split redundant flash ADC                                     | 38      |

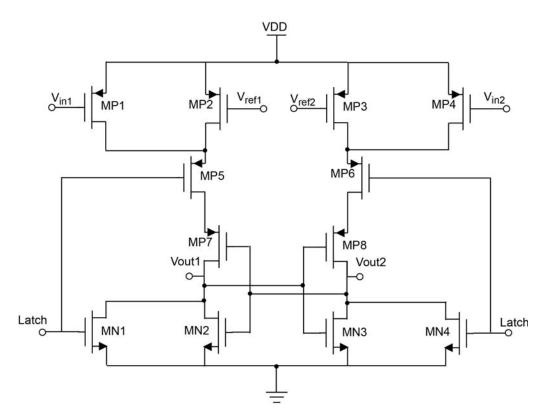

| 4.2          | Block diagram of dynamic comparator                                            | 39      |

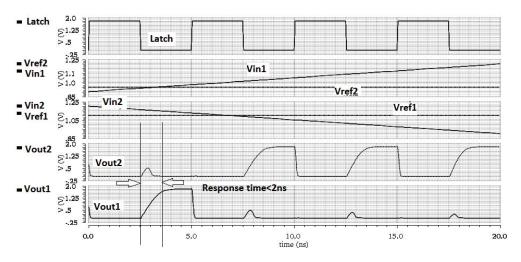

| 4.3          | Dynamic comparator simulation results                                          | 40      |

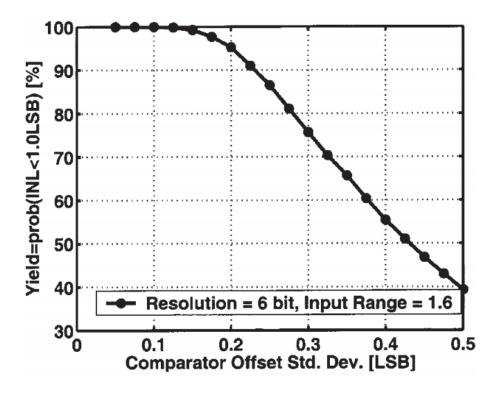

| 4.4          | Indication of comparator offset in flash ADC design [8]                        | 41      |

| 4.5          | MonteCarlo simulation of yield of ADC vs. $\sigma_{offset}$ of comparator [8]. | 42      |

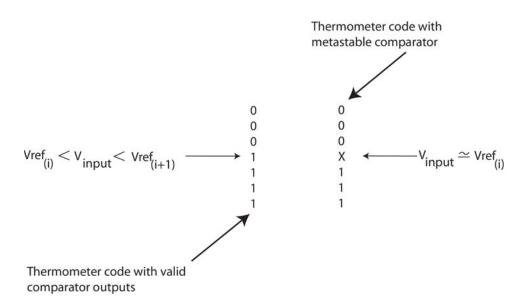

| 4.6          | Flash ADC with unstable thermometer code as digital output [9]                 | 43      |

| 4.7          | Regenerative latch structure [2]                                               | 43      |

|              |                                                                                |         |

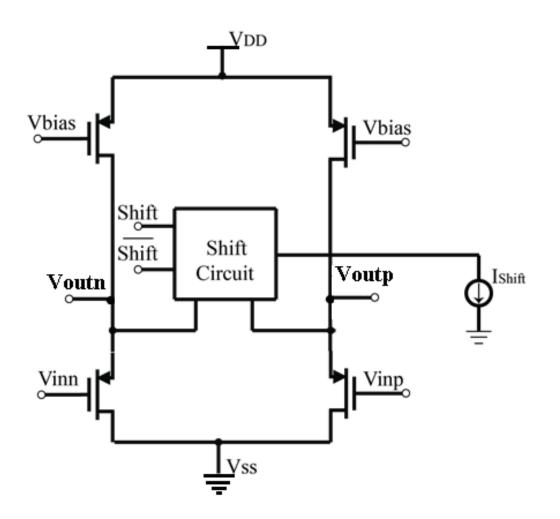

| 4.8          | Analog Shift Circuit                                                              | 45       |

|--------------|-----------------------------------------------------------------------------------|----------|

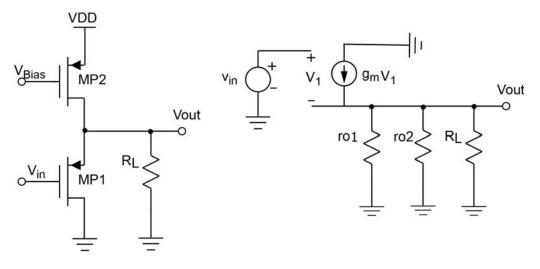

| 4.9          | Source Follower Circuit                                                           | 46       |

| 4.10         | Source Follower with cascode bias Circuit                                         | 47       |

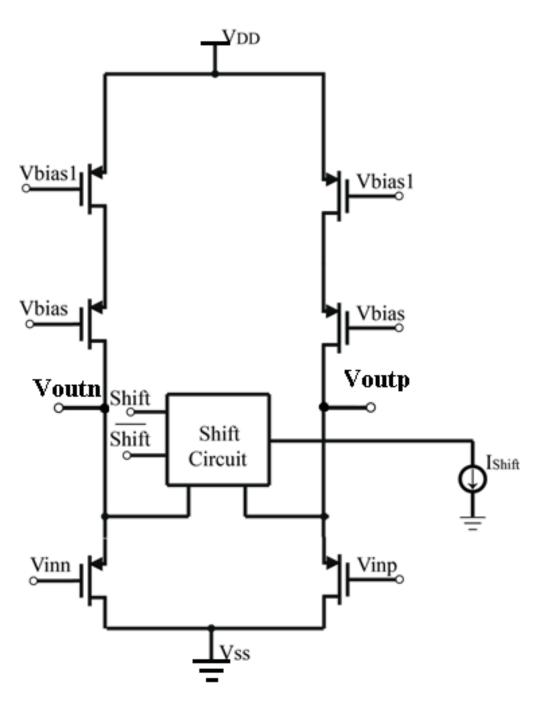

| 4.11         | Analog shift schematic view                                                       | 48       |

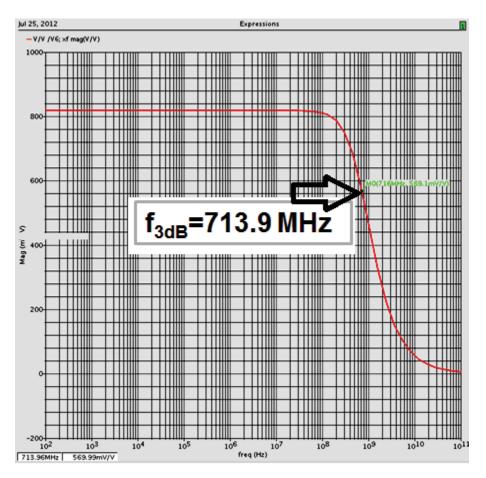

| 4.12         | Analog shift: AC simulation result                                                | 49       |

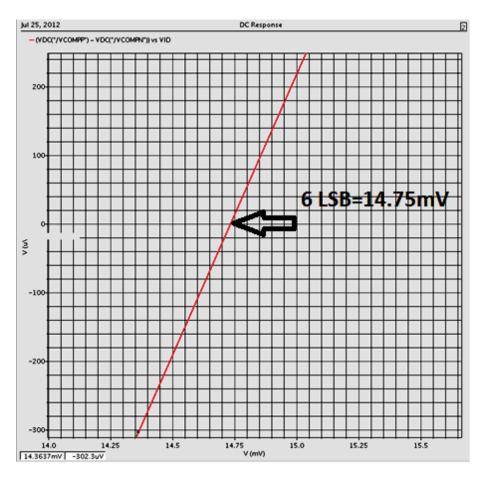

| 4.13         | Analog shift simulation result: DC response                                       | 50       |

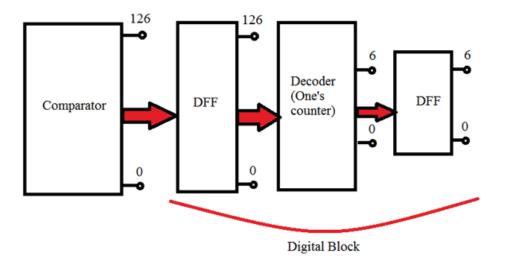

| 4.14         | Digital block diagram of flash ADC                                                | 50       |

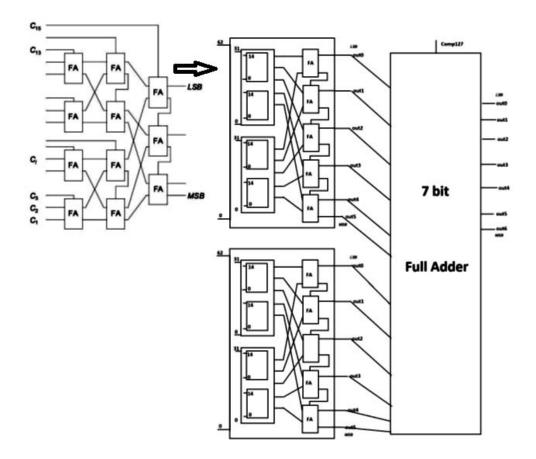

| 4.15         | Wallace tree decoder for a 7-bit flash ADC                                        | 51       |

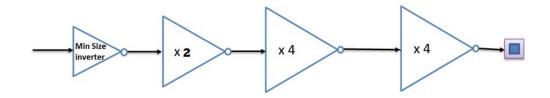

| 4.16         | Block diagram of output buffers                                                   | 51       |

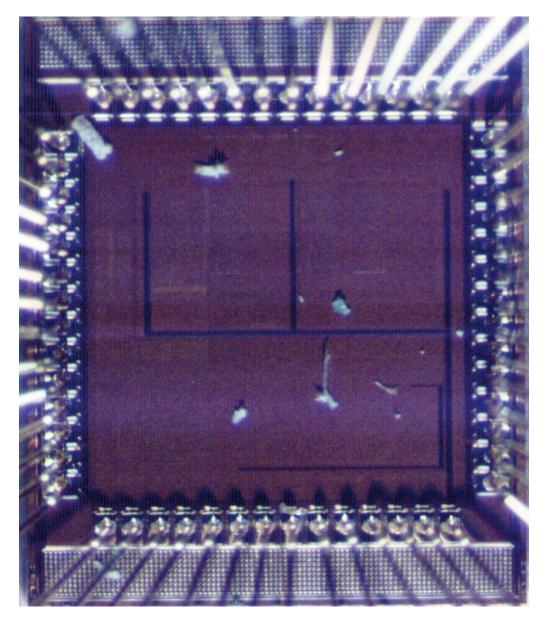

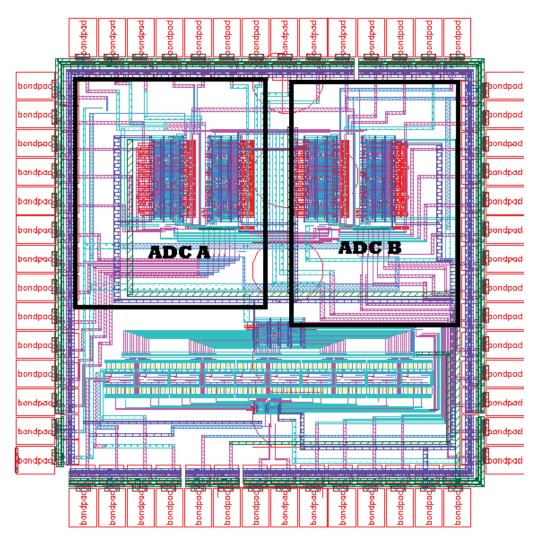

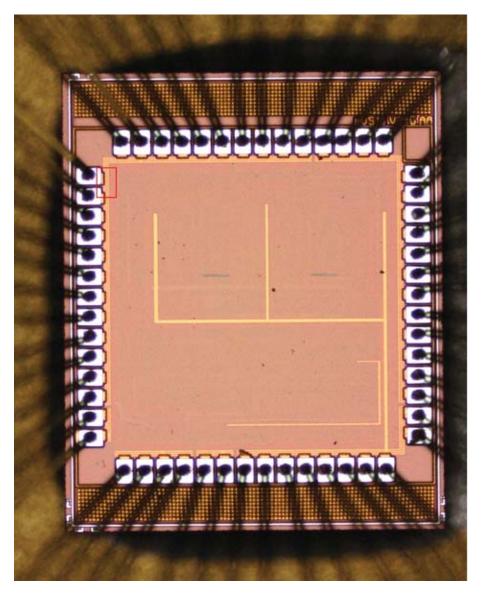

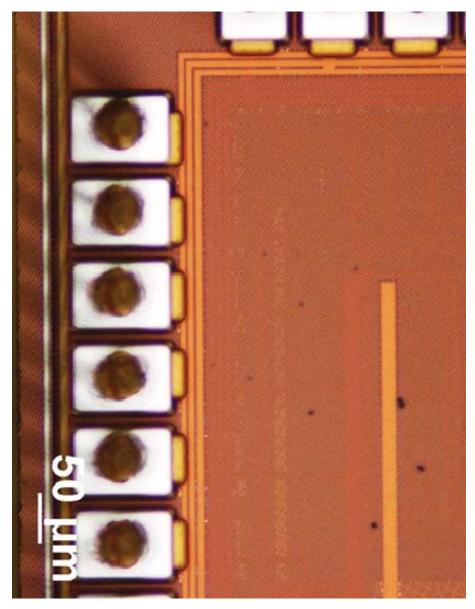

| 5.1          | Flash ADC die photo                                                               | 53       |

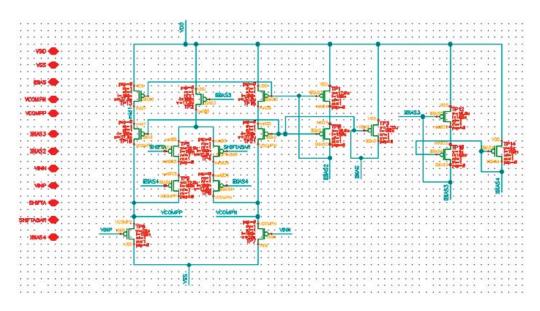

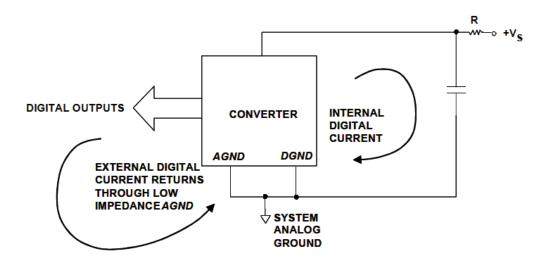

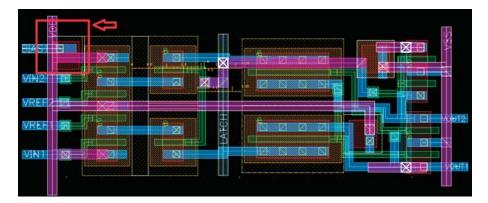

| 5.2          | Flash ADCs Layout                                                                 | 54       |

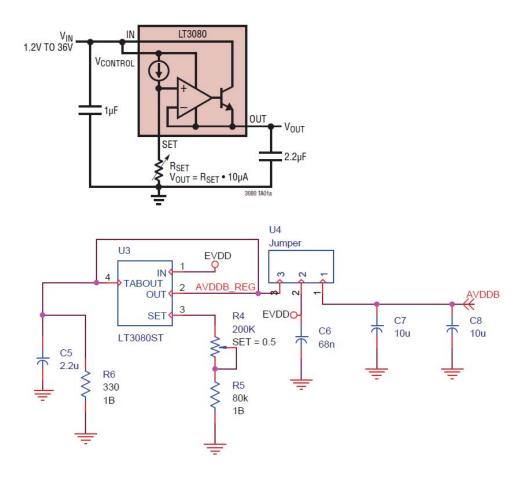

| 5.3          | Linear regulators with low dropout voltage                                        | 55       |

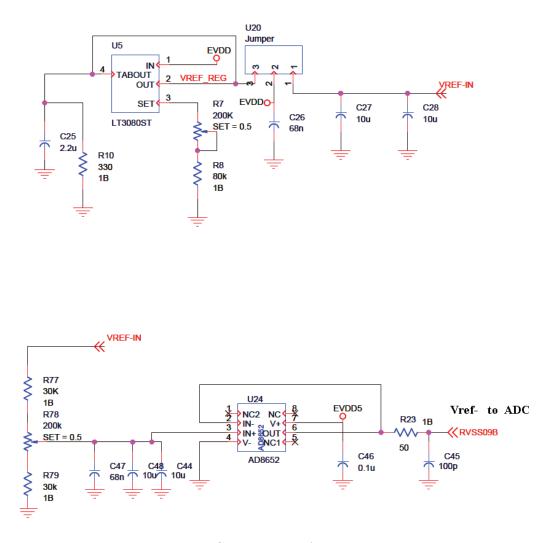

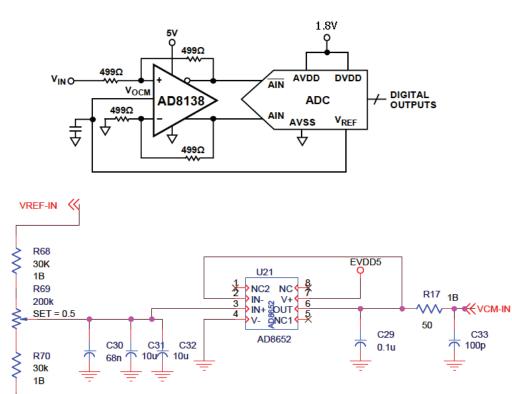

| 5.4          | Generating reference voltages                                                     | 56       |

| 5.5          | Generating differential input for each flash ADC                                  | 57       |

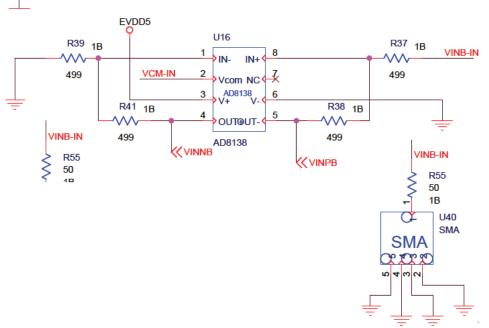

| 5.6          | Connecting the Analog (AGND) and Digital Ground (DGND) Pins                       | 01       |

|              | of ADC to System Analog Ground                                                    | 58       |

| 5.7          | PCB layout for flash ADC evaluation                                               | 58       |

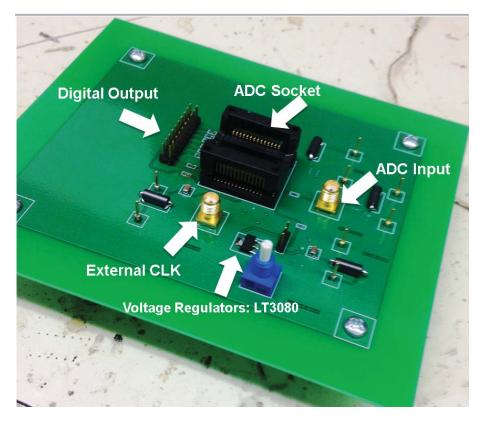

| 5.8          | PCB board for flash ADC evaluation                                                | 59       |

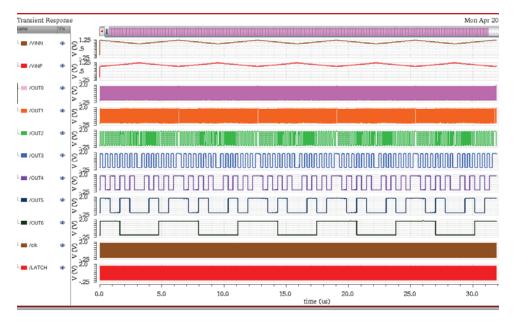

| 5.9          | Simulation results for redundant flash ADC evaluation                             | 59       |

| 5.10         | Procedure of Chip Failure Determination                                           | 61       |

|              | ESD test for flash ADC evaluation                                                 | 62       |

|              | Test chip under optical microscope                                                | 63       |

|              | Closer view of ESD and bond pads                                                  | 64       |

|              | Layout mistake on PMOS substrate contact                                          | 65       |

|              | DNL result for redundant flash ADC                                                | 65       |

| 6.1          | Proposed SA-ADC architecture                                                      | 68       |

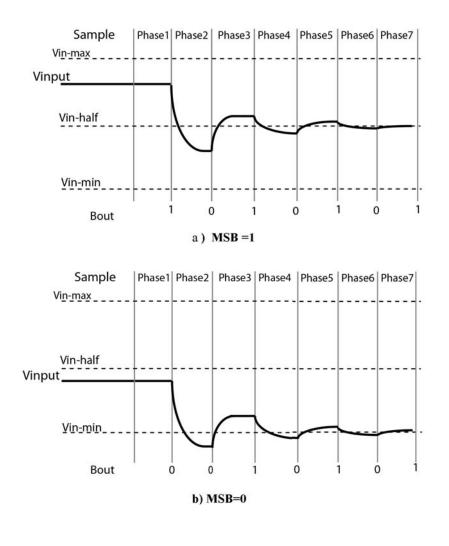

| 6.2          | Waveforms of proposed switching procedure: (a) MSB=1 (b) MSB=0                    | 69       |

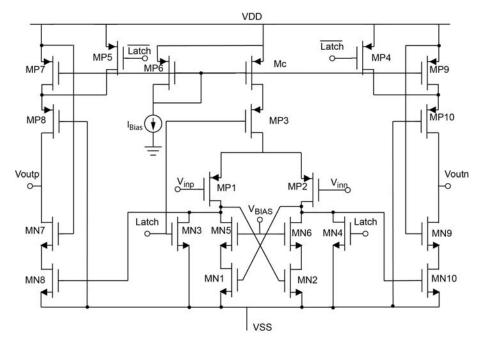

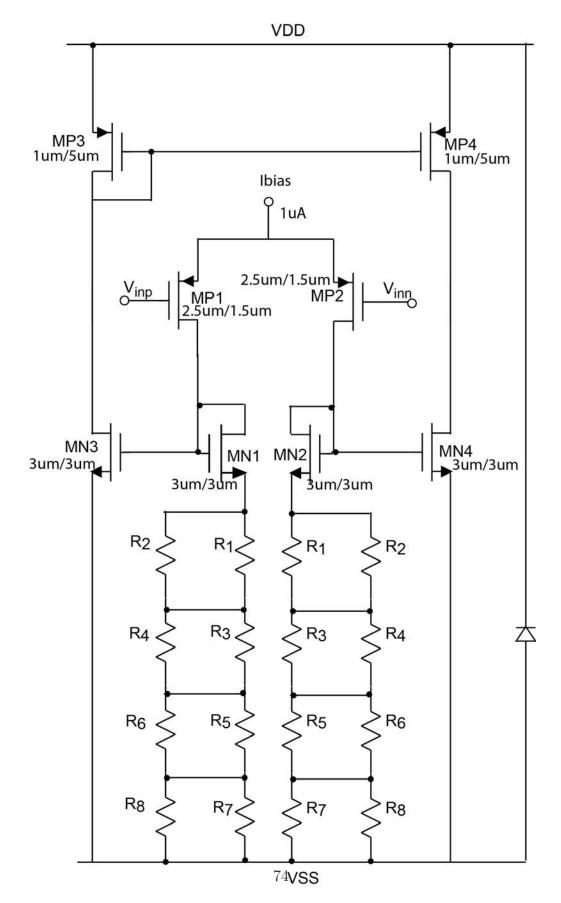

| 6.3          | Dynamic Comparator                                                                | 70       |

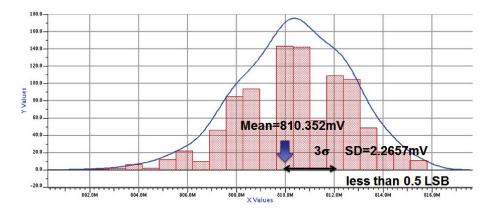

| 6.4          | Monte-Carlo simulation of comparator offset. $\sigma = 2.26 \text{mV}$            | 70       |

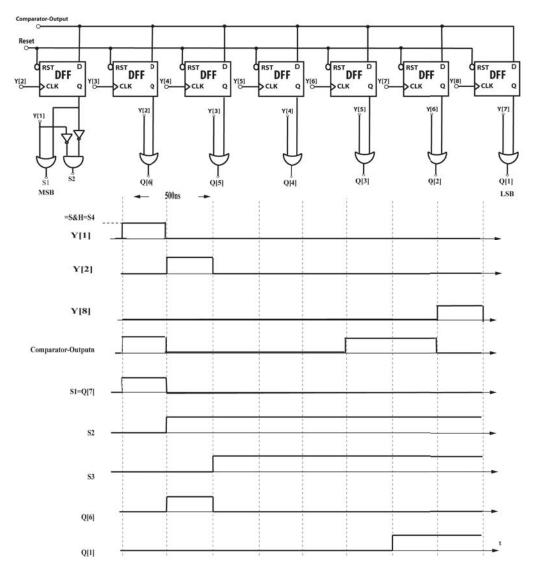

| 6.5          | Control logic switches and timing                                                 | 71       |

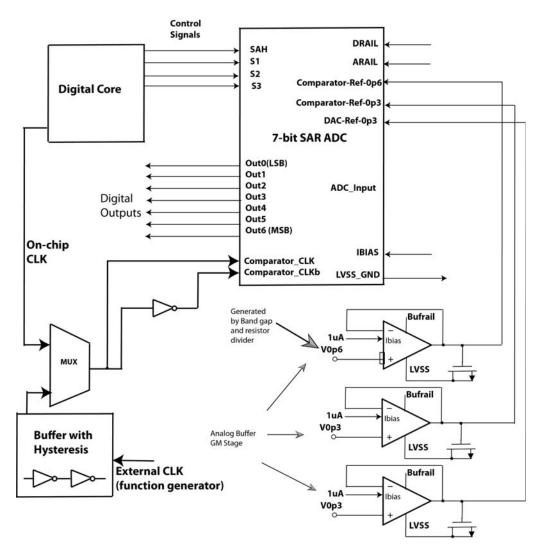

| 6.6          | Top level schematic of SAR ADC design                                             | 73       |

| 6.7          | Analog buffer with tuning                                                         | 74       |

|              |                                                                                   |          |

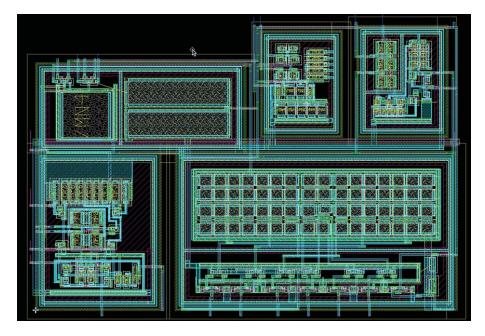

| 7.1          | Analog portion of SAR ADC layout, including buffers, switches, DAC and comparator | 76       |

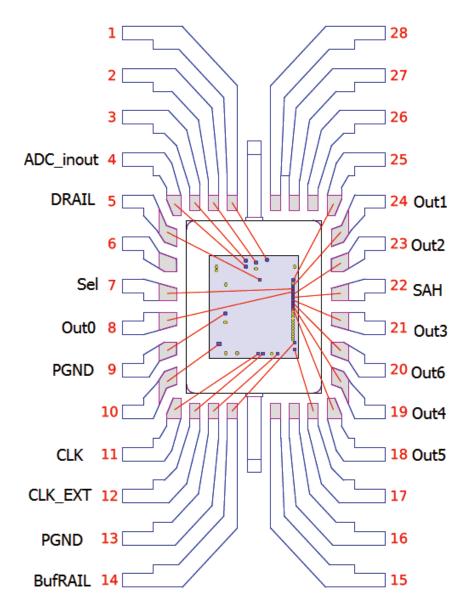

| 7.2          | SAR ADC bonding diagram                                                           | 70<br>77 |

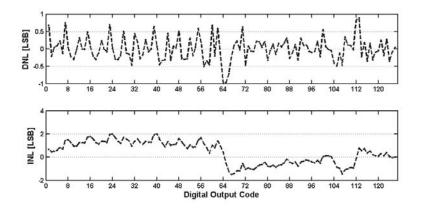

| 7.2<br>7.3   | Measure DNL and INL for Die1                                                      | 78       |

| $7.3 \\ 7.4$ | Measured DNL and INL for Diel                                                     | 78<br>79 |

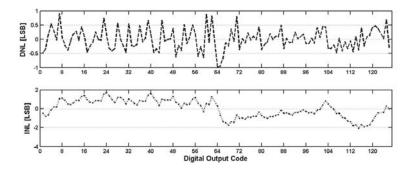

| $7.4 \\ 7.5$ | Measured DNL and INL with ramp input for Die1                                     | 79<br>79 |

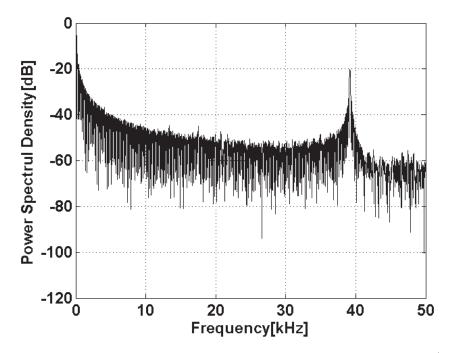

| 7.0 7.6      | Measured 4096-point FFT spectrum at 100 kS/s.                                     | 79<br>80 |

| 1.0          | $measured 4030-point rr r spectrum at 100 Ks/s. \dots \dots \dots \dots$          | 00       |

# List of Tables

| 2.1 | Comparison of different ADC Architectures            | 16 |

|-----|------------------------------------------------------|----|

| 2.2 | Comparison of different flash ADCs in previous works | 27 |

| 2.3 | Comparison of different SAR-ADCs in previous works   | 28 |

| 3.1 | System Simulation Parameters                         | 34 |

|     | System Simulation Results                            |    |

| 7.2 | SAR ADC performance analysis                         | 80 |

# Chapter 1 Introduction

## 1.1 Motivation

Analog-to-Digital Converters (ADCs) are employed to digitize continues analog signals into digital form with a certain number of bits of resolution. With the fast shrinking of CMOS process and rapid advance of digital integrated circuit technologies, high-performance low-cost ADCs are needed in many mixed-signal applications such as communications, software radio, audio, video and sensors [10]. Particularly, wireless receivers as well as high-density disk drives [11] require efficient, high speed, low-to-moderate resolution (5-8 bits) data conversion with a low jitter sample clock. Flash ADCs are typically excellent candidates for these types of applications [11] as the simple analog structure of flash ADCs enhances the feasibility to data converter design with technology scaling.

Designing in a deep submicron process enables high speed but at the price of increasing variation and device mismatch, which leads to decreasing the ADC effective number of bits (ENOB) and affecting the ADC accuracy. Increasing the device size will help with recovering the ENOB by improving matching, at the cost of increasing area and power consumption. Flash ADCs are composed of multiple comparators working in parallel, and device mismatch can cause offset error in each comparator and affect differential and integral nonlinearity (DNL and INL)of the ADC. There are several techniques for calibration found in Flash converters in order to mitigate the offset errors of comparators such as averaging and digitally controlled trimming [11] and combinations of analog and digital techniques have been used to calibrate and correct the output of the ADCs.

Technology scaling has a great impact on area and power consumption of integrated circuits. The power consumption of ADCs is a function of the technology node, the linearity and bandwidth [12]. In general, ADC design methods, that preserve the signal-to-noise ratio with scaling will increase the power consumption and area [12].Flash architectures with moderate resolutions are not challenged by noise requirements due to their low resolution [12]. However, power consumption of the multiple comparators and calibration circuits increase ADC power consumption

and on-chip error correction circuits increase the design complexity. This has lead to a motivation of the first part of this research on calibration of flash ADCs and improving the performance and accuracy of this type of data converter.

In some applications such as wireless sensor networks and biomedical devices [13] and electronic features in modern vehicles, power consumption is the primary concern while speed is of a secondary importance. The second half of this research focuses on a portion of the SAR ADC design that has moderate resolution and speed, but is ultra low power. This SAR ADC has been used as an error detection ADC in a feedback loop. This work explores the opportunity for further improvement in power with a new algorithm using capacitive DAC and area savings by eliminating the differential approach in favor of a single-ended architecture.

# 1.2 Goals

The goal of the first part of this work is to develop a digital background calibration algorithm applying a "Split-ADC" calibration structure and lookup-tablebased correction. Traditional methods used for offset improvements in comparators are based on increasing the size of the device according to Pelgrom matching formula [14]; while in this work small, power efficient comparators are used to design 7-bit flash ADC in order to minimize the ADC input capacitance. Redundancy is used to tolerate the large offset voltage of digital regenerative comparators. Digital background calibration is used to reduce analog complexity. The background approach estimates the error iteratively using least mean squares procedure and can be useful for any changes in threshold voltage of the comparators due to temperature variations or device mismatch.

The goal of the second part of this work is to present the design of a 7-bit SAR ADC that is used as a regulation ADC in a switching mode voltage regulator that uses a digital algorithm. The ADC is used as an error detection in a feedback loop. This design only has  $4\mu$ A current budget for this ADC. The ADC has been designed and fabricated at ON Semiconductor Corp.

# **1.3** Dissertation Organization

The remainder of this dissertation is organized as follows: Chapter 2 will describe flash ADC, SAR ADC and split ADC structures and address ADC characterization and nonidealities while summarizes some previous flash ADC calibration, SAR ADC low power design methods and split ADC techniques. In chapter 3 digital calibration of flash ADC will be discussed. Chapter 4 will present design aspects of the flash ADC designed for the test chip. Evaluation board for the test chip and measurement results are given in chapter 5. The proposed algorithm for the ultra low power SAR ADC and details on implementation of SAR ADC are presented in chapter 6. Testing and measurement results of the SAR ADC are shown in chapter 7. Chapter 8 summarizes and concludes this dissertation and proposes the directions for future research.

# Chapter 2

# Background

## 2.1 ADC Characterization

An analog-to-digital converter (ADC) is used to convert a continuous-time signal to a digital number that represents its discrete amplitude. Any method of digitizing the analog signal introduces some error. The quantization error and ADC nonidealities are discussed in section 2.2. ADC performs the conversion by sampling the real world analog signal periodically. The number of conversions that ADC is needed to convert analog input to the digital code within a specific time is called sampling rate. For example, 100kS/sec ADC collects hundred thousand samples in a second of time.

Resolution of an ADC is the number of output levels of quantizing an analog signal and it is given in powers of 2 as the output of a ADC comes in binary format. A 7-bit ADC represents the analog input using  $2^7$  or 128 quantization levels. ADC needs a reference voltage to digitize the analog signal and divides the reference voltage into small quantization levels. The smallest quantization level that ADC can resolve called the least significant bit (*LSB*) and it is defined as [5]:

$$LSB = \frac{V_{ref}}{2^N} \tag{2.1}$$

For an ADCs with a differential voltage reference LSB is defined as [15]:

$$LSB = \frac{V_{ref(+)} - V_{ref(-)}}{2^N}$$

(2.2)

where  $V_{ref(+)}$  and  $V_{ref(-)}$  are the non-inverting voltage reference and the inverting voltage reference respectively. Full scale of an ADC is defined as:

$$V_{FS} = V_{ref} - 1LSB \tag{2.3}$$

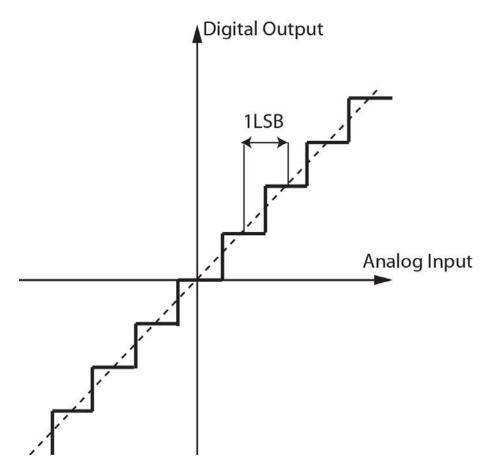

Figure 2.1: Ideal ADC transfer function

Meaning that ADC input can get very close to  $V_{ref}$  but it never reaches its reference voltage [15]. The *LSB* in terms of *FS* using (2.1) and (2.3) is:

$$LSB = \frac{V_{FS}}{2^N - 1}$$

(2.4)

An ideal ADC transfer function is illustrated in Fig 2.1. The Y-axis shows the ADC digital output and X-axis is the analog input. The quantized value of the analog input is represented by the diagonal staircase [16]. The distance between two successive transition points is defined as 1LSB as shown in Fig 2.1.

The ADC is also characterized by its bandwidth and signal-to-noise ratio (SNR). The former is the frequency range that ADC can measure and defines the sampling rate of the ADC; the latter is the ratio of the measured signal to its introduced noise. Accuracy and linearity limit how well the quantizatized output can match the real world signal. The dynamic range of an ADC is specified by its

effective number of bits (ENOB). ENOB is equal to the ADC resolution in an ideal condition. The ideal dynamic range can be defined as the ratio of the full scale input to the smallest quantization level. Assuming most of the input signals are sinusoidal, dynamic range for an ideal N-bit converter can be calculated as [5]:

$$Dynamic Range(dB) \approx 6.02N + 1.76 \tag{2.5}$$

More details on deriving (2.5) are presented in Section 2.2. Further details on using this equation are outlined in [1].

# 2.2 ADC Nonidealities

The ideal ADC has a linear transfer function as shown in Fig 2.1. However, real ADC performance is degraded by several error sources. Quantization, offset, gain, timing and non-linearity are common type of those errors.

#### 2.2.1 Quantization Error

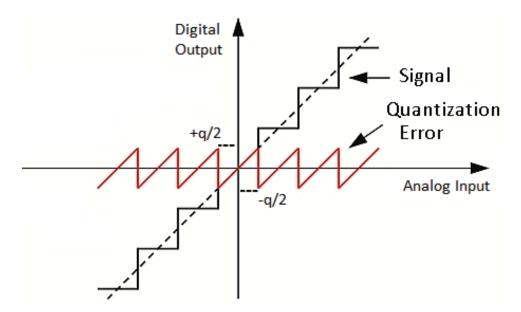

If changes in the input signal applied to the ADC are very small (i1LSB) and cannot be detected by the converter, quantization error is occurred. Fig 2.2 illustrates the quantization error of ideal N-bit ADC. This sawtooth waveform as error signal e(t) is the difference between the analog input signal and the quantized output signal [16]. The maximum error an ideal ADC makes during the conversion is  $\pm \frac{1}{2}$  LSB.

The root-mean-square quantization error is [1]:

$$rms$$

quantization  $error = \sqrt{\overline{e^2(t)}} = \frac{q}{\sqrt{12}}$  (2.6)

From (2.6) and (2.7) the SNR for N-bit ADC can be calculated (assuming a full-scale input sine wave) as:

$$full - scale \ sinewave = v(t) = \frac{q \times 2^N}{2} sin(2\pi ft)$$

(2.7)

...

$$SNR = 20log_{10} \left( \frac{rms \ full - scale \ input \ power}{rms \ quantization \ noise \ power} \right) = 20log_{10} \left( \frac{\frac{q2^N}{2\sqrt{2}}}{\frac{q}{\sqrt{12}}} \right)$$

(2.8)

Figure 2.2: Quantization Error as a function of input voltage [1]

$$SNR = 6.02N + 1.76dB$$

(2.9)

It is important to know that in (2.9) rms quantization error is estimated over the full Nyquist bandwidth, dc to  $\frac{f_s}{2}$  where  $f_s$  is the sampling frequency. If the signal of interest has a smaller bandwidth (BW)or any noise shaping method is used to filter out the noise components, then a correction factor(called process gain) [1] needs to be added to rms quantization error equation. Therefore this correction factor results in increased SNR and we have [1]:

$$SNR = 6.02N + 1.76dB + 10\log_{10}\left(\frac{f_s}{2 \times BW}\right)$$

(2.10)

ENOB can be calculated from (2.9) as:

$$ENOB = \frac{SNR - 1.76 \ dB}{6.02} \tag{2.11}$$

#### 2.2.2 Offset and Gain Error

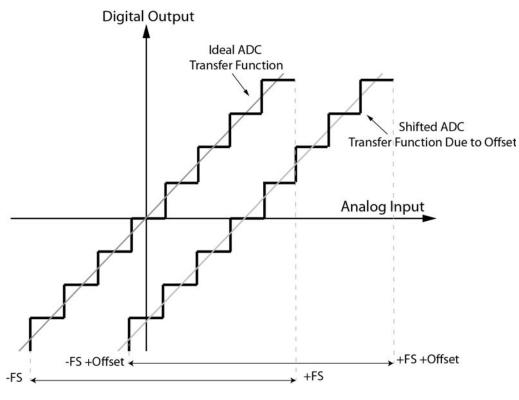

The fixed difference between input and output signals due to device mismatch or other nonidealities of the components of the ADC shifts the transfer function and

Figure 2.3: ADC Offset error

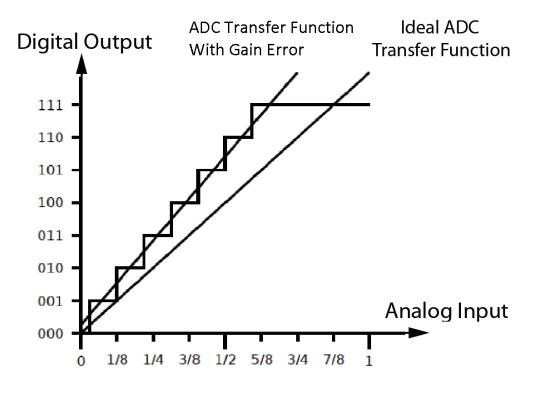

causes offset error. If the slope of the real ADC transfer function varies from the slope of the ideal ADC transfer function, gain error has occured, as typically happens when an on-chip reference is used. In an ideal ADC when the full-scale input is applied the result of the conversion is all ones. In an ADC with gain error, all ones is the result of applying a voltage greater than full-scale (negative gain error) or a voltage less than full-scale (positive gain error). The ADC transfer function with offset and gain errors is shown in Fig.2.3 and 2.4.

Offset and gain errors can be calibrated by shifting the x and y axes of the transfer function to align the zero points of the real and ideal ADC transfer function and that will remove the offset error and then by rotating the transfer function about the new zero point the gain error can be adjusted.

#### 2.2.3 Nonlinearity Error

Integral nonlinearity (INL) and differential nonlinearity (DNL) are two of the accuracy parameters for testing ADC performance. DNL error reveals how far an actual quantization step width is from the ideal value of 1LSB, as in an ideal ADC each quantization step of a converter are spaced exactly 1LSB apart. The distance between an actual step width and the ideal value is measured in a form of a change in input-voltage magnitude and represents in LSB units after removing static gain

Figure 2.4: ADC Gain error

errors, therefore for an ideal ADC DNL is equal to 0LSB. For example, if the input signals increases only  $\frac{7}{8}LSB$  and the output changes levels, the DNL error is  $-\frac{1}{8}LSB$  for this transition. Any DNL error of less than or equal to 1LSB guarantees a monotonic transfer function with no missing codes. If DNL reaches -1LSB, quantization step is skipped and a missing code (is also known as missing-transition levels [17] (MTLs) is occured [1]. Positive DNL values gives rise to wide codes, or missing-decision levels (MDLs). In an ideal case, for every 1LSB interval, only one decision level (transition voltage) exists. Therefore a positive DNL resembles as one or more decision level in the code's input range [17]. Large values of DNL can limit the ADC performance in terms of signal-to-noise ratio (SNR). The DNL for an N-bit ADC is calculated as:

$$DNL[i] = \frac{V_{i+1} - V_i}{V_{LSB-Ideal}} - 1, \quad where \ 0 < i < 2N - 2$$

(2.12)

*i* corresponds to the quantization code level and  $V_{LSB-Ideal}$  is the ideal distance for two adjacent digital codes [1].

Integral nonlinearity (INL) error is defined as the summation of DNL errors and appears as deviation in LSB or percent of full-scale range (FSR) of the real transfer

Figure 2.6: DNL error in a 3-bit ADC with missing Decision Levels

function from a straight line in two forms: "best straight-line INL" and "end-point INL". The former determines the closest linearity approximation to the ADC's actual transfer function and the latter is defined by the position of the all zeros and all ones (full-scale) outputs. Fig 2.5, 2.6 and 2.7 show the DNL and INL error examples for of 3-bit ADC respectively.

Best straight-line INL provides information about offset (intercept) and gain (slope) error, plus the position of the transfer function. It determines, in the form

Figure 2.7: INL error in a 3-bit ADC

of a straight line, the closest approximation to the ADC's actual transfer function. End-point INL passes the straight line through end points of the converter's transfer function, thereby defining a precise position for the line. Thus, the straight line for an N-bit ADC is defined by its zero (all zeros) and its full-scale (all ones) outputs. The best straight-line approach produces lower peak error results and is often preferred [1]. INL for an N-bit ADC is calculated as:

$$INL[k] = \sum_{i=0}^{k} DNL[i] = \frac{V_i - V_{zero}}{V_{LSB-Ideal}} - i, \quad where \ 0 < i < 2N - 1$$

(2.13)

$V_i$  is the analog value corresponding to the digital output code i, N is the ADC resolution,  $V_{zero}$  is the minimum analog input representing the all-zero output code, and  $V_{LSB-Ideal}$  is the ideal distance between two adjacent output codes.

#### 2.2.4 Timing Error

Timing errors also limit ADC performance. Sampling clock jitter, clock skew, and input skew are known as typical timing errors whether from random sources or deterministic sources like clock distribution layout [5].

Sampling clock jitter also known as "aperture jitter" giving rise to sampling-time uncertainty and this error is more significant at the maximum slope of the input signal; meaning that a small  $\Delta t$  change in sampling time while the  $\frac{\Delta V}{\Delta t}$  is large causes a large  $\Delta V$  error. Assuming a sinusoidal input waveform (a full-scale signal  $V_{in}$ ) with input frequency  $f_{in}$  is applied to an N-bit ADC, the maximum slope is at the zero crossing [2,5]:

$$V_{in} = \frac{V_{ref}}{2} sin(2\pi f_{in}t)$$

(2.14)

$$\frac{\Delta V}{\Delta t} \mid_{max} = \pi f_{in} V_{ref} \tag{2.15}$$

If  $\Delta t$  represents the sampling time uncertainty, then in order to keep  $\Delta V$  error less than 1LSB the  $\Delta t$  has a upper bound limitation [2,5], therefore:

$$\Delta t < \frac{1 \, LSB}{\pi f_{in} V_{ref}} = \frac{1}{2^N \pi f_{in}} \tag{2.16}$$

For example, a 7-bit ADC sampling a 200MHz full-scale sinusoidal signal must keeps its aperture jitter under 12 ps to maintain 7-bit accuracy. In order to calculate the signal-to-noise (SNR) ratio affected by jitter-induced noise, we need to calculate the power of  $\Delta V$  error at any point in time. For a sinusoidal input signal  $v(t) = Asin(2\pi f_{in}t)$  the  $\Delta V$  error is:

$$\Delta V(t) = A(2\pi f_{in})\Delta t \ \cos(2\pi f_{in}t) \tag{2.17}$$

The power of the  $\Delta V$  error is calculated as:

$$\langle \Delta V(t)^2 \rangle = \langle [A(2\pi f_{in}) \cos(2\pi f_{in}t)]^2 \rangle \langle \Delta t^2 \rangle = \frac{A^2}{2} (2\pi f_{in})^2 \langle \Delta t^2 \rangle$$

(2.18)

The SNR from jitter-induced noise is expressed as:

$$SNR = \frac{\frac{A^2}{2}}{\frac{A^2}{2}(2\pi f_{in})^2 \langle \Delta t^2 \rangle} = \frac{1}{(2\pi f_{in})^2 \langle \Delta t^2 \rangle}$$

(2.19)

Figure 2.8: Sampling Jitter at different SNR and input frequency [2]

$$SNR_{dB} = -20log_{10}(2\pi f_{in} \langle \Delta t \rangle) or \langle \Delta t \rangle = \frac{10^{\frac{-SNR_{dB}}{20}}}{2\pi f_{in}}$$

(2.20)

This means that for a 200MHz sinusoidal input applied to an ADC, in order to achieve 40dB SNR the aperture jitter must be less than 8 pS. Therefore a low jitter clock is essential to proper ADC performance. Jitter versus the input frequency for a specific SNR is shown in Fig 2.8. As is shown in the figure, at high frequencies in order to achieve large SNR very low jitter clock in the order of ps is needed.

Clock signal path needs careful layout in order to avoid clock skew. Different wiring passes near clock signal wires can affect the capacitance of the clock distribution wires and causes unwanted delays. Random mismatch of transistor devices in buffers on clock signal path can also create clock skew. Input skew happens when input signal arrives with delay to the blocks. For example, in a case of flash ADC design, the input signal to the comparators sees some delay between comparators. Therefore some errors will be associated with the sampled voltage. A front-end sample and hold circuits (at the cost of power consumption and limited input bandwidth) can solve this problem.

## 2.3 Figures of Merit and Performance Trends

When ADCs with different specifications are compared, figure-of-merit (FOM) can combine the various parameters that are important for design [10]. Several FOM has been defined so far [3]:

• Walden FOM

$$FOM_W = \frac{P}{f_s \times 2^{ENOB}} \tag{2.21}$$

• Schreier FOM (DR)

$$FOM_{S-DR} = DR + 10log(\frac{BW}{P})$$

(2.22)

• Schreier FOM (SNDR)

$$FOM_S = SNDR + 10log(\frac{\frac{f_s}{2}}{P})$$

(2.23)

In Fig 2.9, the dashed line shows the schreier FOM which is the borderline for high resolution ADCs [3], in 2014. For low resolution ADCs, it is still appropriate to use the walden FOM (doted line in Fig 2.9) [3].

## 2.4 ADC Architectures

ADCs cover a wide range of resolutions and speed with different architectures. There are two main types of analog-to-digital converters: Nyquist rate and oversampling converters. In Nyquist rate converters like flash and Successive Approximation ADCs, output values have a one-to-one correspondence with input values [5]. However, they are designed to operate at 1.5 to 10 times the input signal Nyquist rate in order to have a reliable anti-aliasing and reconstruction filter [5]. Oversampling data converters such as Delta-Sigma ADC typically operates 20 to 512 times the input signal Nyquist rate. Fig 2.10 shows several ADC architures for different sampling rates and resolutions [4].

Scaling of CMOS IC technology into nanometer area has noticeable improvement in cost, performance, and system integration. Although scaling is very beneficial for digital systems, analog functions are degraded with shrinking the transistor sizes, and analog design is challenging in nanometer technologies. However, the

Figure 2.10: Different ADC architectures comparison [4]

cost advantages of integrating systems with technology scaling has made analog and mixed signal design attractive to the designers yet. In comparison to other types of analog-to-digital converters, the simple analog structure of flash ADCs makes them attractive in the speed-power-complexity trade off in deep submicron CMOS. This work presents a redundant flash ADC using a "Split-ADC" calibration structure and lookup-table-based correction and an ultra low power SAR-ADC design.

#### 2.4.1 Flash ADC Structure

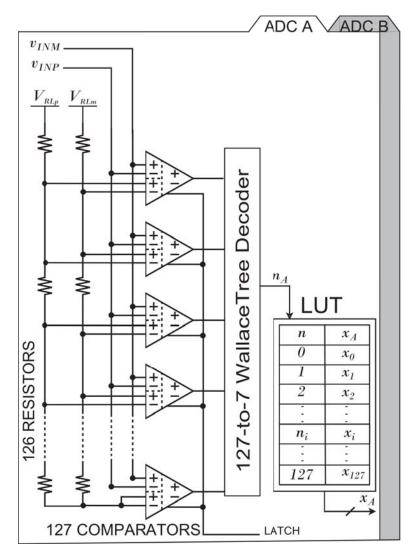

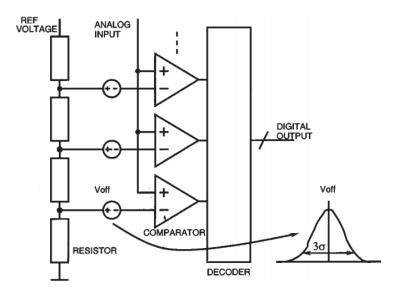

In nanometer scale CMOS high speed low power analog-to-digital converters with high effective number of bits (ENOBs) are in demand. Wireless receivers and high density disk drives are examples of applications that flash ADCs are typically used in [18]. A flash ADC has a simple structure that includes an array of comparators, a resistor ladder in order to generate the reference voltages, and a thermometer-tobinary converter block. Fig 2.11 shows block digram of a simple flash ADC.

The high conversion rate of flash ADC comes at the cost of high number of comparators. A basic flash ADC employs an individual comparator for every quantization level in order to compare an input voltage with a series of reference voltages. For an N-bit flash ADC, typically  $2^N - 1$  comparators are needed. The analog input signal is applied to the negative input of each comparator while the reference voltage coming from a voltage divider resistor ladder is applied to the positive comparator input. The results is a thermometer code output, since all comparators connected to as resistor string will generate a 1 output if the reference voltage is larger than input signal or generate a 0 output if input signal is greater than the related reference voltage. A " $2^N - 1$  to N" digital decoder can convert the thermometer code into a binary weighted output code [5].

Although designing in in a deep submicron process gives us the advantage of higher speed, increasing variation and device mismatch will decrease the ADC effective number of bits (ENOB). Especially in flash ADCs, device mismatch results in offset error in each comparator, affecting differential and integral nonlinearity (DNL and INL) of the ADC and degrading ENOB performance.

#### 2.4.2 Redundant Flash ADC

Redundancy has been shown to be a practical method of yield enhancement in integrated circuit designs [7, 18–20]. In order to reduce the matching problem of transistors, one can increase the device size [14]; however this approach results in increased area and power consumption costs. In flash ADC design, comparator

| Architecture          | Speed       | Accuracy    |

|-----------------------|-------------|-------------|

| Flash                 | High        | Low         |

| SAR                   | Low-Medium  | Medium-High |

| Folding-interpolating | Medium-High | Medium      |

| Delta-Sigma           | Low         | High        |

| Pipeline              | Medium-High | Medium-High |

Table 2.1: Comparison of different ADC Architectures

Figure 2.11: Block diagram of a flash ADC

redundancy tolerates the large comparator offsets due to small device sizes essential to reduce input capacitance and provides the high speed flash ADC with acceptable fan-in.

In a traditional N-bit flash ADC, comparators with monotonically increasing, trip-voltages have the responsibility of quantizing the analog input signal applied to the ADC. In a redundant flash ADC, instead of  $2^N - 1$  comparators, a bank of  $R \times (2^N - 1)$  comparators are used to quantize the input signal; meaning that each code are associated with R comparators [7]. More details on the application of redundant flash ADC are addressed in 2.6.1.

Figure 2.12: SAR ADC architecture

#### 2.4.3 SAR ADC Structure

Successive approximation ADCs are widely used as medium-to-high resolution and medium speed data converters. For high resolution SAR ADCs, fully differential techniques provide the best common mode noise rejection and lowest distortion [21]. For medium resolution ADCs in power-critical applications such as battery management, the lower power consumption of simpler single-ended architectures are attractive.

Unlike the flash ADC in previous section, Successive Approximation Register(SAR) ADC does not use so many comparators for decision making, instead it only has a single comparator that uses a binary search algorithm and a full resolution DAC. Fig 2.12 shows the block diagram of a conventional SAR ADC, consisting of control logic, comparator, and capacitive DAC (CDAC). The sampled analog input voltage is compared with DAC voltage in an iterative process until an analog voltage that is approximately equal to the input voltage is found. A binary weighted capacitor network is used for the DAC architecture in most SAR ADCs since capacitors are better than resistors for device matching [22]. The conversion cycle begins when the Most Significant Bit (MSB) is set to digital value 1 and the rest of the bits are set to zero. The equivalent analog value of this digital code  $\frac{V_{ref}}{2}$  at the output of DAC is compared to original input voltage by the comparator. If the comparison shows the analog output from the DAC is greater than the original sampled input, the MSB will reset to digital value 0 as the comparator output is zero. Otherwise, the MSB is left to 1. The binary search will continue for the rest of the bits and the last digital code of control logic will be the digital representation of the original analog input [23]. Fig 2.13 shows the first three steps of conversion in a single ended SAR ADC. During the sampling mode the top plates of all capacitors are connected to ground and the bottom plates are connected to the input voltage  $V_{in}$ . In the second step which is the "hold mode" the top palates are disconnected from the ground while the bottom plates are connected to ground and due to the charge

Figure 2.13: A 4-bit charge-redistribution SAR ADC [5]

conservation, the top plates voltage will be  $-V_{in}$ . In bit cycling step, the bottom plate of the largest capacitor is connected to the reference voltage  $V_{ref}$ . This makes

the negative input to the comparator  $(V_x)$  increase by  $\frac{V_{ref}}{2}$  as:

$$V_x = -V_{in} + \frac{V_{ref}}{2} \tag{2.24}$$

if the  $(V_x) < 0$  which corresponds to  $V_{in} > \frac{V_{ref}}{2}$ , the comparator output will set the MSB to logic 1; otherwise the MSB will be reset to 0 which means the capacitor corresponding to the MSB will be grounded again. To determine the next bit, the next largest capacitor is connected to  $V_{ref}$  and the related  $(V_x)$  will increase by  $\frac{V_{ref}}{4}$ . This procedure is repeated until all of the bits are determined [23].

# 2.5 Calibration Techniques Overview

#### 2.5.1 Flash ADC Calibration

Most calibration methods of flash ADCs are designed to correct the comparator offsets which can be due to device mismatch inherent in the design [5]. Variations in resistors value due to random mismatch along the reference ladder, temperature variation or the variation in polysilicon thickness in polysilicon resistors can cause error in reference voltages [2]. However, this error is not significant in flash ADC design with less than 10 bit resolution [2]. Any input offset voltage of comparators can lead to a shift in flash ADC's linear transfer function and cause an nonlinearity. Several foreground and background calibration methods have been proposed in literature to deal with comparator's offset in flash ADC design. Some of these methods are:

- Auto-Zeroing: This method helps to reduce the offset of preamplifiers and comparators by sampling the unwanted offset voltage and then subtracting the amount of offset voltage from the input or output of the preamplifier [24].

- Averaging, Interpolation, and Folding: Averaging method connects the outputs of the preamplifier array of comparators with resistors and thus effectively averages the offset of the central preamplifier with its neighbors and will improve the DNL/INL [25].

Interpolation produces voltages that are in between two other voltages and thus a new reference voltage will be created (interpolation factor of 2). This method can reduce the number of preamplifiers required which is also beneficial in terms of input capacitance of flash ADC, power and area [5].

Folding method also reduces the number of comparators needed in flash ADC design by generating multiple zero crossing for each comparators [5, 26].

• Redundancy: Redundancy is the technique that deliberately uses an excess of "cheap and imprecise comparators [27], selects the best ones, and deactivates the others. More detail is explained in 2.6.1.

- Digitally controlled and DAC based calibration: Digital calibration of the comparators is usually applied in the DAC. Input-referred offset of the comparators is controlled with extra circuitry, which increases the power consumption and area of ADC [28].

- Stochastic ADC: Random distribution of comparator offsets is used to create reference voltages, and the ADC output is the sum of the comparator outputs [29]. The cumulative distribution function (CDF) of the comparator offset will generate the flash ADC transfer function [29]. More detail is explained in 2.6.1.

### 2.5.2 SAR ADC Calibration

Calibration methods of the SAR converters are mostly aimed to correct the errors of DAC due to capacitive mismatch inside the capacitor network which is one of the primary sources of power dissipation in this type of ADC. Some of these methods are:

- Capacitor Splitting: In this method the MSB capacitor splits into two capacitors of value  $C_0$ , and then switches down one of them when it is needed. Thus, the capacitor splitting approach uses the same energy for an up and a down transition [30].

- Redundancy: Redundancy in the search algorithm that is used in typical SAR ADCs can relax the settling constraints to a tolerable error corresponding to the step size. Inaccurate decisions in early conversion steps are tolerated and corrected afterward [31].

- DAC trimming: Some matching techniques (such as dummy capacitor placement) are used to improve matching [32]. Some level of reference trimming also can be used to trim the voltage reference that is applied to capacitor network.

Among these methods of calibrations that have been explained in this chapter, split ADC calibration is known as a promising method of calibration for improving the ADC nonlinearities which is explained in more detail in 2.5.3.

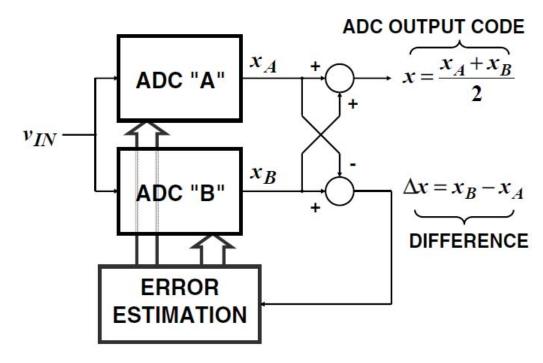

#### 2.5.3 The Split ADC Structure

Fig.2.14 shows the split ADC concept [6,33]. The ADC is split into two channels. The same input is applied to both channels and individual output codes  $x_A$  and  $x_B$  are produced by each ADC. The ADC output code x is the average of the output of the two channels.

The background calibration signal is derived from the difference  $\Delta x$  between two output codes  $x_A$  and  $x_B$ . If both ADCs are precisely calibrated, the two outputs agree and the difference  $\Delta x$  is zero; otherwise if  $\Delta x$  is a nonzero value, calibration parameters in each ADC are adjusted until  $\Delta x$  and the ADC errors approaches to zero.

# 2.6 Previous Works

#### 2.6.1 Flash ADC Research

Comparator offset has been a significant problem for flash ADC design and so far several methods has been proposed in literature to deal with it. Auto-zeroing, averaging, redundancy, DAC-based calibration, digitally controlled trimming and stochastic ADCs are the known techniques to mitigate the effects of comparator offsets. Among all methods, digital calibration was a promising method which results in less FOM (Figure-of-Merit). Table 2.2 outlines various calibration methods and design of flash ADCs published in the IEEE International Solid-State Circuits Conference (ISSCC), IEEE Journal of Solid-State Circuits (JSSC), IEEE Custom Integrated Circuits Conference (CICC), IEEE Symposium on VLSI Circuits (VLSI) and IEEE Asian Solid-State Circuits Conference (A-SSCC). In this table, calibration techniques, the sampling rate, the power, the effective number-of-bits (ENOB), and the resolution of different flash ADC structure in different process technology are

Figure 2.14: Split ADC Architecture [6]

|         | Cod | e                       | Code <sub>6a</sub>                                                    |

|---------|-----|-------------------------|-----------------------------------------------------------------------|

| •       | 6   | _6a 6b _ 6c _           |                                                                       |

|         | 5   | _5a 5b 5∈ _             | 5 - 5a - 6b - 5c - 5                    |

| Je.     |     | -4a— — 4b- — 4€ -       | e 4 <u>3a</u> <u>4b</u> <u>3c</u>                                     |

| Voltage |     | -3a 3b - 3€ -           | $\frac{1}{2a}$ 3 $-\frac{4a}{2a}$ $-\frac{3b}{2b}$ $-\frac{4c}{4c}$ - |

| %       | 2   | -2a 2b - 2c -           | $2 2\epsilon -$                                                       |

| Trip    |     | -1a 1 <del>b</del> 1c - | 'Ē <sup>1</sup> - <u>1</u> īa 26                                      |

|         |     |                         |                                                                       |

(a) Nominal Comparator Trip Voltages

(b) Actual Comparator Trip Voltages

Figure 2.15: The basic principle of redundancy method [7]. Selected comparators are highlighted.

compared.

Among the papers listed in Table 2.2 [19, 34, 35], use a redundancy calibration method. Redundancy is a technique that deliberately uses excess of "cheap and imprecise comparators [27], selects the best ones, and deactivates the others. In case of flash ADC, the identical redundant comparators are spread over the reference voltages and since the offset of comparators span over 1LSB, there will be a chance of overlapping probability distribution functions (PDFs) of the comparator offsets which is good for comparator reassignment. Instead of  $2^N - 1$  comparators, a bank of  $R \times (2^N - 1)$  comparators are used to quantize the input signal; meaning that each code are associated with R comparators [7] and a calibration engine [7] will select the best comparator for each code. The basic principle of redundancy method for flash ADC is depicted in Fig 2.15a and 2.15b. In this case, redundancy factor, R is equal to 3. Nominal trip voltages of the group of R comparators for each code is shown in Fig 2.15a. These are the ideal trip points. In reality, the actual trip points are comparators are different from the ones in this figure and they are shown in Fig 2.15b. The trip voltage of the most suitable comparators for each code is highlighted in this figure. For example, comparator 5b is reassigned to designate the code 6. The comparators which are not assigned to any code are disabled to save on power consumption. A problem with this method is the large area cost of disabled comparators. Another difficulty with selection requirement in redundancy method is the "edge effects" [7] which can reduce yield. One can add extra comparators to recover the selection of suitable comparators at lowest and highest codes.

Large capacitive loading is a big challenge in designing a fast sample and hold for a high speed flash [36]. In [36] a two stage track and hold (T/H) is used, while the second stage works as a buffer between the first stage and the capacitive loading of comparators. With clock duty cycle control SNDR improves. However, the extra T/H stage implies extra power consumption and extra area. In [29, 40] a large number of comparators are used in parallel, while removing the reference ladder from the ADC structure and providing the trip points with random offsets. A statistical selection technique is used as a redundancy method to deal variation in comparator offset. This scheme limits the ADC resolution and also consumes a large

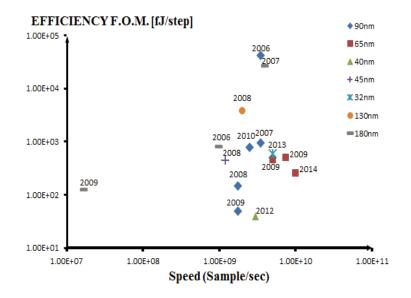

Figure 2.16: Survey of Flash ADCs.

area and any changes in trip points due to temperature drift require recalibration for proper ADC operation [18].

In [25, 39, 42, 46] resistive averaging is used to lower the impact of offset. Speed and linearity is improved with interpolation in [41,43]. In [26] interpolation is used in a folding flash structure and foreground offset calibration is expanded to use digitally controlled DACs for folding-interpolating stages. In [44], analog input is sampled and rectified by a 1-bit folding stage and a 4-bit flash sub-converter converts the folding signal. The nonlinearity of the folding stage is calibrated using additional input pairs in comparators. The combination of a simple folding technique with DAC-based comparator calibration seems to be very practical in reducing the flash ADCs power. In [47]a dynamic technique is used that adds binary-scaled variable capacitors at the drain node of input pair of dynamic comparators. DAC-based calibration has been used in [48–50]. Fig 2.16 plots the reported efficiency FOM as a function of speed in (GS/s). It is evident that recent designs have a wide performance range (20 MS/s to tens of GS/s) and achieve good power-efficiency in high speed conversion.

#### 2.6.2 SAR ADC Research

In recent years, there has been a significant progress in designing energy efficient SAR ADCs. Recent ADC surveys [51] show the conversion speed and power consumption of SAR ADCs have dramatically improved. Process scaling is beneficial for this type of ADC that uses MOS switches, digital logic and capacitance network. Table 2.3 outlines various SAR ADC designs in recent years.

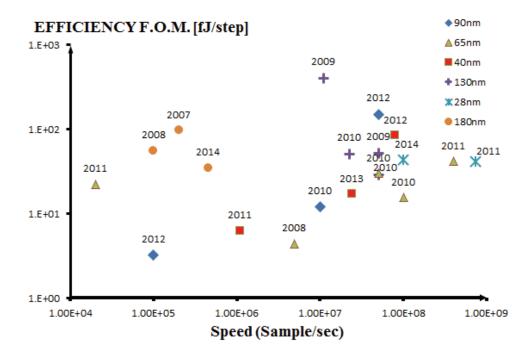

This survey show there has been significant improvement in capacitive DAC

Figure 2.17: Survey of SAR ADCs.

switching energy. Monotonic switching [63], capacitance splitting [30] and arbitrary weight capacitor array [67] has been the promising methods of energy saving in SAR ADC design. Eliminating the MSB capacitance switching [63], using a separate coarse-ADC to calculate the MSBs, dual supply ADC that uses lower supply voltage for power hungry digital portion of ADC and taking the advantage of unary-wighted DAC [59] are some of the energy efficient design schemes that has been proposed in recent years. Fig 2.17 shows a plot of Walden efficiency FOM vs. conversion speed for SAR ADCs in 28nm, 40nm, 65nm, 90nm, 130nm, 180nm process nodes from 2007 to 2014. As it comes from the graph, recent designs that has conversion speed < 100MS/s benefits from process scaling and reports better efficiency FOM.

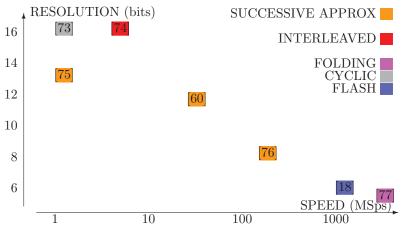

#### 2.6.3 Split ADC Research

The "Split ADC" was originally developed by my advisor Professor John A. McNeill with collaborators Coln and Larrivee from Analog Devices [73, 78, 79]; a similar technique was developed independently by Moon and Li at Oregon State [80]. An indication impact of this technique is the broad range of published work using the Split ADC approach developed by other investigators. While the original work [73, 78, 79] was for an algorithmic (cyclic) ADC architecture, work has also been published applying the split ADC concept to architectures such as flash [18], folding [77], interleaved [74, 81], and SAR [60, 75, 76, 82] ADCs. For work with numerical results, Fig 2.18 shows the speed and resolution reported. Over a broad

Figure 2.18: Survey of ADCs using "Split ADC" approach.

range of the speed-resolution-architecture ADC trade off space, there are examples in the literature in which the "split ADC" approach enables fast digital background self-calibration. This will enable drastically improved power efficiency by moving all calibration and correction into the digital domain, allowing flash ADCs (first part of this dissertation) to fully realize the promise of nanometer scaled CMOS while avoiding the performance trade offs and disadvantages of the calibration techniques described in 2.6.1.

# 2.7 Summary

ADC characterization and different ADC architectures were explained in this chapter. An overview of ADC calibration for flash and SAR ADC were presented and split ADC structure was explained. A brief literature review of flash, SAR and split ADC were presented.

| Reference | Technology (nm) | Sampling-                               | Calibration              | Resolution | ENOB  | Power   | FOM                     |

|-----------|-----------------|-----------------------------------------|--------------------------|------------|-------|---------|-------------------------|

|           |                 | Rates                                   | Calibration              | (bits)     | LIVOD | (mW)    | (pJ/-                   |

|           |                 |                                         |                          | ()         |       | ( )     | conv)                   |

| [19]      | 180             | 2KS/s                                   | Redundancy               | 6          | 5.05  | 0.00166 | 0.125                   |

|           |                 | to 17.5                                 |                          | -          |       |         |                         |

|           |                 | MS/s                                    |                          |            |       |         |                         |

| [34]      | 180             | 4GS/s                                   | Redundancy               | 4          | 3.48  | 608     | 27                      |

|           |                 |                                         | and DAC-                 |            |       |         |                         |

|           |                 |                                         | controlled               |            |       |         |                         |

|           |                 |                                         | trimming                 |            |       |         |                         |

| [35]      | 90              | 2.5  GS/s                               | Comparator               | 4          | 4     | 30.2    | 0.79                    |

|           |                 |                                         | reassignment             |            |       |         |                         |

| [36]      | 65              | $7.5 \mathrm{~GS/s}$                    | clock duty-              | 4.5        | 3.8   | 52      | 0.497                   |

|           |                 |                                         | cycle control            |            |       |         |                         |

| [37]      | 180             | 18 MS/s                                 | Stochastic               | 6          | 4.9   | 0.631   | N/A                     |

|           |                 |                                         | ADC                      |            |       |         |                         |

| [38]      | 90              | $3.5 \mathrm{GS/s}$                     | voltage                  | 5          | 3.6   | 227     | 42                      |

|           |                 |                                         | trimable                 |            |       |         |                         |

|           |                 |                                         | offset-                  |            |       |         |                         |

|           |                 |                                         | canceling                |            |       |         |                         |

|           |                 |                                         | buffer                   |            |       |         |                         |

| [39]      | 90              | $3.5 \mathrm{GS/s}$                     | Averaging                | 6          | 5.19  | 98      | 0.95                    |

|           |                 |                                         | and Interpo-             |            |       |         |                         |

| [ ( 0 ]   |                 |                                         | lation                   | 27/1       |       |         | 27/4                    |

| [40]      | 90              | 210MS/s                                 | Stochastic               | N/A        | 5.9   | 34.8    | N/A                     |

| [05]      | 250             | 1.900/                                  | ADC                      | 6          | 5.0   | 500     | NT / A                  |

| [25]      | 350             | $1.3 \mathrm{GS/s}$                     | resistive av-            | 0          | 5.3   | 500     | N/A                     |

| [41]      | 45              | 1.2GS/s                                 | eraging<br>Interpolation | 6          | 5.7   | 28.5    | 0.45                    |

| [41] [42] | 65              | $\frac{1.2 \text{GS/s}}{5 \text{GS/s}}$ | resistive av-            | 6          | 5.1   | 320     | 0.45<br>N/A             |

| [42]      | 00              | 003/5                                   | eraging                  | 0          | 0.1   | 320     | $\mathbf{N}/\mathbf{A}$ |

| [43]      | 180             | 24GS/s                                  | Interpolation            | 5          | 4.4   | 3300    | 11                      |

| [45]      | 180             | 1GS/s                                   | Folding                  | 10         | 9.1   | 1260    | N/A                     |

| [20]      | 90              | 1.75GS/s                                | Folding and              | 5          | 4.7   | 2.2     | 0.05                    |

|           |                 | 1.1000/8                                | DAC calibra-             |            | 1.1   |         | 0.00                    |

|           |                 |                                         | tion                     |            |       |         |                         |

| [45]      | 32              | 5GS/s                                   | Dynamic-                 | 6          | 5.1   | 8.5     | 0.594                   |

|           |                 |                                         | offset cali-             |            |       |         | 5.001                   |

|           |                 |                                         | bration                  |            |       |         |                         |

| [28]      | 40              | 3GS/s                                   | digital offset           | 6          | 5.1   | 11      | 0.040                   |

|           |                 | /                                       | trim                     |            |       |         |                         |

| [46]      | 180             | $1.6 \mathrm{GS/s}$                     | resistive av-            | 6          | 5.7   | 328     | N/A                     |

|           |                 | ,                                       | eraging                  |            |       |         | ,                       |

| [47]      | 180             | 1GS/s                                   | Threshold                | 4          | 3.6   | 10.6    | 0.8                     |

|           |                 | ,                                       | Calibration              |            |       |         |                         |

| [48]      | 90              | 1.75GS/s                                | DAC-based                | 5          | 4.7   | 2.2     | 0.05                    |

|           |                 |                                         | Calibration              |            |       |         |                         |

| [49]      | 65              | 800MS/s                                 | DAC-based                | 6          | 5.63  | 12      | 0.40                    |

|           |                 |                                         | Calibration              |            |       |         |                         |

| [50]      | 130             | $3.5 \mathrm{GS/s}$                     | DAC-based                | 6          | 5.11  | 170     | 3.79                    |

|           |                 |                                         | Calibration              |            |       |         |                         |

Table 2.2: Comparison of different flash ADCs in previous works

| Reference | Technology | Sampling             | Resolution | ENOB  | Power (mW) | FOM   |

|-----------|------------|----------------------|------------|-------|------------|-------|

|           |            | Rates                | (bits)     |       |            | (fJ/- |

|           |            |                      |            |       |            | conv) |

| [52]      | 180nm      | $200 \mathrm{KS/s}$  | 8          | 7.31  | 0.00615    | 97    |

| [53]      | 90nm       | 10 MS/s              | 8          | 7.7   | 0.0263     | 12    |

| [54]      | 65nm       | $4.9 \mathrm{MS/s}$  | 10         | 8     | 0.0019     | 4.4   |

| [55]      | 180nm      | $100 \mathrm{KS/s}$  | 10         | 9.4   | 0.0038     | 56    |

| [56]      | 130nm      | 50 MS/s              | 10         | 8.48  | 0.92       | 52    |

| [57]      | 90nm       | 50 MS/s              | 6          | 5.02  | 0.24       | 150   |

| [58]      | 130nm      | 11 MS/s              | 12         | 10.46 | 3.57       | 400   |