#### Lookup-Table-Based Background Linearization for VCO-Based ADCs

by

Long Pham

A Thesis

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Master of Science

in

Electrical and Computer Engineering

by

May 2015

APPROVED:

Professor John A. McNeill, Major Thesis Advisor

himm

Professor Thomas Eisenbarth, ECE Department, WPI

#### Abstract

Scaling of CMOS to nanometer dimensions has enabled dramatic improvement in digital power efficiency, with lower  $V_{DD}$  supply voltage and decreased power consumption for logic functions. However, most traditionally prevalent ADC architectures are not well suited to the lower  $V_{DD}$  environment. The improvement in time resolution enabled by increased digital speeds naturally drives design toward time-domain architectures such as voltage-controlled-oscillator (VCO) based ADCs. The major obstacle in the VCO-based technique is linearizing the VCO voltage-tofrequency characteristic. Achieving signal-to-noise (SNR) performance better than -40dB requires some form of calibration, which can be realized by analog or digital techniques, or some combination [1, 2, 9]. A further challenge is implementing calibration without degrading energy efficiency performance. This thesis project discusses a complete design of a 10 bit three stage ring VCO-based ADC. A lookuptable (LUT) digital correction technique enabled by the "Split ADC" calibration approach is presented suitable for linearization of the ADC. An improvement in the calibration algorithm compared to [1, 2] is introduced to ensures LUT continuity. Measured results for a 10 bit 48.8-kSps ADC show INL improvement of  $\approx 10X$  after calibration convergence.

#### Acknowledgements

I would like to express the deepest appreciation to my thesis advisor, Professor John McNeill, for giving me the opportunity to work with him. He has been the most inspiring and motivating advisor I have had in my life. His understanding, wisdom, guidance and encouragement has pushed me further than I thought I could go in this project.

I would also like to thank Jianping Gong, PhD student in the NECAMSID lab, for discussing the project with me and for making my experience at the lab more fun and exciting. Also to Sulin Li who supported my idea and is continuing to further explore the topic of my project.

Thanks also to Robert Boisse for teaching me how to do the surface mount soldering. Without his help, the printed circuit board would have not been completed.

Last but not least, I want to thank my family, my girl friend and my roommates for helping me survive all the stress in my college life and not letting me give up.

## Contents

| 1 | Intr       | oduction                                      | 1  |  |  |  |

|---|------------|-----------------------------------------------|----|--|--|--|

|   | 1.1        | Goals and Motivation                          | 1  |  |  |  |

|   | 1.2        | Organization                                  | 2  |  |  |  |

| 2 | Background |                                               |    |  |  |  |

|   | 2.1        | Analog to Digital Converter (ADC)             | 4  |  |  |  |

|   |            | 2.1.1 Ideal ADC Characteristics               | 5  |  |  |  |

|   |            | 2.1.2 Static Errors                           | 6  |  |  |  |

|   |            | 2.1.3 Dynamic Errors                          | 10 |  |  |  |

|   | 2.2        | VCO-Based ADCs                                | 11 |  |  |  |

|   |            | 2.2.1 VCO-Based-ADC Architecture              | 11 |  |  |  |

|   |            | 2.2.2 VCO-Based ADC Properties                | .3 |  |  |  |

|   |            | 2.2.3 VCO-Based ADC Nonideality               | 5  |  |  |  |

|   | 2.3        | VCO architectures                             | 16 |  |  |  |

| 3 | Bac        | ground Calibration and Correction Technique 1 | 9  |  |  |  |

|   | 3.1        | Lookup-Table Linearity Correction             | 19 |  |  |  |

|   | 3.2        | Dithered Split-ADC Calibration Concept        | 23 |  |  |  |

|   |            | 3.2.1 ADC Characteristic Alignment            | 25 |  |  |  |

|   |            | 3.2.2 Slope Calibration                       | 27 |  |  |  |

|                                |     | 3.2.3                            | Error Estimation                                 | 28 |  |  |

|--------------------------------|-----|----------------------------------|--------------------------------------------------|----|--|--|

|                                |     | 3.2.4                            | Iterative Matrix Solution                        | 31 |  |  |

|                                |     | 3.2.5                            | Limited Signal Range and "Stitching", Estimation | 34 |  |  |

|                                |     | 3.2.6                            | Offset Consideration                             | 36 |  |  |

|                                | 3.3 | Calibr                           | ration Algorithm Summary                         | 37 |  |  |

| 4                              | Ana | alog Ci                          | ircuit and PCB Implementation                    | 39 |  |  |

|                                | 4.1 | Ring V                           | VCO                                              | 39 |  |  |

|                                | 4.2 | Freque                           | ency Divider                                     | 43 |  |  |

|                                | 4.3 | PCB I                            | Design Summary                                   | 45 |  |  |

| 5                              | FPG | GA Im                            | plementation                                     | 47 |  |  |

|                                | 5.1 | Top L                            | evel Block Diagram Design                        | 47 |  |  |

|                                | 5.2 | Clock                            | Signal Generator                                 | 49 |  |  |

|                                | 5.3 | Dither                           | Generator                                        | 53 |  |  |

|                                | 5.4 | Count                            | er                                               | 55 |  |  |

|                                | 5.5 | Calibration and Correction Block |                                                  |    |  |  |

|                                |     | 5.5.1                            | LUT and Error Matrix Implementation              | 56 |  |  |

|                                |     | 5.5.2                            | Conversion Based Calculations                    | 59 |  |  |

|                                |     | 5.5.3                            | Ensemble Based Calculations                      | 61 |  |  |

|                                | 5.6 | SRAM                             | ¶ Controller                                     | 64 |  |  |

| 6                              | Res | ults                             |                                                  | 66 |  |  |

|                                | 6.1 | Offline                          | e LUT Calibration                                | 66 |  |  |

| 6.2 Background LUT Calibration |     | round LUT Calibration            | 71                                               |    |  |  |

|                                |     | 6.2.1                            | DC Linearity                                     | 72 |  |  |

|                                |     | 6.2.2                            | LMS Convergence Investigation                    | 73 |  |  |

|                                |     | 6.2.3                            | Divergence in LMS loop                           | 74 |  |  |

| 7            | Conclusions    |                                    |    |  |

|--------------|----------------|------------------------------------|----|--|

|              | 7.1            | Future work                        | 80 |  |

| $\mathbf{A}$ | A Verilog Code |                                    |    |  |

|              | A.1            | CLOCK GENERATOR block              | 83 |  |

|              | A.2            | MEMORY CONTROLER block             | 84 |  |

|              | A.3            | CALIBRATION block                  | 85 |  |

| В            | MATLAB Code    |                                    |    |  |

|              | B.1            | Offline LUT linearization          | 92 |  |

|              | B.2            | Linearity test                     | 93 |  |

|              | В.3            | Offline calibration linearity test | 93 |  |

# List of Figures

| 2.1  | ADC Input and Output Definitions                                 | 5  |

|------|------------------------------------------------------------------|----|

| 2.2  | Ideal ADC Transfer Function and Quantization Noise               | 5  |

| 2.3  | Nonlinear Static Errors in Nonideal ADCs                         | 8  |

| 2.4  | Histogram testing of a 4 bit ADC                                 | 9  |

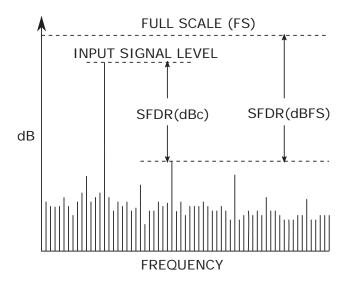

| 2.5  | Spurious Free Dynamic Range                                      | 11 |

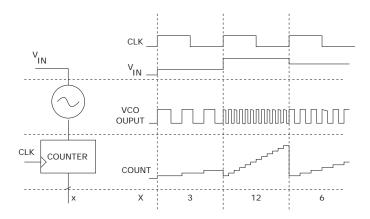

| 2.6  | Simplified VCO-Based ADC                                         | 12 |

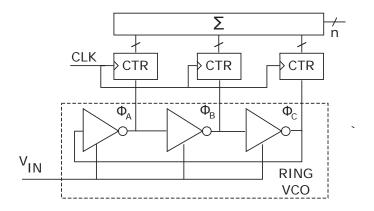

| 2.7  | Multi-phase VCO-Based ADC Architecture                           | 13 |

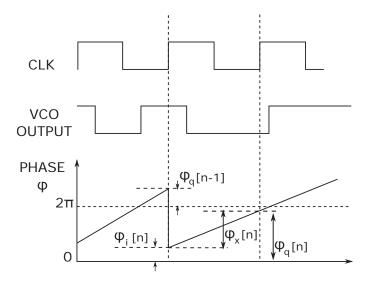

| 2.8  | Quantization of phase in VCO-based ADC                           | 14 |

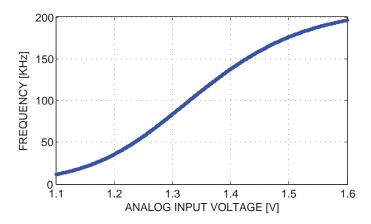

| 2.9  | A 3-stage VCO voltage-to-frequency characteristic                | 15 |

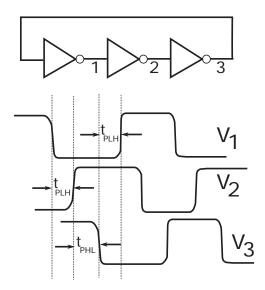

| 2.10 | Waveforms of a three stage single ended ring VCO                 | 16 |

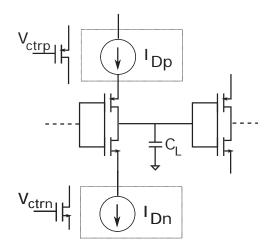

| 2.11 | Simplified Current Starved VCO                                   | 17 |

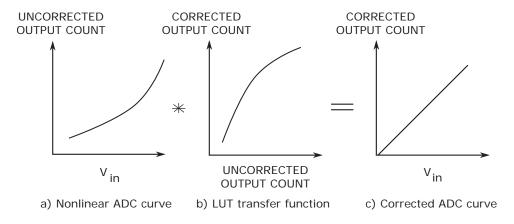

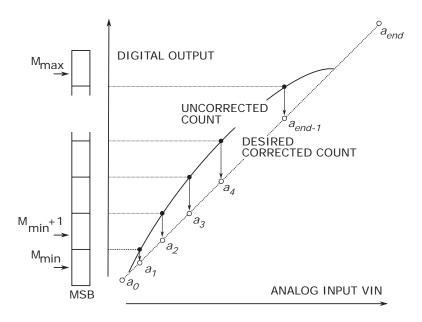

| 3.1  | Transfer functions of nonlinear ADC with LUT correction $\dots$  | 20 |

| 3.2  | Lookup table with linear interpolation digital correction        | 21 |

| 3.3  | Missing codes in LUT implementation                              | 22 |

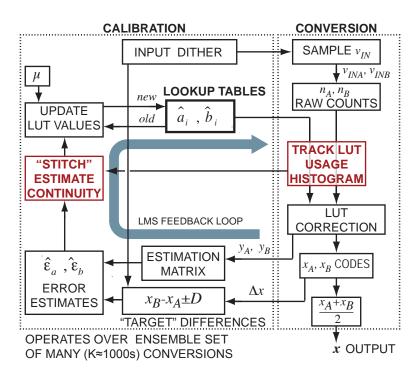

| 3.4  | Dithered Split ADC system block diagram                          | 24 |

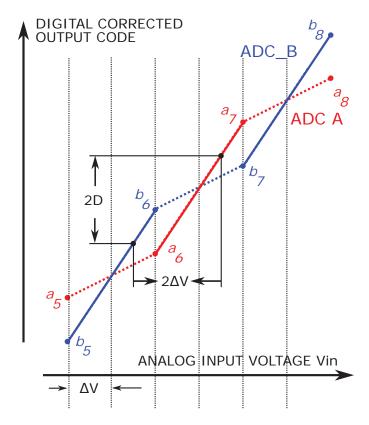

| 3.5  | Split ADC characteristic alignment                               | 25 |

| 3.6  | Split ADC Characteristic alignment with two agreeing but equally |    |

|      | nonlinear ADC characteristics                                    | 26 |

| 3 7  | Slope Calibration                                                | 28 |

| 3.8  | Error estimation depends on distance of the LUT locations to the  |    |

|------|-------------------------------------------------------------------|----|

|      | input count $\ldots$                                              | 33 |

| 3.9  | Example for portions of input range not covered by signal         | 35 |

| 3.10 | Calibration algorithm flow chart                                  | 37 |

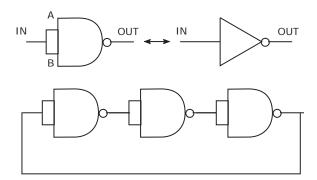

| 4.1  | Simple ring oscillator implemented by NAND gate                   | 40 |

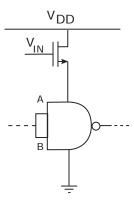

| 4.2  | Using MOSFET to control the delay of the inverter                 | 41 |

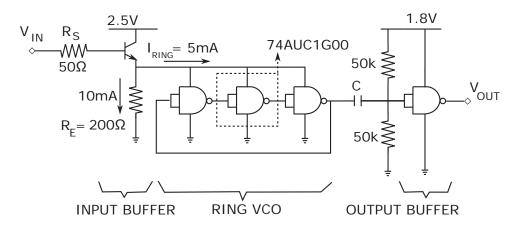

| 4.3  | Ring VCO schematics                                               | 42 |

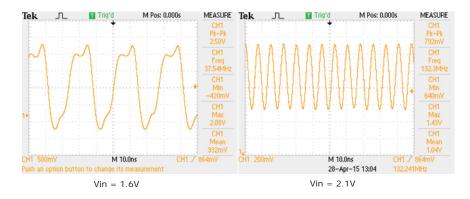

| 4.4  | VCO output waveform for 1.6V and 2.1V input voltage               | 42 |

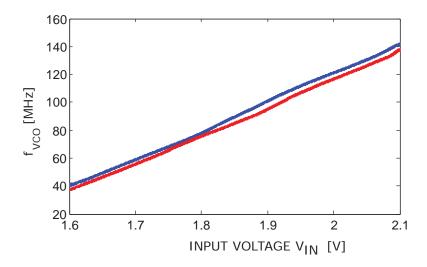

| 4.5  | VCO V-to-f characteristic                                         | 43 |

| 4.6  | Ripple counter circuit schematic                                  | 44 |

| 4.7  | Timing diagram of VCO_GATE signal                                 | 44 |

| 4.8  | PCB block diagram                                                 | 45 |

| 5.1  | Simplified top level block diagram for FPGA implementation        | 48 |

| 5.2  | GPIO input, output configuration                                  | 49 |

| 5.3  | GPIO input, output configuration                                  | 50 |

| 5.4  | GPIO input, output configuration                                  | 51 |

| 5.5  | Converting gated clocks to clock enables to eliminate clock skews | 52 |

| 5.6  | PRN GENERATOR block                                               | 53 |

| 5.7  | Pseudo-random signal timing diagram                               | 54 |

| 5.8  | Pseudo-random signal timing diagram                               | 55 |

| 5.9  | Counter Block                                                     | 56 |

| 5.10 | Calibration and Correction Block                                  | 57 |

| 5.11 | Code and synthesized digital circuit for LUT implementation       | 58 |

| 5.12 | Synthesized digital circuit for the correction block              | 59 |

| 5.13 | Synthesized digital circuit for the correction block              | 60 |

| 5.14 | Ensemble based clock signals                                          | 61 |

|------|-----------------------------------------------------------------------|----|

| 5.15 | Block diagram to realize the "stitching" algorithm                    | 62 |

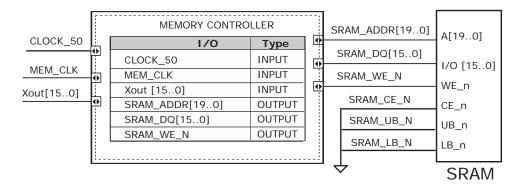

| 5.16 | MEMORY CONTROLLER block                                               | 64 |

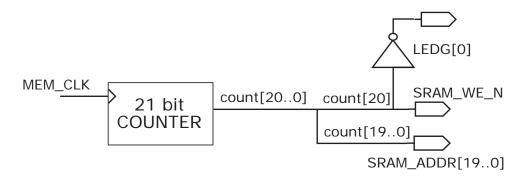

| 5.17 | Digital circuit implementation controlling the address and write en-  |    |

|      | able signal of the SRAM                                               | 65 |

| 6.1  | Offline calibration technique to estimate LUT coefficients            | 67 |

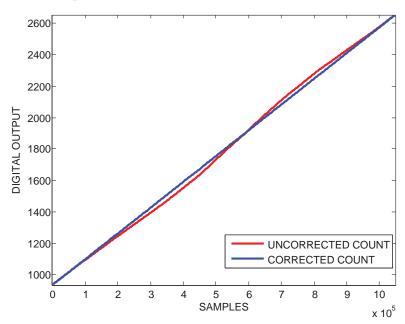

| 6.2  | Raw output count and corrected output count using offline calibration | 68 |

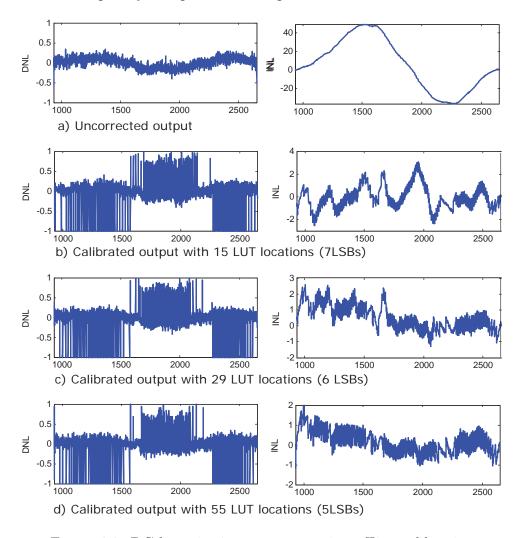

| 6.3  | DC linearity improvement using offline calibration                    | 69 |

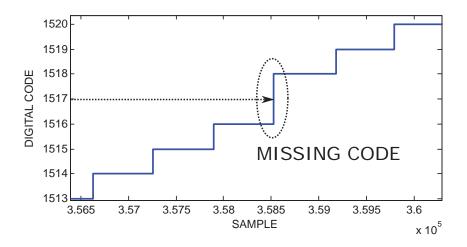

| 6.4  | Missing code at the calibrated output                                 | 70 |

| 6.5  | Introducing $R=2$ reduces DC linearity by factor of $2$               | 71 |

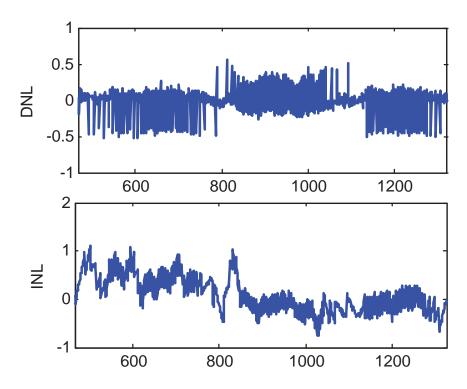

| 6.6  | Digital output of a full-scale triangle wave input                    | 72 |

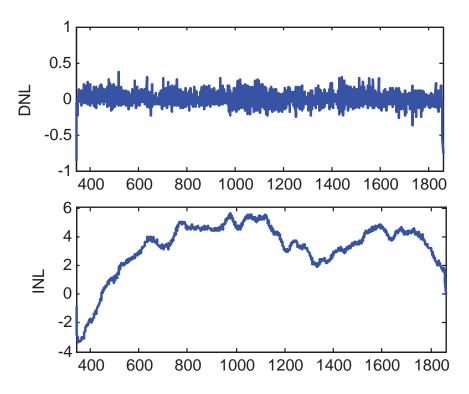

| 6.7  | DC linearity error of the background calibrated output                | 73 |

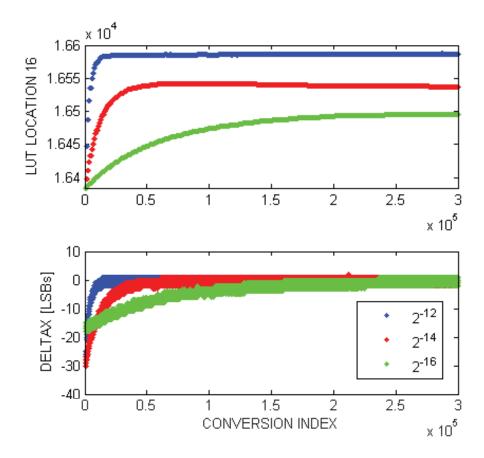

| 6.8  | LUT convergence for different parameter $\mu$                         | 74 |

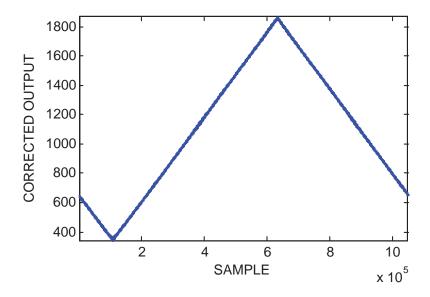

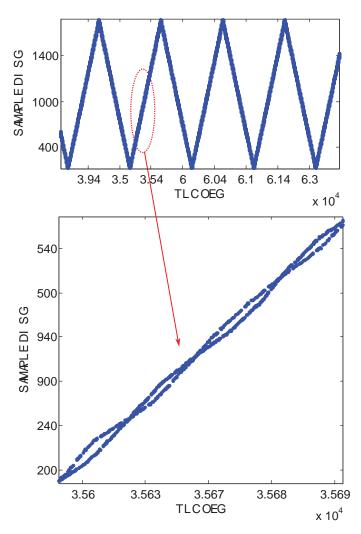

| 6.9  | Digital output of the triangle wave input when the algorithm diverges | 75 |

| 6 10 | Digital output of two channels when the algorithm diverges            | 77 |

# List of Tables

| 7.1 | VCO-based ADC System Parameters /       | Results           | s | 79 |

|-----|-----------------------------------------|-------------------|---|----|

| –   | , , , , , , , , , , , , , , , , , , , , | _ 0 0 10 02_ 0 10 |   |    |

## Chapter 1

## Introduction

#### 1.1 Goals and Motivation

The analog-to-digital converter (ADC) plays an important role as a bridge between the inherently analog world and ever-increasing digital processing world. Ultra-low-power ADCs are needed in systems constrained by battery power or scavenged energy limits in applications such as wireless communication, autonomously powered sensing and monitoring nodes, or implanted biomedical devices for assistive technology. The ADC energy efficiency expressed by the fJ/step figure-of-merit is a critical design system driver in power-constrained applications. When pushing for increasing data rates there is a corresponding increase in the demands of bandwidth and power dissipation [4].

The advance in CMOS technologies has dramatically improved the performance of general purpose processors and digital signal processors. However, most traditionally prevalent ADC architectures have not been able to utilize the process scaling to the same extent, suffering from reduced voltage headroom and reduced analog gain. The improvement in time resolution enabled by increased digital speeds naturally

drives design toward time-domain architectures such as voltage-controlled-oscillator (VCO) based ADCs. A major difficulty with this approach is that ADC linearity depends directly on the linearity of the VCO voltage-to-frequency control characteristic, which is in general poorly controlled.

Efforts have been made to improve performance of VCO-based ADC. One could be to place the VCO-based quantizer within a continuous-time  $\Sigma\Delta$  loops where the high loop gain suppressed non-linearity and phase noise, such as [5, 6, 7, 8, 9]. This approach, however, still required op-amp based integrators or additional DACs and was thus very analog in nature. Another would be to use a highly linear current controlled oscillator (ICO) architecture as shown in [8]. However without the support of a  $\Sigma\Delta$  modulator and a feedback DAC, the linearity of the VCO can only be improved to maximum 7.4 bits.

This thesis project describes a complete design of a 10 bit VCO-based ADC including an implementation of a lookup table (LUT) linearization technique suitable for that ADC. A three stage ring VCO is constructed and the digital output of the ADC can be obtained by measuring the VCO output clock frequency. The "Split ADC' approach [1, 2, 3, 11] is applied to realize continuous digital background calibration. All the calibration and correction process is performed entirely in the digital domain by a field-programmable gate array (FPGA) board.

#### 1.2 Organization

This thesis is organized as follows: Chapter 2 provides the background on ADC characteristics and nonideal behavior. The VCO-based ADC is also investigated, followed by different VCO architectures. Chapter 3 reviews the background calibration and correction technique in details, as well as introduces the improved algorithm

to preserve LUT continuity. Chapter 4 presents the hardware implementation in a print circuit board (PCB) including the ring VCOs and frequency dividers. Chapter 5 discusses the FPGA implementation of the calibration technique. All the inputs, outputs and timing configurations of each digital blocks are explained. The result measurements of the ADC are provided in Section 6. Finally, Chapter 7 concludes the research work presented here and provides possible paths for future investigation.

## Chapter 2

## Background

This section firstly provides background information on analog to digital converters including ideal characteristics and performance metrics. It then goes on to discuss the VCO-based ADC architecture. Finally, different VCO architectures are investigated in the last subsection.

### 2.1 Analog to Digital Converter (ADC)

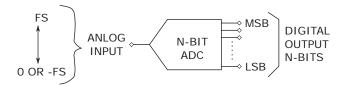

Analog to digital converters (ADCs) translate analog quantities, which are the inherent characteristic of "real world" signals, to digital language used in various applications including computing, information processing and control systems. The relationship between inputs and outputs of ADCs is shown in Figure 2.1. The ADC takes an analog voltage as an input and returns a unique group of digital levels, or binary codes, corresponding to each analog level.

Before designing an ADC, it is necessary to understand the performances and specifications of the ADC. The following subsections firstly describe the ADC transfer function, followed by discussions on different sources of error of ADCs.

Figure 2.1: ADC Input and Output Definitions

#### 2.1.1 Ideal ADC Characteristics

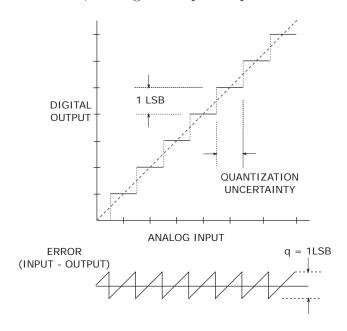

During the conversion process, the analog input signal is quantized to a digital value. The resolution of an analog to digital converter describes how many quantization levels the ADC can represent. Since the output of an ADC is in binary format, the resolution is given in powers of 2. For example, a 10-bit A/D converter can represent an analog signal using  $2^{10}$  or 1024 quantization levels. Figure 2.2 shows the ideal transfer characteristics of an ADC. It is important to note that while the analog voltage is continuous, the digital output is quantized to certain levels.

Figure 2.2: Ideal ADC Transfer Function and Quantization Noise

The only error mechanism present in an ideal ADC is quantization. This error arises because the analog input signal may assume any value within the input

range of the ADC while the output data is a sequence of finite precision samples [4]. As Figure 2.2 shown, the quantization error for any signals that spans more than few LSBs can be modeled as a sawtooth waveform [12]. The maximum error an ideal converter makes when digitizing a signal is  $0.5V_{LSB}$ . Assuming the quantization noise is uniformly distributed over the range  $\pm 0.5V_{LSB}$ , the root-mean-square quantization error can be calculated as:

$$(RMS)V_q \approx \frac{V_{LSB}}{\sqrt{12}}$$

(2.1)

For a N bit fullscale analog input sinewave,  $V_{in} = 2^{N-1}V_{LSB}\sin(2\pi ft)$ , swinging from  $-2^{N-1}V_{LSB}$  to  $2^{N-1}V_{LSB}$ , the RMS value is expressed as:

$$(RMS)V_{FS} = \frac{2^{N-1}V_{LSB}}{\sqrt{2}}$$

(2.2)

Therefore, the signal-to-noise ratio for an ideal N-bit converter is

$$SNR = 20 \log_{10} \left[ \frac{(RMS)V_{FS}}{(RMS)V_q} \right] = 6.02N + 1.76dB$$

(2.3)

It is important to note that, Equation 2.3 assumes that the quantization noises and the input signal are uncorrelated and are both measured over the full Nyquist bandwidth. In the case that the actual signal occupies in a smaller bandwidth, a correction factor must be included when calculating the signal-to-noise-ratio [12].

#### 2.1.2 Static Errors

There are four possible sources of DC errors associated with ADCs including offset error, gain error, differential nonlinearity (DNL) and integral nonlinearity (INL). Unlike the inevitable quantization noise, these error sources only occurs in non-ideal

ADCs. As described in Figure 2.2, the dashed straight line joining the midpoints of all the "steps" often referred as the "code centers", plays an important role in determining the static errors of the ADCs. This ideal transfer function of an ADC might be expressed as a straight line y = Ax + b, where y is the digital code, x is the analog input voltage, A and b are two constants. The gain and offset errors are defined as the deviations between the actual gain A and offset b and the ideal values, respectively. However, since "real world" ADC characteristic might not be a straight line, the two types of linearity error are used when investigating the ADC performance.

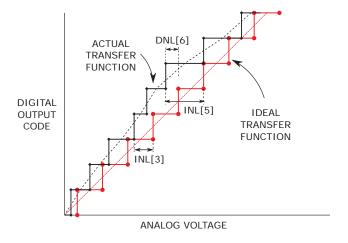

Figure 2.3 shows linearity errors of ADCs. The integral nonlinearity (INL) is defined as maximum deviation of the actual transfer characteristic of the converter from a straight line. This straight line can be either a best straight line which is drawn so as to minimize these deviations or it can be a line drawn between the end points of the transfer function once the gain and offset errors have been nullified. Differential nonlinearity (DNL) is the difference between the step size of an ADC's output and the ideal step size. The DNL and INL are usually measured in terms of least significant bit (LSB). In the case where DNL equals to -1 or +1, the ADC is nonmonotonic or has missing codes [12].

There are many possible methods to test the linearity performances of an ADC. One could be to directly measure the the code transitions of the analog input voltage while observing the digital outputs. However, this method requires a large amount of measurements and only works well if ADC's input referred noise is less than 1 LSB [12]. Another approach is the back-to-back static test which captures the error waveform by comparing the analog input to the digital output through a feedback path. The main difficulty with this approach is that it requires an additional digital to analog converter which must have an accuracy significantly greater than the ADC

Figure 2.3: Nonlinear Static Errors in Nonideal ADCs

under test [12]. The servo-loop code transition test and computer-based servo-loop test lend themselves to automated measurements, either ATE systems or in PC-based controller. These method's complexity goes beyond the scope of this project.

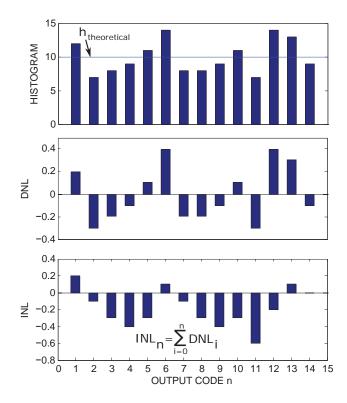

Histogram (code density) test with linear ramp input is the most suitable method in testing the linearity performance of the ADC for this project. It involves collecting a large number of digitized samples over a period of time for a well-defined input signal which is usually a low frequency fullscale triangular waveform. The number of occurrences, h(n), are then recorded for each code bin. Ideally, the number of hits in each bins are equal and can be calculated based on the total number of output samples M and total number of bins  $2^N - 1$ .

$$h(n) = \frac{M}{2^N - 2} \tag{2.4}$$

If measured histogram indicates the actual number of hits in a bin is  $h(n)_{actual}$ , then the DNL can be calculated as:

$$DNL(n) = \frac{h(n)_{actual}}{h(n)_{theoretical}} - 1$$

(2.5)

Since the INL measures the nonlinearity of the overall transfer function, it is simply the cumulative sum of the DNL.

$$INL(n) = \sum_{i=0}^{n} DNL(n)$$

(2.6)

Figure 2.4 shows an example of a histogram test of a four bit ADC. Note that, the histogram test alone does not imply monotonicity in an ADC. Additionally, in order to eliminate the linearity due to the input voltage source, the linear input ramp used in the histogram test must have greater precision compared to the ADC under test [12].

Figure 2.4: Histogram testing of a 4 bit ADC

#### 2.1.3 Dynamic Errors

The fact that DNL and INL meet the system requirements does not implies that the DAC will perform well for AC input signals. There are several ways to characterize the dynamic performance of an ADC. An FFT analysis is often used to measure the AC distortion of the signal. From that, three important parameters are defined including Signal-to-Noise-and-Distortion ratio (SNDR), Signal-to-Noise ratio (SNR), spurious-free dynamic range (SFDR), and effective number of bits (ENOB).

SINAD is defined as the ratio of the RMS signal amplitude to the mean value of the root-sum-squares of all other noise components. SNR is similar to SINAD except that it does not include the harmonic content which occurs at multiples of signal frequency. Therefore, SNR can reveal the noise floor, which ideally only includes the quantization noise. As discussed in Section 2.1.1 the ideal SNR is directly related to the resolution of the ADC. In a similar manner, the effective number of bits is defined as:

$$ENOB = \frac{SINAD - 1.76dB}{6.02} \tag{2.7}$$

It should be noted that SINAD and ENOB are functions of the input signal frequency. As frequency increases toward the Nyquist limit, SINAD decreases; so does ENOB.

Another significant specification for an ADC is the Spurious Free Dynamic Range (SFDR). SFDR is the ratio of the RMS value of an input sine wave to the RMS value of the largest spur observed in the frequency domain. Figure 2.5 shows an example of SFDR specification for an ADC. As the figure illustrates, the SFDR could be calculated either based on the amplitude of the carrier signal (dBc) or with respect to the full scale amplitude (dBFS).

Figure 2.5: Spurious Free Dynamic Range

#### 2.2 VCO-Based ADCs

There are a wide variety of different ADC architectures available depending on the requirements of the application. They can range from high-speed, low resolution flash converters to the high-resolution, low-speed oversampled noise-shaping sigma-delta converters. Scaling of CMOS to nanometer dimensions has enabled dramatic improvement in digital power efficiency, with lower  $V_{DD}$  supply voltage and decreased power consumption for logic functions. This drives ADCs toward Voltage-Controlled-Oscillator-Based ADC which takes advantage of the high speed performance and low power consumption of logic circuits. This section firstly describes structure of a VCO-based ADC, then discusses the properties, followed by the nonideality associated with it.

#### 2.2.1 VCO-Based-ADC Architecture

A VCO-based ADC is a time-based architecture that converts an analog input to frequency which is then quantized to digital output by other digital circuitry. Figure

Figure 2.6: Simplified VCO-Based ADC

2.6 shows the VCO-based approach in its simplest form: the ADC input  $V_{IN}$  is the control input to the VCO; the output of the VCO is a digital clock. The digital output x of the ADC can be obtained by measuring the clock frequency in the digital domain, for example by a counter recording the number n of VCO clock phase edges in a given period of time. At the end of every clock period the output of the counter is sampled and then reset to zero.

In order to increase the resolution of the VCO-based ADC, multiple phase outputs of the VCO are used together as shown in Figure 2.7 [10, 17]. In this structure, the output of each stage is an oscillating waveform which has frequency given by:

$$f_{VCO} = K_{VCO}V_{IN} (2.8)$$

where  $K_{VCO}$  is the slope of the voltage-to-frequency characteristic of the VCO, and  $V_{IN}$  is the analog voltage. The digital output of the ADC is resulted from summing the number of phase transitions n in a fixed period  $T_{CONV}$  of every stage. Therefore, for an N-stage ring VCO, the digital output is:

$$n = 2N f_{VCO} T_{CONV} = (2N K_{VCO} T_{CONV}) V_{IN}$$

(2.9)

Figure 2.7: Multi-phase VCO-Based ADC Architecture

As Equation 2.9 indicates, ideally, the digital output is directly proportional to analog input voltage, which is the desired characteristic of an ADC. For an N-phase VCO-based ADC, the resolution of the ADC is higher by a factor of 2N compared to that of a single-phase converter. The multi-phase approach does require a modest increase in complexity, power consumption and chip area [17].

#### 2.2.2 VCO-Based ADC Properties

The VCO-based ADC has several important properties making it suitable for high speed and low power consumption signal processing applications. The first property is that quantization noise is first-order noise-shaped [10]. The quantization error of the VCO-based ADC is not as straight forward as conventional ADC architectures. Since the number of cycles of each the clock signal is counted, the phases are quantized by  $2\pi$ . If both the rising edges and the falling edges of the oscillated waveform are counted, the phases are quantized by  $\pi$ . A signal waveform capturing the phase of the VCO output is shown in Figure 2.8. Since the residual phase (quantization error  $\phi_q[n-1]$ ) of the previous sampling period inherently becomes the initial phase  $\phi_i[n]$  of the next period, the output of a N-phase VCO-based ADC can be calculated

by:

$$y[n] = \frac{N}{2\pi} (\phi_x[n] + \phi_q[n-1] - \phi_q[n])$$

(2.10)

where  $\phi_x[n]$  is the VCO phase change due to analog inpute. Taking the Z-transform of Equation 2.10 gives:

$$Y(z) = \frac{N}{2\pi} (\Phi_x(z) + \Phi_q(z)(z^{-1} - 1))$$

(2.11)

As Equation 2.11 indicates, the quantization phase noise  $\phi[n]$  "sees" a high pass filter transfer function  $(z^{-1} - 1)$ . Therefore, the VCO-based ADC is first-order noise-shaped.

Figure 2.8: Quantization of phase in VCO-based ADC

Another property that makes VCO-based ADC superior to other architectures is that the output of a ring VCO is digital in nature. The clock signal toggles between two discrete levels, either  $V_{DD}$  or GND. This property makes the VCO a great converter building block which takes advantage of the high performance nanometer CMOS technology without worrying about the decreasing power supply. In addition, since the amplitude of the VCO output does not play an essential role

in the quantization process, the architecture greatly reduces the need of additional analog circuitries such as buffers and amplifiers.

#### 2.2.3 VCO-Based ADC Nonideality

Despite of these attractive properties discussed in Section 2.2.2, implementing VCO-based ADC still faces a critical challenge, since the voltage-to-frequency tuning curve of the VCO is usually nonlinear. This translates directly to the nonlinearity of the ADC, which highly degrades both static and AC performance of the ADC. Mitigating this effects of the VCO characteristics becomes the main subject of this project.

Figure 2.9: A 3-stage VCO voltage-to-frequency characteristic

Figure 2.9 captures the voltage-to-frequency characteristic of a three stage current starved VCO. The figure shows that the V-f curve of the VCO is nonlinear with an offset and a varied slope  $K_{VCO} = \partial f_{VCO}/\partial V_{in}$ . Although the offset of the VCO can easily be corrected by subtracting a fixed amount to the digital output code, some form of calibration to correct the nonlinear slope  $K_{VCO}$  is required in order to achieve a SNR better than 40dB [1, 2, 9].

#### 2.3 VCO architectures

This section briefly discusses some of the available VCO architectures. One of the oscillator topologies is the LC oscillator. Although this topology out-performs ring oscillators in terms of phase noise [14, 17], it is analog in nature and requires areaconsuming passive elements; therefore, it is not considered further in this project.

Figure 2.10: Waveforms of a three stage single ended ring VCO

Another common type of oscillator is the ring oscillator. The simplest ring oscillator can be formed by an odd number of inverters connected in a closed loop with positive feedback as shown in Figure 2.10. The delay time between the 50% points of the input and output are labeled  $t_{PLH}$  and  $t_{PHL}$  depending on whether the output logic level is changing from high to low or from low to high. If the total number of stages is n and all of them have the same delay, the oscillation frequency is then given by:

$$f = \frac{1}{n(t_{PHL} + t_{PLH})} \tag{2.12}$$

The number of stages n in a ring oscillator is determined by various requirements,

including speed, power consumption, and noise immunity. Usually, there must be an odd number of inversions in the loop so that the circuit does not latch up. However, the differential implementation of the ring oscillator can utilize an even number of stages by simply configuring one stage such that it does not invert [14].

Figure 2.11: Simplified Current Starved VCO

As shown in Equation 2.12 the oscillation frequency depends on the total delay of each stage. Thus, to vary the frequency, the delay time can be adjusted. There are several ways to control this delay. The first method is to control the current drive strength charging and discharging the load of each inverter. This topology is referred as the current-starved VCO. Figure 2.11 shows a simplified view of a single stage of the current-starved VCO. The two additional MOSFETs, controlled by the input voltage  $V_{CTR}$ , are used to limit the drain currents to the inverter; in other word, the inverter is starved for current. The total sum of the output capacitor of the first stage and the input capacitor of the second stage can be modeled as a load capacitor  $C_L$ . The time it takes to charge and discharge  $C_L$  depends on the current  $I_{Dp}$  and  $I_{Dn}$ , respectively. These time delays are the same as the propagation delays  $t_{PHL}$  and  $t_{PLH}$  in Equation 2.12. Therefore, by controlling either the current  $I_{D1}$  or  $I_{D2}$  the frequency can be changed.

Another method is to vary the propagation delay by varying the capacitive load  $C_L$ . This variation in load capacitance can be realized by one ore more voltage dependent capacitors called varactor diodes. A reverse-bias pn junction can serve as a varactor which has capacitance of:

$$C_{var} = \frac{C_0}{(1 - V/\Phi_B)^m} \tag{2.13}$$

where  $C_0$  is a zero bias capacitance, V is the applied voltage,  $\Phi_B$  is the builtin voltage of the junction, and m is a value typically between 0.3 and 0.5 [15]. Adding a varactor diode increases the load capacitance, therefore, directly affect the tuning range of the VCO. Additionally, the nonlinear relationship between controlled voltage and the varactor diode capacitance is also translated into the nonlinearity of the VCO.

There are many other methods to implement a VCO including the source-coupled VCO [13] and delay interpolation VCO [14]. Circuit-level techniques can be used to improve uncalibrated VCO linearity, easing requirements on digital calibration and allowing smaller LUT size. However, since designing a VCO is not the main focus of this project, these techniques are not covered in details. Additionally, as the calibration technique operates entirely in the digital domain, its applicability is not limited by the specific VCO circuit architecture [1].

## Chapter 3

# Background Calibration and Correction Technique

A significant challenge to the VCO-based ADC architecture is to mitigate the effect of the nonlinear V-f characteristic of the VCO. The main purpose of this section is to discuss a calibration method to improve the linearity of the VCO-based ADC. First, the lookup-table with linear interpolation method is discussed. The next section investigates the "Split ADC" background digital calibration approach. Finally, the calibration and correction technique is summarized and the functional block diagram, as how the technique is implemented, is presented.

#### 3.1 Lookup-Table Linearity Correction

An ideal VCO-based ADC has the digital output code n proportional to the analog input  $V_{IN}$ . However, as discussed by Section 2.2.3, the real relationship between the VCO count n and the input  $V_{IN}$  is usually nonlinear. In order to correct the nonideal output code, the proposed digital correction technique utilizes a lookup-table (LUT).

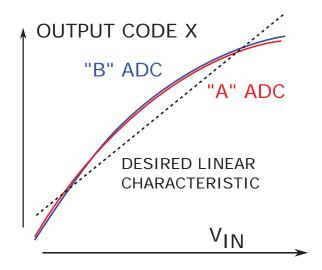

This LUT provides an additional transfer function between the "uncorrected" count and the final desired digital output code. Mathematically, this transfer function is the inverse of the VCO characteristic; thus it can cancel the nonlinearity of the VCO. This can be explained in Figure 3.1.

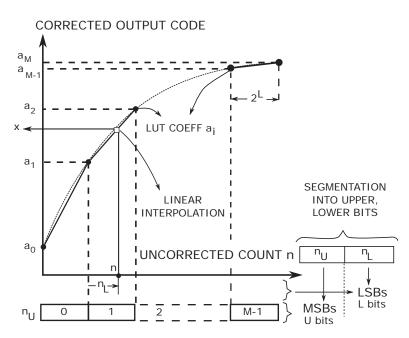

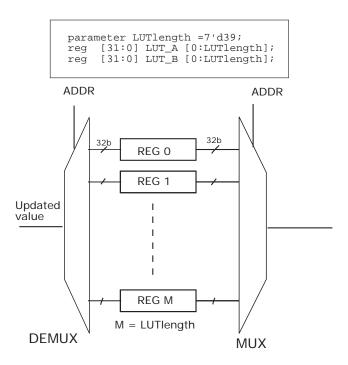

Figure 3.1: Transfer functions of nonlinear ADC with LUT correction

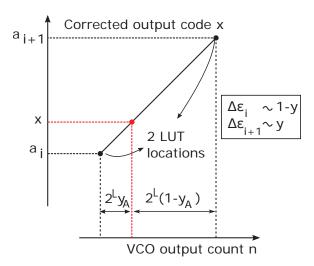

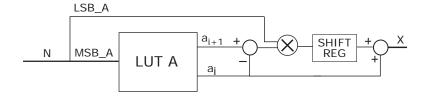

Since LUT is a discrete point by point mapping implementation of a transfer characteristic, it requires  $2^N$  entries to fully cover the whole range of the N bit ADC uncorrected output. In order to reduce complexity of the digital implementation, a combination of the LUT approach and linear interpolation is used [1, 2]. Figure 3.2 shows definition of the LUT: The uncorrected counter output n is divided into an upper and a lower group of bits, thereby segmenting the ADC transfer characteristic. The size of the upper MSB word  $n_U$ , U bits long, determines the maximum number of points M in the LUT:  $M \leq 2^U + 1$ . The MSBs  $n_U$  is served as index to a lookup table which holds correction coefficients  $a_{n_U}$ . Within each segment, the value of the LSB word  $n_L$  is used to linearly interpolate between adjunct  $a_{n_U}$  and  $a_{n_U+1}$  values in the LUT. Since the two adjunct LUT entries are separated by  $2^L$  on the n axis,

the corrected output code x can be calculated as:

$$x = a_{n_U} + \underbrace{\frac{n_L}{2^L}}_{n_U} (a_{n_U+1} - a_{n_U})$$

(3.1)

The LUT can be implemented using digital registers and multiplexers. One multiplication is required for the linear interpolation. The fraction  $1/2^L$  can be realized simply by an L bit shift in radix point. Since the lengths of the MSB word and LSB word determine the LUT length and spacing, they also affect the linearity of the final digital output. The number of points in the LUT needed for adequate correction is determined by the desired ADC accuracy and the nonlinearity of the VCO V-f characteristic. More points in the LUT provide a better linearity of the digital output but require more complex digital circuitry, and consume more power [1, 2].

Figure 3.2: Lookup table with linear interpolation digital correction

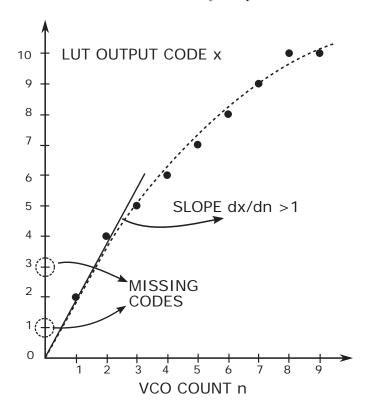

Another aspect that must be considered when implementing the LUT is the

"redundancy factor". Due to the discrete nature of the input count, there are numbers that cannot come out of the interpolation. An example of this is shown in Figure 3.3. At the region where the slope of the LUT transfer function dx/dn is greater than 1, as the input count increases by 1 the corresponding output code might increase by more than 1, therefore skipping over some possible values, leading to missing codes in the ADC. To ensure every output x can be reached by at least

Figure 3.3: Missing codes in LUT implementation

one input count n, the slope dx/dn must always be less than unity [18]. For an N-bit converter, the ultimate output code x will have  $2^N$  possible values, zero to  $2^N - 1$ . In order to ensure the slope to be less than unity, the total possible output counts of the VCO must be increased to  $R(2^N - 1)$ , where R is a redundancy factor. For an ideal ADC, the slope is always 1, therefore, no redundancy would be required, and R = 1.

There are several ways to implement the redundancy factor in VCO-based ADC. The first one would be to initialize the LUT so that total output range is reduced by a factor of R compared to the input range. For example, as discussed previously, the distance between two adjunct LUT entries in the n domain is  $2^L$  where L is the LSB word length. The redundancy factor R could be realized by initialize the LUT such that the difference between two values in the adjunct LUT locations is  $2^L/R$ .

Another simpler approach is to shift the radix point of the digital output code. For instance, the redundancy factor of 4 can be implemented by a left shift in the radix point by 2 bits. Although, this method only works if R is a power of 2, it is easy to be implemented in digital domain and will be utilized in this project.

#### 3.2 Dithered Split-ADC Calibration Concept

The task of the calibration procedure is to determine the  $a_i$  coefficients in the LUT used for linear interpolation as shown in Figure 3.2. One option would be to take the ADC offline, sweep the input linearity over the entire signal range and determine the proper coefficients  $a_i$ , as shown in [10]. Disadvantages of this approach include the need to take the ADC offline and develop the known input signal. Another drawback is that the VCO characteristic could be a function of temperature. As the VCO characteristic changes, it requires different set of coefficients  $a_i$  to properly correct the digital output. Therefore, offline calibration technique cannot mitigate the nonlinearity problem if the ADC characteristic differs over time. This section discusses the proposed approach using "Split ADC" architecture presented in [1, 2] to realize the background calibration with no need for an accurately known input signal.

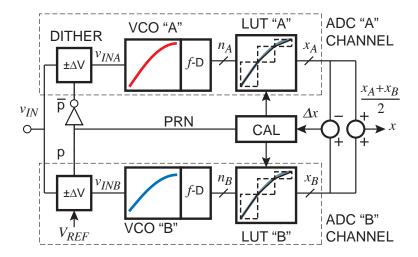

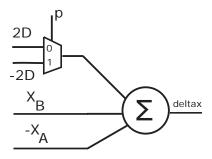

Figure 3.4 shows the split ADC concept as implemented in this project. The

Figure 3.4: Dithered Split ADC system block diagram

signal path is split into two channels, each producing individual output codes  $x_A$  and  $x_B$ . A dither signal  $\pm \Delta V$  is added to the input voltage  $V_{IN}$  so that the inputs to each channels are:

$$V_{INA} = V_{IN} - p\Delta V \tag{3.2}$$

$$V_{INB} = V_{IN} + p\Delta V \tag{3.3}$$

in which  $p = \pm 1$  is chosen on a pseudo-random basis for each conversion. The best estimate for ADC output code x is the average of the  $x_A$  and  $x_B$  outputs:

$$x = \frac{x_A + x_B}{2} \tag{3.4}$$

Since, the dither is added to one channel, and subtracted from the other, its effect can be eliminated when averaging the digital output codes. The difference  $\Delta x$  of the two output codes  $x_A$  and  $x_B$  can be used to calibrate the two LUTs transparently to converter operation in the output code signal path:

$$\Delta x = x_B - x_A \tag{3.5}$$

For more intuitive understanding of the algorithm, the next subsections consider the local difference between the "A" and "B" characteristics, followed by calibration of the slope.

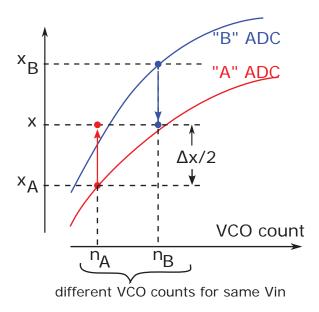

#### 3.2.1 ADC Characteristic Alignment

In general the two VCOs have different characteristics, requiring two separate LUTs for each of the "A" and "B" ADCs, as shown in Figure 3.5. Since the VCO characteristics are different, even with identical input voltages the uncorrected output count  $n_A$  and  $n_B$  will generally be different. If the two LUTs had been correctly calibrated, the  $x_A$  and  $x_B$  outputs would have been equal. If the LUTs are not calibrated correctly, the LUT output  $x_A$  and  $x_B$  would have been different. The nonzero difference  $\Delta x = x_B - x_A$  indicates a need to adjust the LUTs to bring the LUTs and the ADC into calibration. Since there is no reason to prefer one VCO

Figure 3.5: Split ADC characteristic alignment

over the other, half of the total difference  $\Delta x$  is assigned to each LUT to produce

the same output code of:

$$x = x_B - \frac{\Delta x}{2} = x_A + \frac{\Delta x}{2} = \frac{x_B + x_A}{2}$$

(3.6)

For each conversion, one LUT location is updated such that the output codes are the same for identical input voltages  $V_{IN}$  regardless of the disagreement in the two  $V_{IN}$ -to-n characteristics. Therefore, over many conversions across the input signal range, repeating this LUT adjustment process will eventually bring the ADC characteristics into agreement. However, the main difficulty of this approach is that while point-by-point agreement among the conversions can be achieved, the linearity of the ADC is not guaranteed. In other words, calibration can end up with two agreeing but equally erroneous nonlinear characteristics as shown in Figure 3.6. This difficulty is addressed in Section 3.2.2 below.

Figure 3.6: Split ADC Characteristic alignment with two agreeing but equally non-linear ADC characteristics

### 3.2.2 Slope Calibration

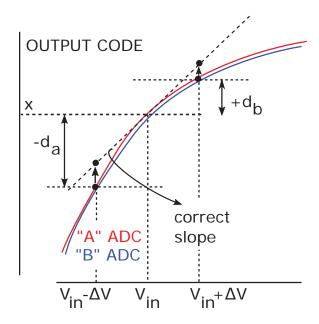

The characteristic alignment technique discussed above does not have any visibility to the linearity of the two channels. To enable correction of linearity errors, the dither function is added to the input as shown in the system block diagram of Figure 3.4. The inputs are offset by a known dither value  $\pm \Delta V$  representing a known code excursion  $\pm D$  at the ADC output. However, since the two ADC characteristics are different, the actual codes corresponding to  $\Delta V$  also differs from the ideal value. Therefore, the general input voltages and output codes of the two channels can be expressed by:

$$V_{INA} = V_{IN} - p\Delta V \to x_A = x - pd_a \tag{3.7}$$

$$V_{INB} = V_{IN} + p\Delta V \to x_B = x + pd_b \tag{3.8}$$

where p is either +1 or -1. As Equation 3.7 and Equation 3.8 indicate, not only the point-by-point agreement but also the slopes of the VCO characteristics are now under consideration. The difference of the two output codes  $x_{outA}$  and  $x_{outB}$  can be calculated as:

$$\Delta x = (x - x) + p(d_a + d_b) = p(d_a + d_b)$$

(3.9)

Figure 3.7 shows the idea of slope calibration. Ideally, when the two ADCs are identical and linear,  $d_a$  and  $d_b$  would be equal to D. Therefore  $\Delta x_{(ideal)} = p(D+D) = 2pD$ . The fact that  $\Delta x$  is different from the desired value  $\pm 2D$  indicates that the slope of the "A" and "B" characteristics need to be adjusted. The mathematical derivation of how the LUT entries would be updated is discussed in Section 3.2.3 below.

Figure 3.7: Slope Calibration

### 3.2.3 Error Estimation

This section investigates the mathematical derivation of the error estimation and LUT calibration process. Firstly, as discussed in the previous sections, generally the two LUTs have different coefficients denoted by  $a_i$  and  $b_i$  corresponding to ADC "A" and ADC "B". Therefore, for each LUT Equation 3.1 can be rewritten as:

$$\hat{x}_A = (1 - y_A)\hat{a}_{n_{UA}} + y_A\hat{a}_{n_{UA}+1} \tag{3.10}$$

$$\hat{x}_B = (1 - y_B)\hat{b}_{n_{UB}} + y_B\hat{b}_{n_{UB}+1}$$

(3.11)

The "hat" above each parameter in the equations denotes the difference between the actual value, that is needed to be calibrated, and the desired correct value. The LUT entries can be redefined as the sum of the correct value and an error term  $\varepsilon$ .

$$\hat{a}_{n_{UA}} = a_{n_{UA}} + \varepsilon_{n_{UA}} \tag{3.12}$$

$$\hat{b}_{n_{UA}} = b_{n_{UA}} + \varepsilon_{n_{UB}} \tag{3.13}$$

Substitute (3.12) and (3.13) into (3.10) and (3.11) gives:

$$\hat{x}_{A} = (1 - y_{A})(a_{n_{UA}} + \varepsilon_{n_{UA}}) + y_{A}(a_{n_{UA}+1} + \varepsilon_{n_{UA}+1})$$

$$= \underbrace{[(1 - y_{A})a_{n_{UA}} + y_{A}a_{n_{UA}+1}]}_{x_{A}} + (1 - y_{A})\varepsilon_{n_{UA}} + y_{A}\varepsilon_{n_{UA}+1}$$

and:

$$\hat{x}_{B} = (1 - y_{B})(a_{n_{UB}} + \varepsilon_{n_{UB}}) + y_{B}(b_{n_{UB}+1} + \varepsilon_{n_{UB}+1})$$

$$= \underbrace{[(1 - y_{B})b_{n_{UB}} + y_{B}b_{n_{UB}+1}]}_{x_{B}} + (1 - y_{B})\varepsilon_{n_{UB}} + y_{B}\varepsilon_{n_{UB}+1}$$

Given that the difference of the two corrected digital outputs,  $x_B - x_A$ , should be 2pD as mentioned in Section 3.2.2, taking the difference of the estimates results in:

$$\hat{x_B} - \hat{x_A} - 2pD = (1 - y_B)\varepsilon_{n_{UB}} + y_B\varepsilon_{n_{UB}+1} - (1 - y_A)\varepsilon_{n_{UA}} - y_A\varepsilon_{n_{UA}+1}$$

(3.14)

Equation 3.14 captures the contribution of each LUT entry error to the variation of  $\Delta x = x_B - x_A$  from its ideal value 2pD. If all the error terms  $\varepsilon$  in (3.14) are zero, then the left hand side must be equal to zero, indicating the correct offset and slope calibration of the ADC characteristics.

Mathematically, four conversions are needed to solve for four unknown errors in a specific LUT entry in (3.14). Since there are many LUTs errors to determine, an ensemble of K ( $\approx 1000$ ) conversions is accumulated. A matrix representation of these results are described by:

$$\begin{bmatrix} \mathbf{Y}_{\mathbf{A}} & \mathbf{Y}_{\mathbf{B}} \end{bmatrix} \cdot \begin{bmatrix} -\mathbf{e}_{\mathbf{A}} \\ \mathbf{e}_{\mathbf{B}} \end{bmatrix} = \mathbf{\Delta}\mathbf{x} - 2D\mathbf{p}$$

(3.15)

$\mathbf{Y_A}$  and  $\mathbf{Y_B}$  are  $K \times M$  matrices containing coefficients  $y_A$  and  $y_B$  in (3.14); K is the ensemble size and M is the length of the LUT. An example of  $\mathbf{Y_A}$  is shown in (3.16). Row  $i^{th}$  of the matrix represents error weight coefficients for the  $i^{th}$  conversion in the ensemble; and column  $k^{th}$  contains coefficients corresponding to  $k^{th}$  entry in the LUT. Since in every conversion, only two of the LUT locations  $n_U$  and  $n_U + 1$  would be hit, there are only two nonzero terms, 1 - y and y, in each row.

$$\mathbf{Y_A} = \begin{bmatrix} 0 & (1 - y_{A1}) & y_{A1} & 0 & \cdots \\ 0 & 0 & (1 - y_{A2}) & y_{A2} & \cdots \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ (1 - y_{AK}) & y_{AK} & \cdots & 0 & \cdots \end{bmatrix}$$

(3.16)

$\mathbf{e_A}$  and  $\mathbf{e_B}$  in (3.15) are  $M \times 1$  column vector of the LUT errors to be determined:

$$\mathbf{e_{A}} = \begin{bmatrix} \varepsilon_{0A} \\ \varepsilon_{1A} \\ \vdots \\ \varepsilon_{MA} \end{bmatrix}, \qquad \mathbf{e_{B}} = \begin{bmatrix} \varepsilon_{0B} \\ \varepsilon_{1B} \\ \vdots \\ \varepsilon_{MB} \end{bmatrix}$$

$$(3.17)$$

$\Delta \mathbf{x}$  and  $2D\mathbf{p}$  are  $K \times 1$  column vectors of the actual  $\hat{x}_B - \hat{x}_A$  differences and the ideal values  $x_B - x_A = 2pD$ , respectively in each conversion.

$$\Delta \mathbf{x} - 2D\mathbf{p} = \begin{bmatrix} \Delta x_1 \\ \Delta x_2 \\ \vdots \\ \Delta x_K \end{bmatrix} - 2D \begin{bmatrix} p_1 \\ p_2 \\ \vdots \\ p_K \end{bmatrix}$$

(3.18)

Ideally, the LUT error vectors  $\mathbf{e_A}$  and  $\mathbf{e_B}$  could be determined by solving Equation 3.15, then would be subtracted from the  $a_i$  and  $b_i$  in the LUT to get correct

coefficients. However, there are difficulties associated with this approach. Firstly, since the total number of LUT locations (2M) is much fewer than the number of conversions K in an ensemble, the system is considered as an "overdetermined" systems. In other words, the matrix  $\mathbf{Y} = \begin{bmatrix} \mathbf{Y_A} & \mathbf{Y_B} \end{bmatrix}$  in Equation 3.15 has more rows than columns; therefore, the system of equations has more equations than unknowns. According to [20], overdetermined system is usually inconsistent and does not have a unique solution, especially when there is a lot of uncertainty and randomness in the system. Secondly, reducing the number of conversions K to 2Mmakes Y to be a square matrix, but does not guarantee it to be full rank; and unique solution does not exist. Particularly, when there are fewer conversions, it is very likely that the input signal does not hit all the LUT locations in one ensemble, resulting in "zero" columns in Y. Finally, even if the solution of (3.15) exists, solving for  $\mathbf{e_A}$  and  $\mathbf{e_B}$  requires a very complicated left inverse matrix operation which is too computationally intensive and could not be realized by a simple digital circuitry. Due to all of these difficulties, another approach is investigated in the next section to estimate the error of the LUT coefficients.

### 3.2.4 Iterative Matrix Solution

The main challenge to the calibration process addressed in Section 3.2.3 includes the ability to solve for an exact solution of Equation 3.15. To simplify the digital hardware, an iterative procedure is used to avoid matrix inversion [3]. Instead of solving for exact error terms, an LMS-style estimation method is adopted. The procedure begins by firstly multiply both side of Equation 3.15 with the transpose of Y:

$$(\mathbf{Y}^{\mathbf{T}} \cdot \mathbf{Y}) \cdot \mathbf{e} = \mathbf{Y}^{\mathbf{T}} \cdot (\Delta \mathbf{x} - 2D\mathbf{p})$$

(3.19)

For simplicity, assume (unrealistically) that the  $(\mathbf{Y^T} \cdot \mathbf{Y})$  matrix is equal to the identity matrix

$$(\mathbf{Y}^{\mathbf{T}} \cdot \mathbf{Y}) = \mathbf{I} \tag{3.20}$$

Substitute (3.20) into (3.19) gives an "over simplified" solution to the error matrix:

$$\mathbf{e} = \begin{bmatrix} -\mathbf{e}_{\mathbf{A}} \\ \mathbf{e}_{\mathbf{B}} \end{bmatrix} = \mathbf{Y}^{\mathbf{T}} \cdot (\mathbf{\Delta} \mathbf{x} - 2D\mathbf{p})$$

(3.21)

The corrected LUT entries would be calculated by subtracting the error terms from the incorrect LUT coefficients. However, since (3.21) relies on the unrealistic assumption (3.20), a least mean square (LMS) method is adopted by subtracting a small portion  $\mu$  of the estimated errors  $\mathbf{e}$  as follow:

$$a_i^{new} = a_i^{old} - \mu \varepsilon_{iA} \tag{3.22}$$

$$b_i^{new} = b_i^{old} - \mu \varepsilon_{iB} \tag{3.23}$$

Examination of (3.21) and (3.16) shows that the large  $\mathbf{Y}$  matrix need not be stored, since the information required for the  $\varepsilon_{\mathbf{A}}$  and  $\varepsilon_{\mathbf{B}}$  estimation can be accumulated on a conversion-by-conversion basis. Every conversion, if a LUT location is hit, the error for that entry will be accumulated and then finally subtracted from the actual LUT coefficients at the end of the ensemble. The way each error is accumulated in every conversion can be described by:

$$\varepsilon_{iA}^{(new)} = \varepsilon_{iA}^{(old)} - (1 - y_{iA})(\Delta x_i - 2p_i D)$$

(3.24)

$$\varepsilon_{(i+1)A}^{(new)} = \varepsilon_{(i+1)A}^{(old)} - y_{iA}(\Delta x_i - 2p_i D)$$

(3.25)

$$\varepsilon_{iB}^{(new)} = \varepsilon_{iB}^{(old)} + (1 - y_{iB})(\Delta x_i - 2p_i D)$$

(3.26)

$$\varepsilon_{(i+1)B}^{(new)} = \varepsilon_{(i+1)B}^{(old)} + y_{iB}(\Delta x_i - 2p_i D)$$

(3.27)

The energy cost of implementing the algorithm is modest; only two additional multiplications per conversion are required and the multiplier is already available as a resource since it is required for the linear interpolation. As the four equations indicate, all four error terms are proportional to  $\Delta x_i - 2p_iD$ . The more  $\Delta x$  differs from its ideal value, the larger the error terms. Additionally, the "distance" between the actual output code to the LUT coefficient also plays an important role in updating the LUT. It is related to the percentage of the contribution of each LUT entry to the error of the output. Intuitively, this makes senses, since the closer the value to a LUT location, the more effect that LUT entry has on the output code. Therefore the error of the output code is more likely due to the error of that LUT entry compared to the others. This can be seen in Figure 3.8. One extreme example of this is when  $y_{iA}$  equals zero; all of the output error is due to LUT coefficient  $a_i$  and no information on the error of  $a_{i+1}$  is observed.

Figure 3.8: Error estimation depends on distance of the LUT locations to the input count

A key advantage of the LMS approach is that the error estimates need not be accurate; all that is required is that they be zero-bias and (on average) steer the convergence of each LUT entry in the correct direction [3]. Secondly, development

of the split ADC approach relied on the A and B inputs differing by a known  $\Delta V$  dither. In practice, noise will cause an additional difference, leading to inaccuracy in error estimation even if the error terms had been solved exactly. By averaging information over many ensembles of conversions, the LMS approach averages out the effect of noise in determining calibration parameters [1].

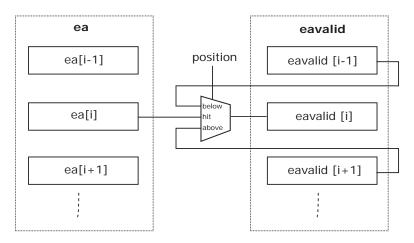

### 3.2.5 Limited Signal Range and "Stitching" 'Estimation

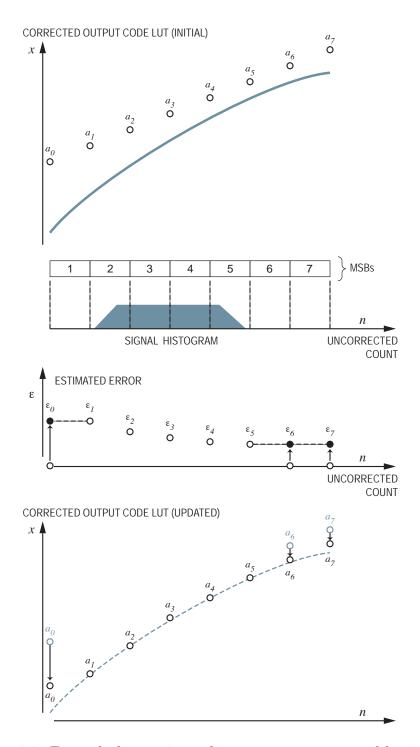

As mentioned previously in Section 3.2.3, for each conversion, only the two LUT locations, which are hit, are updated. Therefore, regions of the LUT not covered by the input signal are not calibrated. If the signal activity histogram changes to access previously unused LUT entirely, ADC error may increase dramatically until the background calibration loop can converge for the newly used portions of the LUT.

Consider the example shown in Figure 3.9. Suppose the error estimation process begins with an initial distribution of linearly spaced LUT entries  $a_i$  as shown in the plot at the top of the figure. Also shown as the solid gray line in the figure is the correct characteristic for error estimation process to converge to. Since the LUT entries are incorrect the error estimation process would result in nonzero values, which will be used in the LMS loop to drive the errors toward zero.

In the middle of Figure 3.9 is a histogram of input voltage distribution during one ensemble of K conversions. Due to the limited signal range, only LUT segments 2-5 are used; the input voltage never reaches the range corresponding to segments 1, 6, or 7.

Below the histogram in Figure 3.9 is a plot showing open circles to represent the results of the error estimation process for this ensemble of data. Nonzero error estimates are correctly returned for locations  $a_1$ - $a_5$ . But since LUT locations  $a_0$ ,  $a_6$ ,

Figure 3.9: Example for portions of input range not covered by signal.

and  $a_7$  are never used, estimate for these locations is zero.

At the bottom of Figure 3.9 is a plot of the updated lookup table. As the LMS

process updates the  $a_i$  values, locations  $a_1$ - $a_5$  are corrected since the input signal range allows proper estimation of errors  $\varepsilon_1$ - $\varepsilon_5$ . But since the error estimates are zero for  $a_0$ ,  $a_6$ , and  $a_7$ , they will not change even as  $a_1$ - $a_5$  are corrected. The result, with gray circles shown for  $a_0$ ,  $a_6$ , and  $a_7$  at the bottom of figure 3.9, is a LUT with discontinuities and potentially even nonomonomorphicity. If the input signal histogram shifts, the ADC will make large errors until the calibration loop converges with the new information.

The solution implemented in this work is based on the ability to distinguish between the cases of  $\varepsilon = 0$  due to a true zero error, and  $\varepsilon = 0$  due to an LUT location not being used. During each ensemble of conversions, the calibration algorithm keeps track of whether an LUT location has been used or not. After calculation of the  $\varepsilon_i$  values, but before the LMS updating, the algorithm checks for unused LUT locations. When the algorithm reaches an unused LUT location, the  $\varepsilon = 0$  in that location is replaced with the nearest valid estimate from an LUT location that was used. This substitution is represented with the arrows and solid circles in the plot of  $\varepsilon$  in Figure 3.9. The result, shown with the open circles for  $a_0$ ,  $a_6$ , and  $a_7$  at the bottom of Figure 3.9, preserves continuity of the LUT and reduces ADC errors when the input signal range histogram changes. This "stitching" of the LUT does not completely eliminate ADC errors. Since there is no signal in the unused LUT locations no information as to the correctness of those values is determined. However this technique does preserve continuity of the lookup table at the boundary between the used and unused portions of the signal range.

#### 3.2.6 Offset Consideration

As noted earlier, this calibration approach provides no information on offset. The error estimation block only sees the difference between the two channels, thus has no vision on the absolute offset of the ADC. Since the LMS loop is a perfect numerical integrator, any systematic offset errors in the estimation process would accumulate indefinitely, causing numerical overflow. To prevent this numerical problem, the value of one location in the "A" table is fixed and all other error estimates are referenced to that location to prevent a global drift in offset of the lookup table entries.

If absolute offset accuracy is required, one of the "A" or "B" converters can be taken off line for one conversion to sample a known DC voltage and provide an absolute offset reference for the ADC. When this is done the averaging the two channel is suspended for that one conversion and the ADC output is determined only by the output of the other "A" or "B" converter that was not taken offline.

## 3.3 Calibration Algorithm Summary

Figure 3.10: Calibration algorithm flow chart

Figure 3.10 summarizes the LUT calibration and correction technique implemented in this project. While the right hand side of the figure captures the operations that occur every conversion, the left hand side includes all calculations that are done for every ensemble (K conversions).

Initially, the analog input voltage is preprocessed by adding a known dither voltage  $\Delta V$  to one channel and subtracting  $\Delta V$  to the other. The sign of the dither is determined by a pseudo-random sequence  $p=\pm 1$ . The analog voltage is then converted in to digital outputs  $n_A$ ,  $n_B$  by counting the number of phase transitions of the VCO output clock signals in a given period of time. Generally, the two VCOs are not identical and both nonlinear; therefore two LUTs are implemented to correct the output counts. The final digital code is obtained and the effect of dither is eliminated by averaging the two resulted outputs of the two channels  $x_A$  and  $x_B$ .

In every conversion, there are at most two adjunct LUT coefficients used for each channel. These locations are then recorded by the "TRACK LUT USAGE HISTOGRAM" block in Figure 3.10. Additionally, all parameters needed to estimate the error using Equation 3.15 are also calculated, including  $y_A$ ,  $y_B$ , and  $\Delta x$ . The error terms  $\varepsilon_A$  and  $\varepsilon_B$  of all the used LUT locations are then accumulated over K conversions. Finally, before the LUTs are updated by subtracting a small amount  $\mu\varepsilon$ , the error of the unused LUT coefficients are managed by the "STITCH EXTIMATE CONTINUITY" block to preserve the continuity of the LUT.

## Chapter 4

## **Analog Circuit and PCB**

## Implementation

This chapter describes the Printed Circuit Board (PCB) design of the VCO-based ADC. The choice of the VCO architecture is discussed in the first section. In order to reduce the frequency of the signal processed by the FPGA board, a frequency divider was built; the details are discussed in the next section. Finally, the overall block diagram of the PCB is summarized in the last section.

## 4.1 Ring VCO

The purpose of this section is to discuss a VCO topology which can provides an oscillating waveform swinging from 0V to 1.8V and has wide frequency range of about 100MHz. Although the linearity of the VCO directly affects the performance of the ADC, the digital calibration technique applicability is not limited by the VCO architecture [1, 2]. Due to the time constraint, this project does not concentrate on a complete VCO design in transistor level. Instead, different circuits were built at

the discrete level, and then tested to determined the most suitable implementation of the VCO for the ADC specifications.

Most of these implementations were based on the 74AUC1G00 NAND gate. There is no specific reason for using this chip other than the availability of the component in the lab. It should be noted that the fundamental building block of a VCO, an inverter, can be easily implemented using a NAND gate by connecting the two input of the gate as shown in Figure 4.1. Three NAND gates are then connected together in a feedback loop to form a ring oscillator. The frequency at which the circuit oscillates depends on the propagation delay of each stage as discussed in Section 2.3

Figure 4.1: Simple ring oscillator implemented by NAND gate

There are several ways to control the frequency of the oscillator. One could be to use the current starved VCO architecture by using a MOSFET to control to current provided to the inverter as shown in Figure 4.2. However, one difficulty with this approach is that the power supply  $V_{DD}$  and the input voltage range  $V_{IN}$  needs to be high enough so that transistor does not crash in to saturation region. More importantly, experiments show that the frequency to  $V_{IN}$  characteristic of this structure is not well behaved. The output waveform has relatively large ripples, causing uncertainty in the phase transition measurements. This might be caused by the internal structure of the NAND gate which cannot be controlled. Therefore

another structure is considered for this project.

Figure 4.2: Using MOSFET to control the delay of the inverter

Shown in Figure 4.3 is the schematic of the VCO used in this project. The ring oscillator is implemented in the same manner as Figure 4.1. The speed of the oscillator is controlled directly by varying the supply voltage of these inverters.  $R_S = 50\Omega$  is the protecting resistor to limit the input current. An emitter follower is added to buffer the input voltage  $V_{IN}$ , preventing the two channels to be coupled together.

One important factor that needs to be considered when designing the emitter follower is that as the current drawn by the ring oscillator changes, the bias voltage  $V_{BE}$  also changes exponentially. In order to avoid the nonlinear effect introduced by the emitter follower, it is desired that the collector current of transistor  $I_C$  should be large enough compared to the maximum current drawn by the ring oscillator  $I_{RING}$ . Measurement shows  $I_{RING(max)} \approx 5mA$ . If  $I_C$  is about 3X larger than  $I_{RING}$  then the resistor  $R_E$  can be determined by:

$$R_E = \frac{V_E}{I_C - I_{RING}} \approx \frac{2V}{15mA - 5mA} = 200\Omega$$

(4.1)

The input voltage  $V_{IN}$  is translated directly to the supply voltage of the ring

Figure 4.3: Ring VCO schematics

oscillator by:  $V_{RING} \approx V_{IN} - 0.7V$ . Therefore, not only the frequency but also the amplitude of the oscillated output waveform depend on the input voltage  $V_{IN}$ . In order to keeps the amplitude of the output clock signal approximately at 1.8V, one more inverter is required as shown in Figure 4.3. This inverter is powered by a constant 1.8V supply voltage providing an output swing from 0 to 1.8V. A simple resistor bias circuit is needed to bias the input of the inverter at around 0.9V. The output of the ring oscillator is AC coupled to the output stage by the capacitor C = 1000pF. Two VCOs in Figure 4.3 were built; the sample waveform of the

Figure 4.4: VCO output waveform for 1.6V and 2.1V input voltage

output is shown in Figure 4.4 and the characteristics were measured as shown in Figure 4.5. The analog input voltage ranges from 1.6V to 2.1V and the output

Figure 4.5: VCO V-to-f characteristic

frequency ranges from 40 MHz to about 140 MHz. It can be seen in the figure that the two VCOs have similar but not identical characteristics. Both of them are nonlinear; but the slopes df/dV only vary within about  $\pm 20\%$  of its average value which is given by:

$$K_{VCO(AVG)} = \frac{\Delta f}{\Delta V} \approx \frac{14\text{MHz} - 40\text{MHz}}{2.1V - 1.6V} = 200 \left[ \frac{\text{MHz}}{V} \right]$$

(4.2)

## 4.2 Frequency Divider

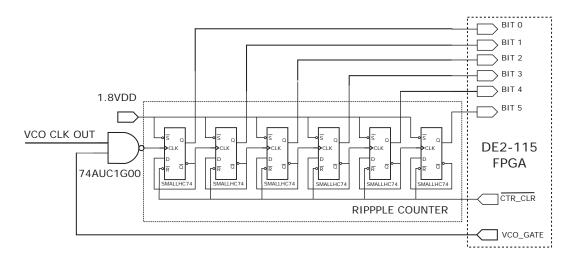

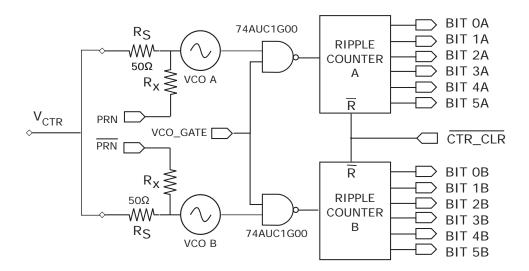

Although the digital calibration can be implemented solely using the FPGA board, a divider is built in order to reduce the frequency of the waveforms processed by the FPGA. This frequency divider can be considered as a part of the counter. In other words, the 12 bits counter is split into two 6 bit counters: one is constructed in the PCB, the other is implemented by the FPGA. The PCB schematic of the frequency divider is shown in Figure 4.6. As there is no correlation between the VCO output clock signal and the reset signal provided by the FPGA board, the ripple counter structure is used instead of the synchronous one.

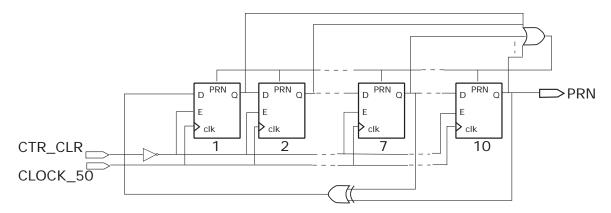

Figure 4.6: Ripple counter circuit schematic

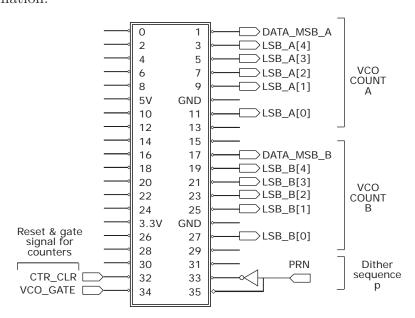

The circuit uses six dual positive edge triggered D-type flip-flops 74HC74. All six bit output signals of the ripple counter become the inputs to the FPGA board. The FPGA only needs to count the most significant bit signal "BIT 5" of which the frequency is 64 times smaller than that of the VCO output  $f_{VCO}$ .

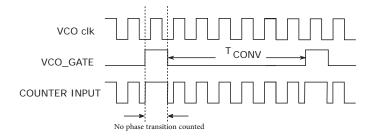

It should be noted that, in addition to the low enable reset signal  $\overline{\text{CTR\_CLR}}$  the counter also requires a gate signal VCO\_GATE. When VCO\_GATE = 1, the NAND gate inverts the VCO output clock signal; when VCO\_GATE = 0 the output of the NAND gate is always high. Therefore, no phase transition of the VCO output would be counted during the time when VCO\_GATE is high. This sets up a "break" time window for the FPGA to grab the data and reset the counter. The actual effective conversion time is only the period when VCO\_GATE is low.

Figure 4.7: Timing diagram of VCO\_GATE signal

### 4.3 PCB Design Summary

Figure 4.8 shows the complete block diagram implementation of the PCB for this project. The input voltage  $V_{IN}$  is split into two channels. The PRN signal represents a pseudo-random sequence of either 1 ( $V_{DD} = 1.8V$ ) or 0 (GND). The dither size can be controlled by the resistor  $R_x$  as follow:

$$2\Delta V = \frac{V_{DD}R_s}{(R_x + R_s)} \Rightarrow \Delta V = \frac{V_{DD}R_s}{2(R_x + R_s)}$$

$$(4.3)$$

Figure 4.8: PCB block diagram

The analog voltages are then converted to frequency domain using the two VCOs of which the V-to-f characteristics are shown in Figure 4.5. The two 774AUC1G00 NAND gates are then used to generate a break time window for the counter to grab the data and to reset. Two 6 bit ripple counters are constructed using six 74HC74 D-flip flops. The reset signal  $\overline{\text{CTR\_CLR}}$ , gate signal VCO\_GATE, and dither PRN are 0-1.8V digital signals provided by the FPGA board. The first five least significant bits of the two ripple counters are sampled by the FPGA, while the sixth bit signals

are then counted to get the last seven most significant bits of the VCO counts n. The detailed implementation of FPGA board are documented Chapter 5

## Chapter 5

# FPGA Implementation

The main focus of this project is to implement the calibration algorithm in an FPGA board. The board used in this project is DE2-115; and the algorithm is implemented in Altera - Quartus II 13.0. Although the whole calibration technique can be coded solely using Verilog, it is easier to implement each block separately using the schematic feature in Quartus II.

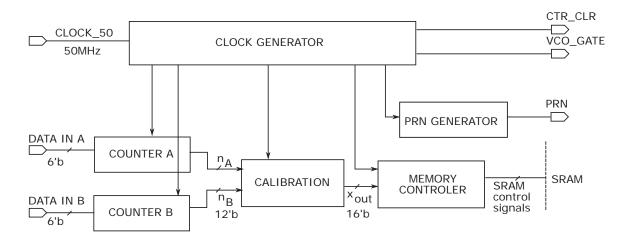

### 5.1 Top Level Block Diagram Design

This section describes a top design structure of the FPGA implementation for this project. The Quartus II CAD system supports a schematic design method in which the users draws a graphical diagram of the circuit. Each function can be implemented using one block diagram which then can be described by either a verilog source code file or a schematic design file. There are totally 6 blocks in the top level design:

• CLOCK GENERATOR: generate all the clock signals controlling the timing operation of other blocks and provide reset and gate signals for the PCB

- PRN GENERATOR: generate pseudo-random sequence p for the dither  $\Delta V$

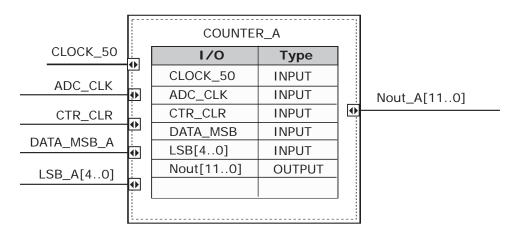

- COUNTER A: sample 5 LSB signals and count 7 MSBs of VCO A output

- COUNTER B: sample 5 LSB signals and count 7 MSBs of VCO B output

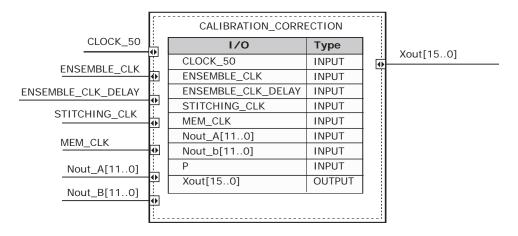

- CALIBRATION: perform the LUT correction and background calibration.

- MEMORY CONTROLLER: control the SRAM to store measured data

Figure 5.1: Simplified top level block diagram for FPGA implementation

Figure 5.1 captures the simplified block diagram of the FPGA implementation. All the clock signals are generated based on the 50MHz clock signal "CLOCK\_50" produced by an oscillator of the DE2-115 board. The two COUNTER blocks output 12 bit numbers  $n_A$  and  $n_B$  which are then corrected by the CALIBRATION block. The corrected output x has 16 bit and is written in the SRAM memory by the MEMORY CONTROLLER block.

The DE2-115 FPGA board interfaces with the designed PCB through a 40-pin expansion header. The voltage level of the I/O pins on the header is adjusted to 1.8V by the JP6 jumper. Figure 5.2 captures the inputs and outputs connected to each pin of the GPIO. The FPGA takes 12 output signals of the two frequency

dividers, implemented on the PBC, as the inputs and provides the reset, gate clock signals and the dither sequence p and  $\bar{p}$ . The DE2-115 Control Panel is used to performs all data transfers between the FPGA board and a host computer via the USB Blaster link. Readers are encouraged to refer to the DE2-115 user manual for more information.

Figure 5.2: GPIO input, output configuration

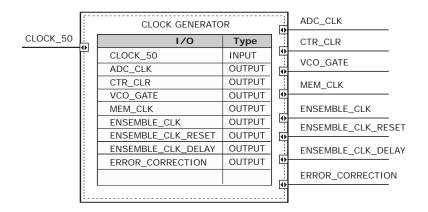

## 5.2 Clock Signal Generator

The first parameter that needs to be determined when implementing a clock generator is the sampling frequency  $f_s$ . For this project, since the frequency range of the VCO output is around 100MHz, in order to realize a 10 bit ADC with a redundancy factor R = 2 the sampling frequency is required to be:

$$f_s = \frac{\Delta f_{VCO}}{2^N R} \approx \frac{100 \text{MHz}}{2 \cdot 2^{10}} \approx 48.8 \text{MHz}$$

(5.1)

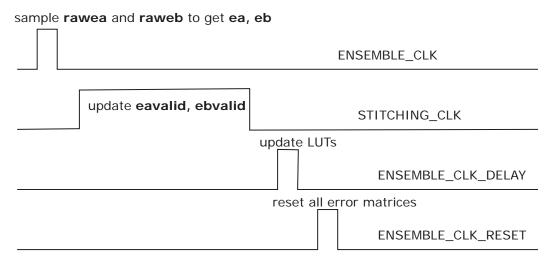

Figure 5.3 shows the CLOCK GENERATOR block. There are a total of 7 output

Figure 5.3: GPIO input, output configuration

signals produced which are listed below:

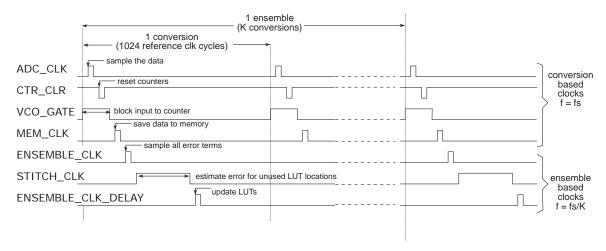

- ADC\_CLK: 48.8kHz main conversion clock of the ADC

- MEM\_CLK: 48.8kHz clock to control the MEMORY\_COTROLLER block

- CTR\_CLR: 48.8kHz reset signal to reset the counters

- VCO\_GATE: 48.8kHz gate window to block the VCO oscillated signal, "freezing" the counter outputs while the ADC samples data.

- ENSEMBLE\_CLK: 48.8 kHz/K clock to sample all the LUT error terms every K conversions

- STITCH\_CLK: 48.8kHz/K clock to perform the "stitching" error estimation for all unused LUT locations

- ENSEMBLE\_CLK\_DELAY: 48.8 kHz/K clock to updates the LUT every K conversions

All the clock signals are generated based on the 50MHz reference clock of the FPGA. The simplest way to divide a clock frequency is to count the number of rising edge of the reference clock. The maximum count of the counter determines the frequency of the output signal:

$$f_{out} = \frac{f_{REF}}{\text{Max count} + 1} = \frac{50 \text{MHz}}{\text{Max count} + 1}$$

(5.2)

In this project, a 10 bit counter with maximum output count of 1023 is used to realize the frequency of 48.8 kHz. To get the desired clock signals, the output of the counter is then compared to a reference count value. This value determines the relative delay of the output clocks. Figure 5.4 shows the timing diagram of all the input and output signals to the CLOCK GENERATOR block.

Figure 5.4: GPIO input, output configuration

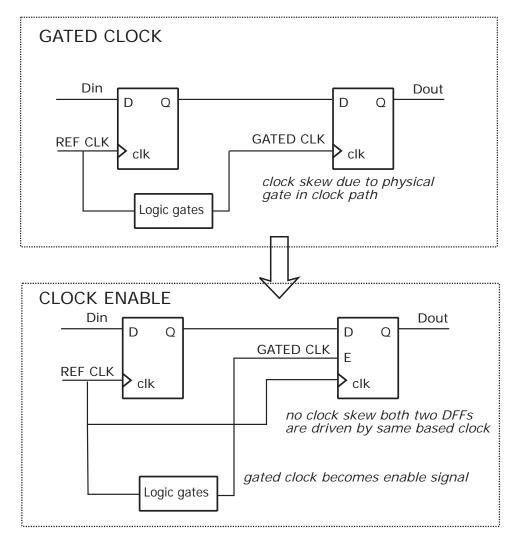

When implementing a complex clock network, eventually the design will introduce physical gates in the clock paths to control the downstream clocks. This is referred as "clock gating". These gates could introduce significant delay and cause large clock skew and lead to setup and hold-time violations [16]. Although the FPGA has a 50MHz low skew reference clock, it is not flexible enough to represent the clocking needs of a sophisticated design. When the global clock lines cannot naturally accommodate these physical gates, the place and route tools will be forced

to use other on-chip routing resources for the clock networks with inserted gates, usually resulting in large clock skews between different paths to destination registers. Additionally, using the detecting the rising edge of the clocks shown in Figure 5.4 is difficult. The main reason is because these clocks have very small duty cycles of less than 1%. Therefore, they might have relatively high noise and jitter. An unwanted ripple in the waveform my be miss-detected as a rising edge, resulting in inconsistency in the design.

Figure 5.5: Converting gated clocks to clock enables to eliminate clock skews

To overcome the two problems above, the "clock enable" method, illustrated in Figure 5.5, is applied in this project [16]. The gated clock is used as an enable signal of the flip flops. When the gated clock is to be switch "on", the sequential elements will be enabled and when the clock is to be switched "off", the sequential elements will be disabled. All the operations are performed at the rising edge of the reference clock, therefore, eliminating the large clock skews. Additionally, since the circuit functions when the the gated clock is high rather than at the rising edge of the gate clocks, it also solve the rising edge miss-detection problem mentioned earlier.

### 5.3 Dither Generator

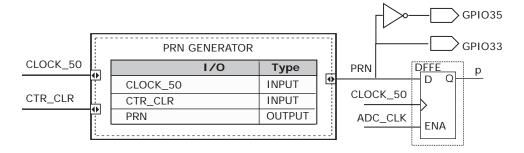

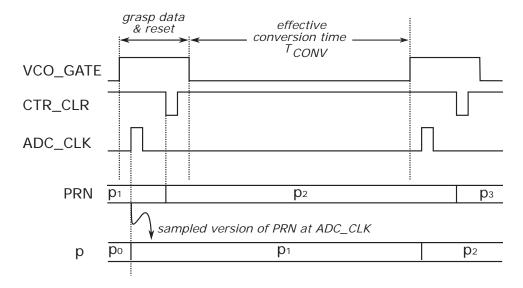

Figure 5.6: PRN GENERATOR block