#### ALL DIGITAL, BACKGROUND CALIBRATION FOR TIME-INTERLEAVED AND SUCCESSIVE APPROXIMATION REGISTER ANALOG-TO-DIGITAL CONVERTERS

by

Christopher Leonidas David

A Thesis Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

in

Electrical and Computer Engineering by

Christophen Leanidas

May 2010

APPROVED;

Professor John McNeill, Major Advisor

Professor Donald R. Brown

Doctor Michael Coln

#### Abstract

The growth of digital systems underscores the need to convert analog information to the digital domain at high speeds and with great accuracy. Analog-to-Digital Converter (ADC) calibration is often a limiting factor, requiring longer calibration times to achieve higher accuracy. The goal of this dissertation is to perform a fully digital background calibration using an arbitrary input signal for A/D converters. The work presented here adapts the cyclic "Split-ADC" calibration method to the time interleaved (TI) and successive approximation register (SAR) architectures.

The TI architecture has three types of linear mismatch errors: offset, gain and aperture time delay. By correcting all three mismatch errors in the digital domain, each converter is capable of operating at the fastest speed allowed by the process technology. The total number of correction parameters required for calibration is dependent on the interleaving ratio, M. To adapt the "Split-ADC" method to a TI system, 2M+1 half-sized converters are required to estimate 3(2M+1) correction parameters. This thesis presents a 4:1 "Split-TI" converter that achieves full convergence in less than 400 000 samples.

The SAR architecture employs a binary weight capacitor array to convert analog inputs into digital output codes. Mismatch in the capacitor weights results in non-linear distortion error. By adding redundant bits and dividing the array into individual unit capacitors, the "Split-SAR" method can estimate the mismatch and correct the digital output code. The results from this work show a reduction in the non-linear distortion with the ability to converge in less than 750 000 samples.

To My Family, My Friends, and My Lee Anne

#### Acknowledgements

It has been a great privilege to be a student of Professor John McNeill over the past six years. Over this period of time, I have worked on various projects including the Split-Interleaved and Split-SAR work on which this thesis is based. In each of these projects, he has provided me with invaluable guidance and insight in the field of analog integrated circuit design. His encouragement and assistance helped me through the most challenging aspects of my work. The annual trips to the International Sold-State Circuits Conference provided a first-hand glimpse at leading edge research in analog IC design. These trips inspired his graduate students to pursue a level of excellence and professional standard to match his own.

I would also like to thank my committee members, Professor D. Rick Brown and Dr. Michael Coln for their expertise and review of this work. Professor Brown's suggestions on algorithmic development and Dr. Coln's comments on circuit design were an important contribution to the thesis. In addition, I would like to thank Dr. Michael Coln's High Speed Converter group at Analog Devices, Inc. for their feedback on both the discrete and integrated circuit designs.

This work was carried out as part of the New England Center for Analog and Mixed Signal Design at WPI under the direction of Professor McNeill. The two Split-ADC projects were supported in part by NSF Award 0523996 and by Analog Devices, Inc.

This thesis represents research work that was carried out in collaboration with many colleagues at the Analog Lab in the Electrical and Computer Engineering Department at WPI, to which I owe my gratitude. Rosa Croughwell provided the layout design work for the integrated circuit version of the 4:1 Split-Interleaved architecture, to which I applied my calibration research. Chilann Chan, a colleague and a friend, developed the Split-SAR algorithm which was applied to ADC chip I worked on. Cody Brenneman was my partner throughout all of the trials and tribulations of the Split-SAR integrated circuit design. I could not have completed the project in such a timely and efficient manner without his help. I would like to thank my other colleagues in the lab, many of whom are also my friends, Tsai Chen, Ali Ulas Ilhan, Thomas Liechti, Chengxin Liu, Shant Orchanian, Altin Pelteku,

Alihusain Sirohiwala and Hattie Spetla.

In addition to the Analog Lab, there were several friends and colleagues in the Digital Lab and Machine Vision Lab who lent both moral and technical support. I would like to thank Jorge Alejandro, Vincent Amendolare, Matthew Campbell, Andrew Cavanaugh, Vivek Varshney and Benjamin Woodacre. Their guidance and friendship is greatly appreciated. Professor Fred Looft has been a great benefit as both the head of the Electrical and Engineering Department at WPI as well as my sailplane instructor.

Throughout my entire education, my family has been with me through the good time and the bad. Without their support, this thesis would not have been possible. Finally, I would like to thank my girlfriend Lee Anne Gerardi, for all of her love as well as her knowledge of the English language. Her encouragement and generous assistance in improving the readability of the thesis will not be forgotten.

## Contents

| List of Figures viii |       |                 |                                                                                                                                                        |           |  |  |  |

|----------------------|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| $\mathbf{Li}$        | st of | Tables          | 5                                                                                                                                                      | x         |  |  |  |

| 1                    | Intr  | oducti          | ion                                                                                                                                                    | 1         |  |  |  |

| <b>2</b>             | Bac   | kgrour          | ad                                                                                                                                                     | 6         |  |  |  |

|                      | 2.1   | ADC 0           | Characterization                                                                                                                                       | 6         |  |  |  |

|                      |       | 2.1.1           | Sampling Rate and Resolution                                                                                                                           | 6         |  |  |  |

|                      |       | 2.1.2           | Nonidealities and Nonlinearity                                                                                                                         | 9         |  |  |  |

|                      | 2.2   | ADC .           | Architectures                                                                                                                                          | 13        |  |  |  |

|                      |       | 2.2.1           | Flash Architecture                                                                                                                                     | 14        |  |  |  |

|                      |       | 2.2.2           | Cyclic Architecture                                                                                                                                    | 15        |  |  |  |

|                      |       | 2.2.3           | Pipelined Architecture                                                                                                                                 | 16        |  |  |  |

|                      |       | 2.2.4           | SAR Architecture                                                                                                                                       | 17        |  |  |  |

|                      |       | 2.2.5           | Time Interleaved Architecture                                                                                                                          | 19        |  |  |  |

| 3                    | Inte  | rleave          | d and SAR Architectures                                                                                                                                | <b>22</b> |  |  |  |

|                      | 3.1   | The T           | Time Interleaved Converter                                                                                                                             | 22        |  |  |  |

|                      |       | 3.1.1           | Offset Mismatch Error                                                                                                                                  | 23        |  |  |  |

|                      |       | 3.1.2           | Gain Mismatch Error                                                                                                                                    | 25        |  |  |  |

|                      |       | 3.1.3           | Aperture Delay Mismatch Error                                                                                                                          | 26        |  |  |  |

|                      |       | 3.1.4           | Bandwidth Mismatch Error                                                                                                                               | 29        |  |  |  |

|                      | 3.2   | The S.          | AR Converter                                                                                                                                           | 33        |  |  |  |

|                      |       | 3.2.1           | Operation of a Differential SAR                                                                                                                        | 33        |  |  |  |

|                      |       | 3.2.2           | Non-Idealities in a SAR Converter                                                                                                                      | 36        |  |  |  |

|                      |       | 3.2.3           | Incorrect Comparator Decisions                                                                                                                         | 36        |  |  |  |

|                      |       | 3.2.4           | Capacitor Weight Mismatch                                                                                                                              | 38        |  |  |  |

| 4                    | AD    | ADC Calibration |                                                                                                                                                        |           |  |  |  |

|                      | 4.1   | Time            | Interleaved ADC Calibration                                                                                                                            | 41        |  |  |  |

|                      | 4.2   | SAR A           | A/D Calibration $\ldots \ldots \ldots$ | 45        |  |  |  |

|                      | 4.3   | The S           | plit-ADC Architecture                                                                                                                                  | 49        |  |  |  |

| <b>5</b>                         | Spli  | Interleaved ADC                              | <b>53</b> |  |  |  |

|----------------------------------|-------|----------------------------------------------|-----------|--|--|--|

|                                  | 5.1   | Digital Error Correction                     | 53        |  |  |  |

|                                  | 5.2   | Split-ADC and the Time Interleaved Converter | 54        |  |  |  |

|                                  |       | 5.2.1 Digital Derivative Estimate            | 59        |  |  |  |

|                                  |       | 5.2.2 The LMS Calibration                    | 60        |  |  |  |

|                                  | 5.3   | Simulation Results                           | 63        |  |  |  |

|                                  |       | 5.3.1 MATLAB Simulation                      | 64        |  |  |  |

|                                  |       | 5.3.2 IC Layout Simulation                   | 69        |  |  |  |

| 6                                | Spli  | SAR ADC                                      | 72        |  |  |  |

|                                  | 6.1   | Applying the Split-ADC to the SAR Converter  | 72        |  |  |  |

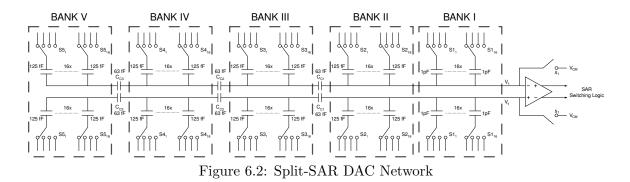

|                                  |       | 5.1.1 Modifying the SAR DAC Network          | 73        |  |  |  |

|                                  |       | 6.1.2 Split-SAR Error Calibration            | 76        |  |  |  |

|                                  | 6.2   | Split-SAR IC Design                          | 81        |  |  |  |

|                                  |       | 5.2.1 Split-SAR IC Overview                  | 81        |  |  |  |

|                                  |       | 5.2.2 Split-SAR Analog Circuit               | 82        |  |  |  |

|                                  |       | 5.2.3 Split-SAR Digital Logic                | 88        |  |  |  |

|                                  | 6.3   | Split-SAR Results                            | 92        |  |  |  |

| 7                                | Cor   | lusions                                      | 100       |  |  |  |

|                                  | 7.1   | Future Work                                  | 101       |  |  |  |

| G                                | lossa | /                                            | 102       |  |  |  |

| $\mathbf{A}$                     | Spli  | Interleaved MATLAB Code                      | 105       |  |  |  |

| в                                | Spli  | SAR MATLAB Code                              | 129       |  |  |  |

|                                  | •     |                                              |           |  |  |  |

| C Split-SAR Hardware Description |       |                                              |           |  |  |  |

| Bibliography                     |       |                                              |           |  |  |  |

# List of Figures

| 1.1  | Block Diagram of an Analog Oscilloscope                                      | 2  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Block Diagram of a Digital Sampling Oscilloscope                             | 3  |

| 1.3  | Block Diagram of a 2:1 Time-Interleaved ADC                                  | 4  |

| 2.1  | Ideal ADC Transfer Characteristic                                            | 7  |

| 2.2  | ADC Quantization Error Characteristic                                        | 8  |

| 2.3  | ADC Transfer Function with Offset and Gain Error.                            | 9  |

| 2.4  | ADC Transfer Function with Nonlinearity.                                     | 10 |

| 2.5  | ADC DNL and INL                                                              | 12 |

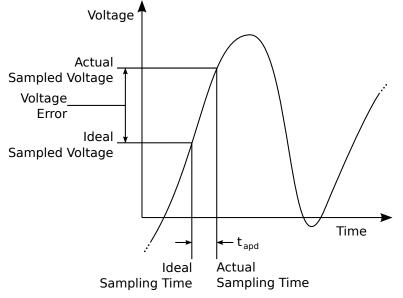

| 2.6  | The Effects of Aperture Delay on the Sampled Voltage                         | 13 |

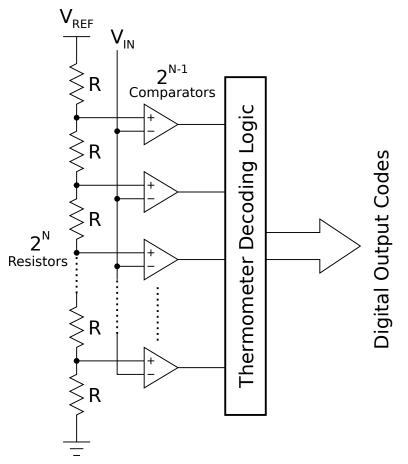

| 2.7  | Block Diagram of a Flash ADC                                                 | 14 |

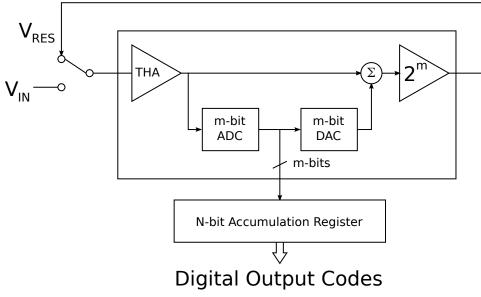

| 2.8  | Block Diagram of a Cyclic ADC                                                | 15 |

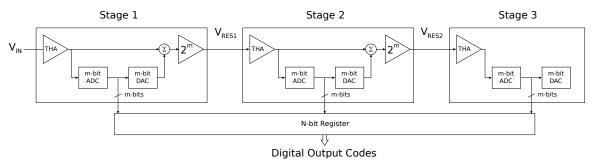

| 2.9  | Block Diagram of a Pipelined ADC                                             | 17 |

| 2.10 | Basic Operation of a SAR ADC                                                 | 18 |

| 2.11 | Block Diagram of a Time Interleaved ADC                                      | 20 |

| 3.1  | Effects of time interleaved channel mismatch on an input signal              | 23 |

| 3.2  | Block Diagram of 4:1 Time Interleaved Converter with Offset Error Introduced | 24 |

| 3.3  | 4:1 Time Interleaved Output Spectrum with Offset Errors                      | 25 |

| 3.4  | Block Diagram of 4:1 Time Interleaved Converter with Gain Error Introduced   | 26 |

| 3.5  | 4:1 Time Interleaved Output Spectrum with Gain Errors                        | 27 |

| 3.6  | Block Diagram of 4:1 Time Interleaved Converter with Aperture Delay Error    |    |

|      | Introduced                                                                   | 28 |

| 3.7  | 4:1 Time Interleaved Output Spectrum with Aperture Delay Errors              | 29 |

| 3.8  | Plot of Bandwidth Mismatch for Multiple Input Frequencies                    | 32 |

| 3.9  | Block Diagram of a Differential SAR                                          | 34 |

| 3.10 | Basic Circuit Operation of a Differential SAR                                | 35 |

| 3.11 | DAC Voltage Waveform of the Differential SAR                                 | 36 |

|      | DAC Voltage Waveform of the SAR with Redundant Bit and Recovery              | 37 |

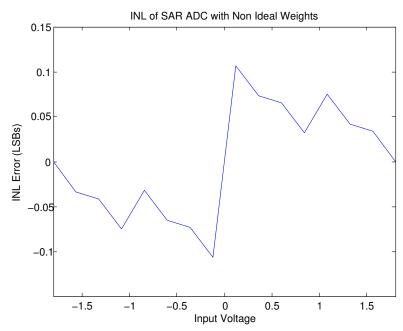

|      | INL of Non-Ideal SAR Converter                                               | 39 |

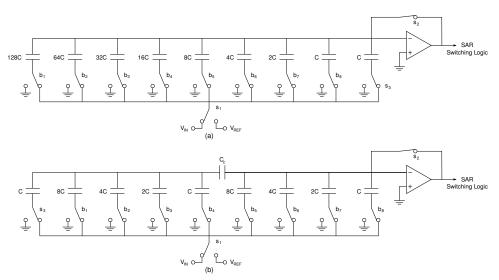

| 4.1  | (a) An 8-bit SAR with straight binary weighted DAC                           |    |

|      | (b) An 8-bit SAR with a Coupling Capacitor DAC                               | 46 |

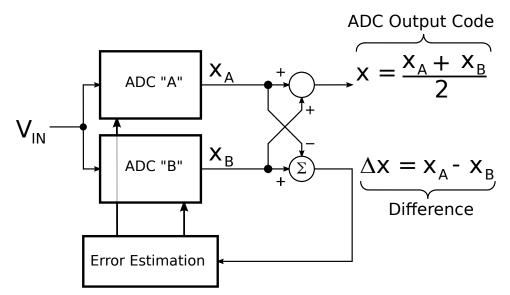

| 4.2  | Block Diagram of Split-ADC Architecture                                    |

|------|----------------------------------------------------------------------------|

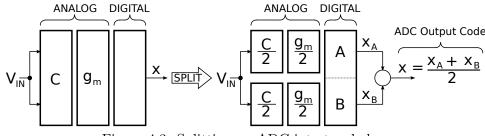

| 4.3  | Splitting an ADC into two halves                                           |

|      |                                                                            |

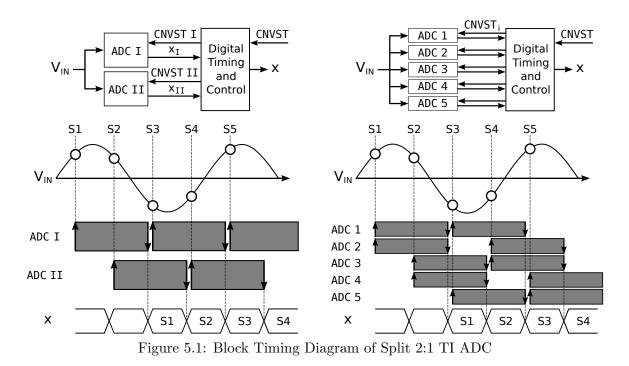

| 5.1  | Block Timing Diagram of Split 2:1 TI ADC 55                                |

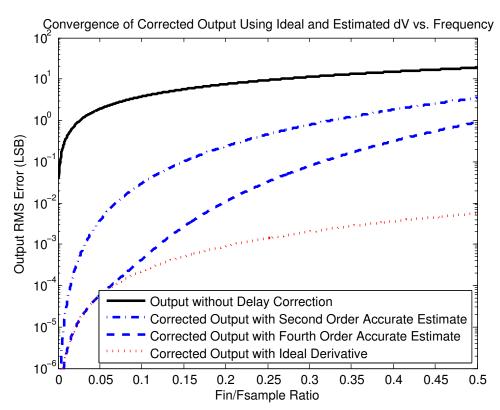

| 5.2  | Comparison of Derivative Estimates used for Error Correction 61            |

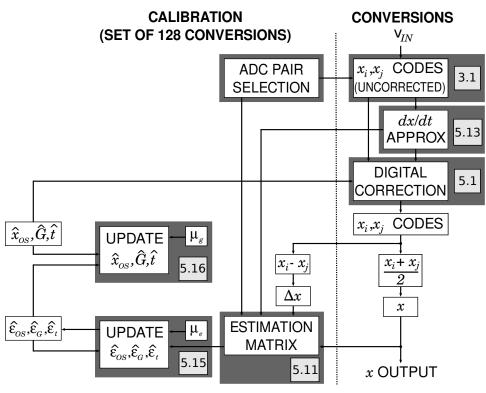

| 5.3  | Error Estimation Algorithm and Correction                                  |

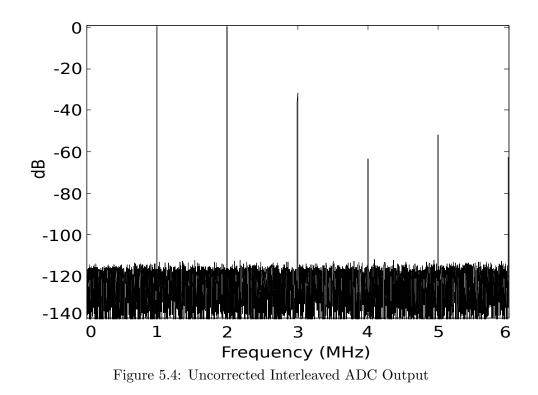

| 5.4  | Uncorrected Interleaved ADC Output                                         |

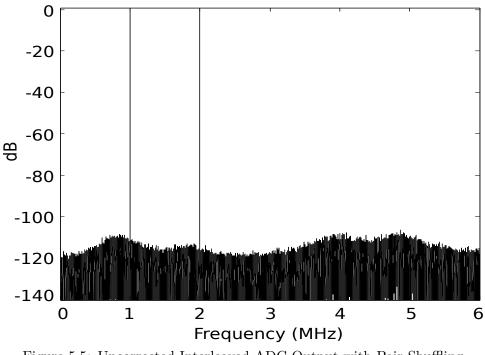

| 5.5  | Uncorrected Interleaved ADC Output with Pair Shuffling                     |

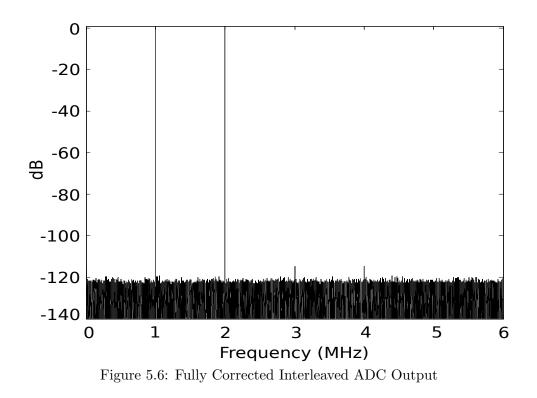

| 5.6  | Fully Corrected Interleaved ADC Output    67                               |

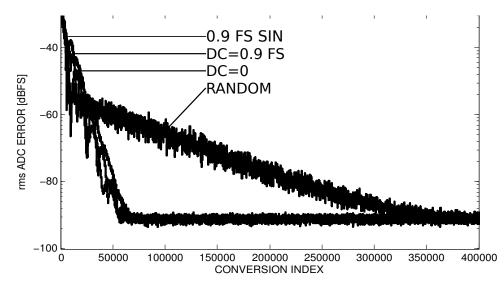

| 5.7  | Calibration Convergence for Sinusoidal, DC, and Random Input Signals 68    |

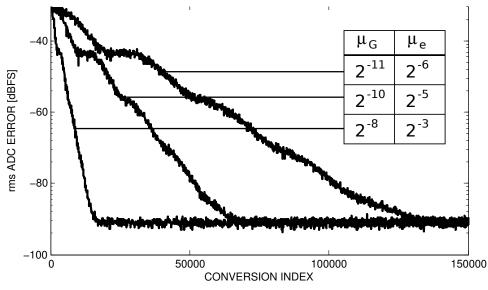

| 5.8  | Calibration Convergence for Different LMS Parameters                       |

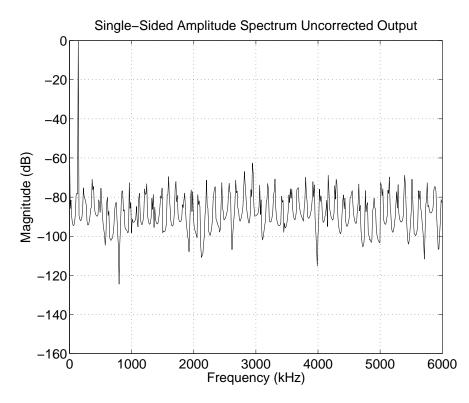

| 5.9  | FFT of Uncorrected Sine Wave $f_{in} = 140.625 kHz$                        |

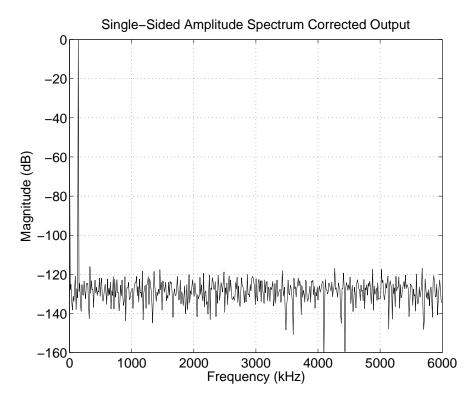

| 5.10 | FFT of Corrected Sine Wave $f_{in} = 140.625 kHz$                          |

|      |                                                                            |

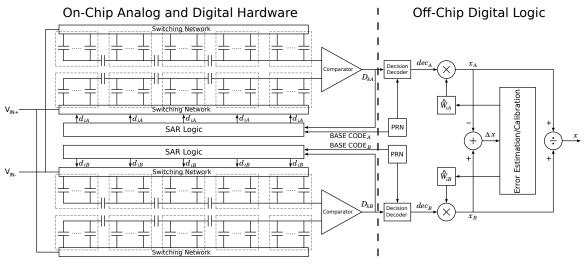

| 6.1  | Split-SAR Block Diagram    73                                              |

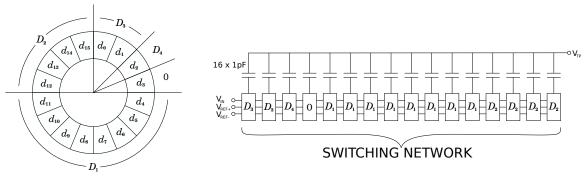

| 6.2  | Split-SAR DAC Network                                                      |

| 6.3  | Split-SAR Bank Capacitor Selection    75                                   |

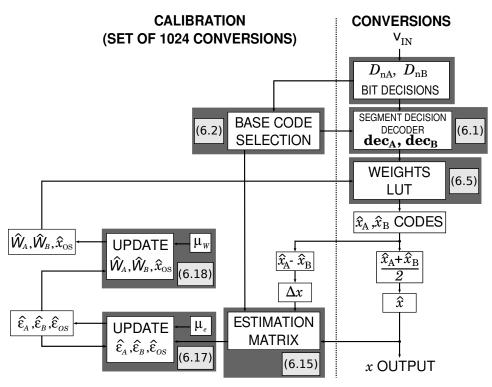

| 6.4  | Split-SAR Error Estimation Algorithm and Correction       78               |

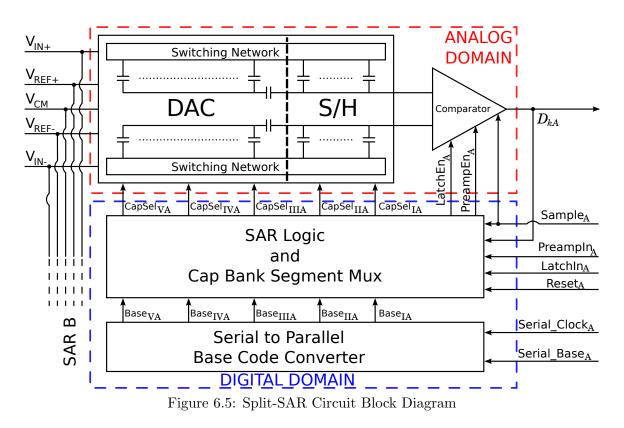

| 6.5  | Split-SAR Circuit Block Diagram    82                                      |

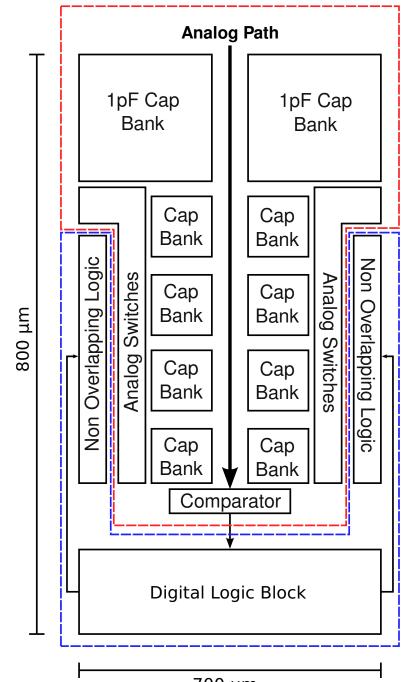

| 6.6  | Split-SAR Layout Floor Plan    83                                          |

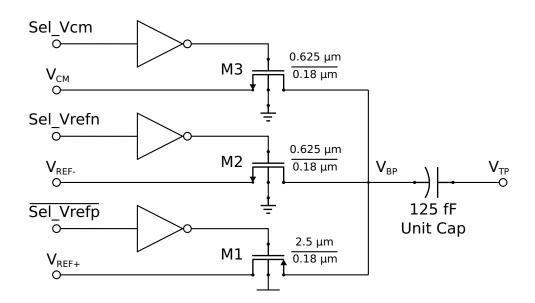

| 6.7  | Switching Circuit for 125 fF Capacitors                                    |

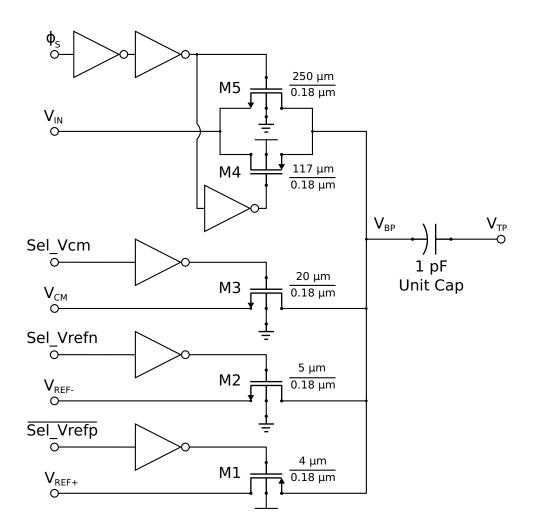

| 6.8  | Switching Circuit for 1 pF Capacitors                                      |

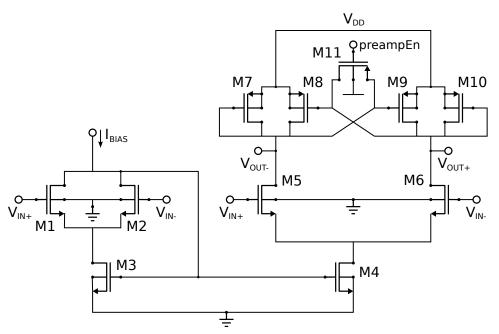

| 6.9  | Preamplifier Single Stage Schematic                                        |

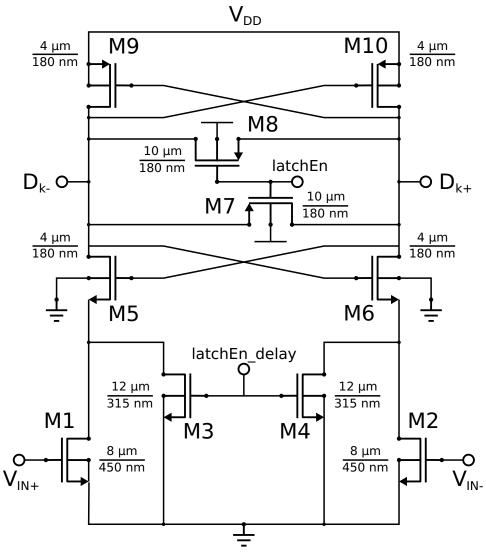

|      | Preamplifier Regenerative Latch                                            |

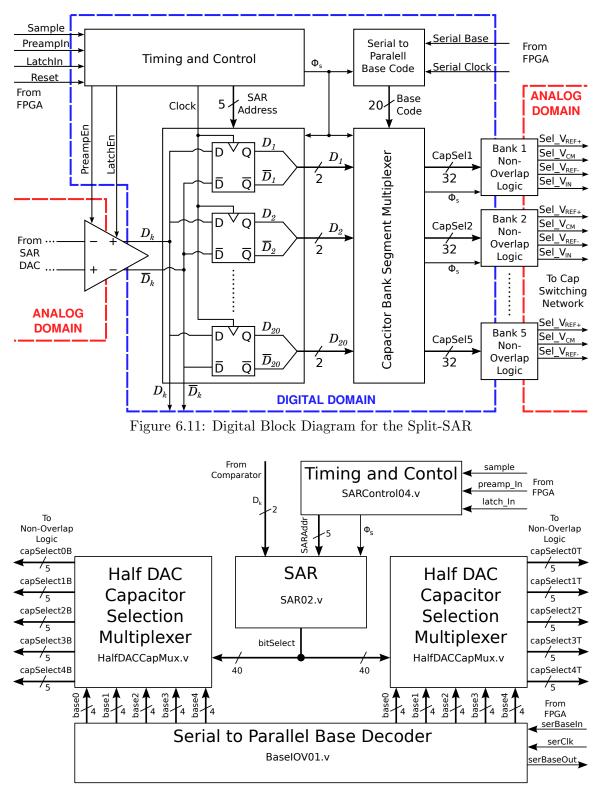

|      | Digital Block Diagram for the Split-SAR                                    |

|      | Digital Circuit Hierarchy Block Diagram                                    |

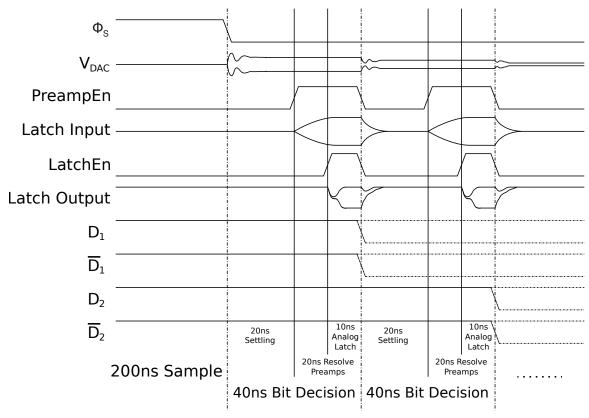

| 6.13 | Timing Diagram of Control Signals    91                                    |

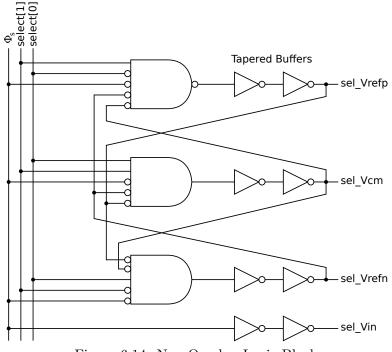

|      | Non-Overlap Logic Block                                                    |

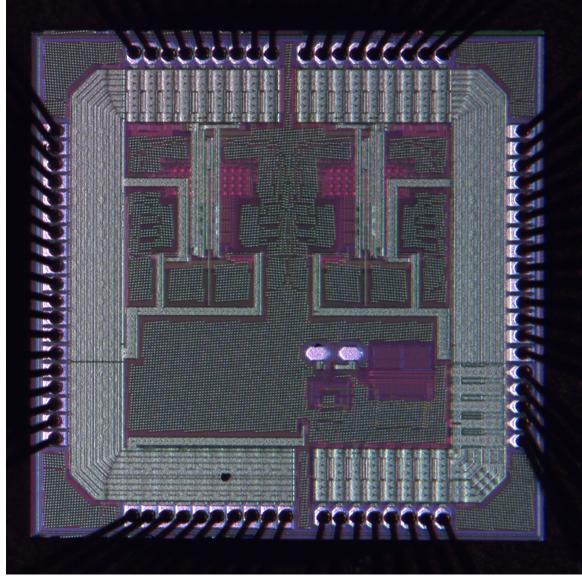

| 6.15 | Die Photo of Split-SAR                                                     |

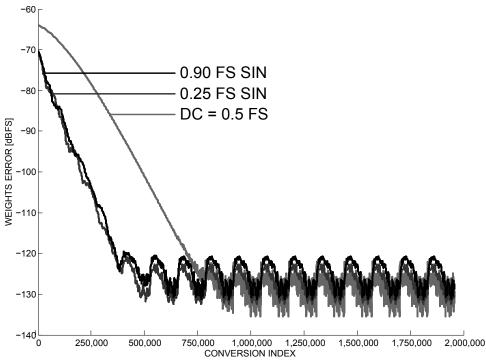

| 6.16 | Split-SAR Algorithm Convergence with Different Waveforms 95                |

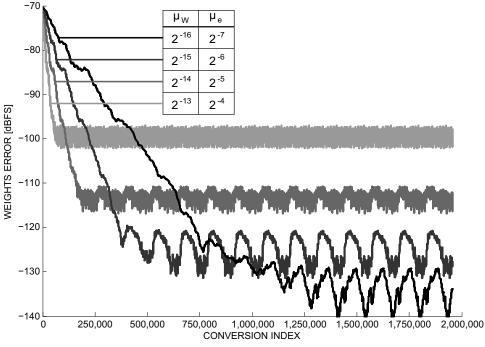

| 6.17 | Split-SAR Algorithm Convergence with Different LMS Parameters 96           |

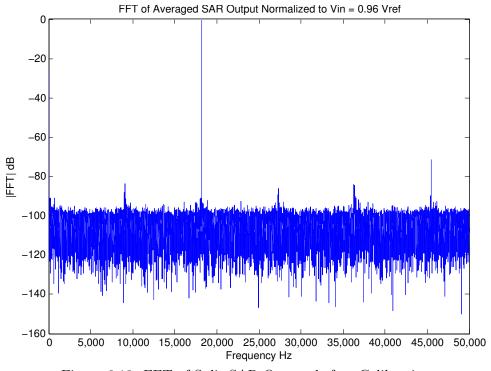

| 6.18 | FFT of Split-SAR Output before Calibration                                 |

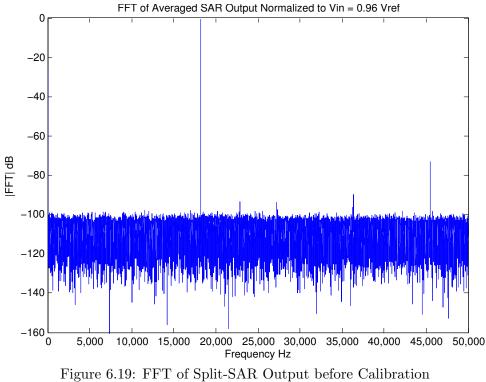

| 6.19 | FFT of Split-SAR Output before Calibration                                 |

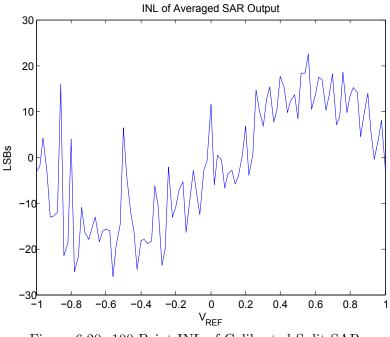

| 6.20 | 100 Point INL of Calibrated Split-SAR                                      |

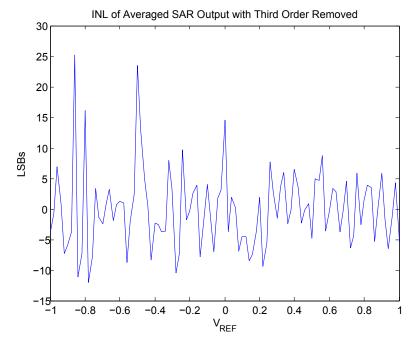

| 6.21 | 100 Point INL of Calibrated Split-SAR with Third Order Effect Removed . 99 |

## List of Tables

| 3.1 | Table of DAC Voltages for a Single Conversion                     | 34 |

|-----|-------------------------------------------------------------------|----|

| 3.2 | Table of DAC Voltages for a SAR Conversion with Decision Recovery | 38 |

| 3.3 | Table of Ideal and Non-Ideal DAC Weights                          | 39 |

| 4.1 | Comparison of Previous Calibration Techniques                     | 49 |

| 5.1 | Behavioral Simulation Parameters                                  | 64 |

| 6.1 | Transistor Sizes for the Preamplifier Stages                      | 87 |

### Chapter 1

### Introduction

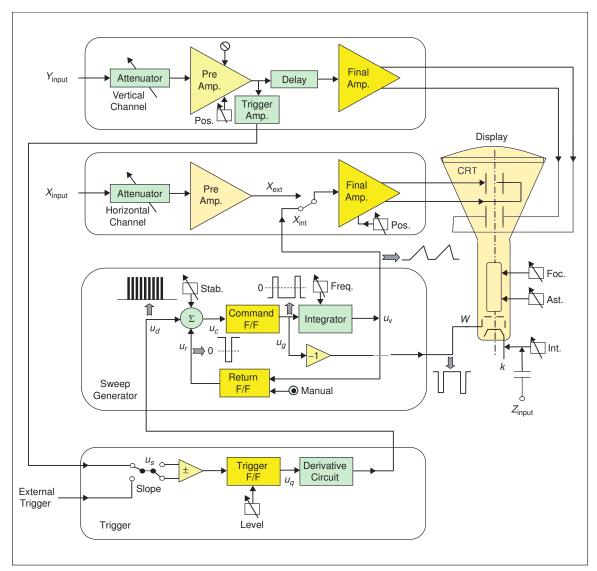

One of the most common themes in electrical engineering is the transmission, storage and processing of data. Early forms of this handled data in the analog domain, by manipulating signals with analog components such as resistors, capacitors, inductors, and amplifiers. This can be found in examples such as early analog oscilloscopes used for test and measurement. Figure 1.1 shows a block diagram of an analog oscilloscope which uses only components in the analog domain such as attenuators, amplifiers and delay circuits [1]. These types of oscilloscopes, while essential for analog circuit evaluation, had limited abilities in signal processing, analysis, and display abilities. The Cathode Ray Tube (CRT) could only display the input signal in real-time and didn't have the ability to store an input waveform for postanalysis [1].

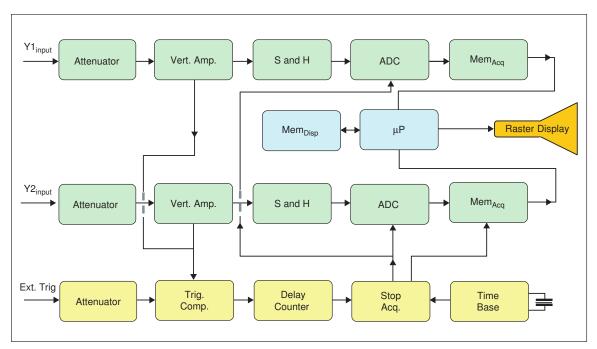

With the advent of digital computing, there has been a tremendous shift of signal processing and storage from analog to the digital domain. To extend the example of the oscilloscope, the quantization and Data Acquisition (DAQ) of digital sampling oscilloscopes allowed for more advanced analysis [1]. Figure 1.2 shows how an input signal is minimally processed and filtered before being sampled and quantized by an Analog-to-Digital Converter (ADC). The digitized waveform can then be processed, sorted, analyzed and displayed entirely in the digital domain [1]. Both analog and digital scopes are capable of simple analysis such as measuring peak voltage (V<sub>pk</sub>) and frequency. However, digital scopes can perform statistical analyses and generate frequency spectrum plots of analog

Figure 1.1: Block Diagram of an Analog Oscilloscope

Figure 1.2: Block Diagram of a Digital Sampling Oscilloscope

waveforms [1].

When analog signals are transferred to the digital domain, the performance of the Digital Signal Processing (DSP) is limited by the accuracy of the Analog to Digital Converter (ADC) used. As the amount of data bandwidth has increased over the years, so has the speed, resolution and overall precision required of ADCs. Unfortunately, physical limitations and variations in the semiconductor fabrication process introduces sources of error into the A/D converters [2]. In order to increase their performance, much research has been done to calibrate out and correct for these inherent errors. The work presented here looks into two types of converter, time interleaved and Successive Approximation Register ADCs. These two A/Ds each have their own types of unique errors that must be corrected.

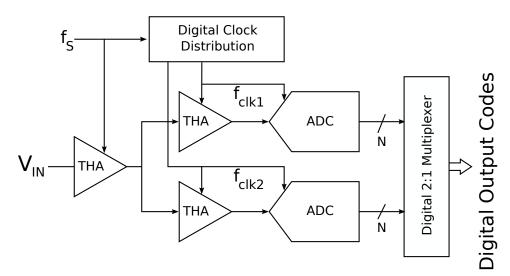

The Time Interleaved (TI) A/D is a technique that uses multiple converters to increase the throughput of the data. The interleaving method has some flexibility because it uses existing ADC architectures. It is capable of achieving faster conversion speeds than what a given technology would allow for a single converter [3]. Interleaving converters are often used in applications such as instrumentation. Typical TI systems use M sub-ADCs that each operate at 1/M the master sampling rate,  $f_S$ . The M digital output codes are then

Figure 1.3: Block Diagram of a 2:1 Time-Interleaved ADC

multiplexed into a single stream of digital codes. A 2:1 example of which is shown in Figure 1.3 [2]. Mismatch between the sub-ADCs produces three types of errors, offset, gain, and aperture time delay which affect all interleaved A/Ds. These errors are often dealt with using a combination of analog and digital calibration techniques [2, 4, 3].

Successive Approximation Register ADCs use a binary search algorithm with a charge redistribution network to convert an analog input into a digital output. Use of capacitors in a binary weighted redistribution network help the SAR achieve moderate to high resolutions with relatively low power [5, 6, 7]. The mismatch between these capacitors leads to nonlinearity errors in the digital output code. The traditional technique for correcting this error source is to use a calibration DAC to offset the charge mismatch [7, 8]. This calibration still requires a method for measuring ratio errors of the binary weighted capacitors.

The goal of this work is to apply a self-calibrating algorithm to both the time interleaved and SAR converters. This algorithm uses the Split-ADC method introduced in [9, 10]. Most recent calibration techniques are performed using a digital logic, however they often require foreground operation or statistical methods to achieve full convergence. The Split-ADC performs the calibration and correction completely in the digital domain, while operating in the background and achieving a deterministic convergence rate. The original Split-ADC algorithm was used to estimate only two correction parameters. Both the time interleaved and the SAR converters require a much larger number of correction parameters to be found. The majority of this research focused on adapting the Split-ADC method to calibrate the multiple parameters needed for these two architectures.

This thesis is organized as follows; Chapter 2 describes the performance metrics used to characterize ADCs. It then goes on to introduce the different types of architectures, their trade-offs, and the applications they are best suited for. Chapter 3 describes the interleaved and SAR architectures in more detail, as well as error sources and their affects on the output code. Chapter 4 discusses the work done using previous calibration techniques, including the Split-ADC method and its advantages over other methods. Chapter 5 presents what work has been to adapt the Split-ADC algorithm to a time interleaved converter and the results from simulation. Chapter 6 reviews the Split-SAR algorithm presented in [11], the design of the integrated circuit used for this research and the results from the fabricated chip. Finally, Chapter 7 concludes the research work presented here and provides possible paths for future designs.

### Chapter 2

### Background

A wide variety of analog to digital converters exist with each type suited for different applications. Section 2.1 describes the characterization of ADCs, in order to determine which ADC architecture to use for a given application. Section 2.2 describes different ADC architectures and their trade-offs in characteristics.

#### 2.1 ADC Characterization

There are several characteristics of A/D converters that measure their performance. These are useful in determining which type of ADC to use for a target application. This section will discuss the parameters of conversion speed and resolution, integral and differential nonlinearity (INL and DNL), total harmonic distortion (THD), and signal to noise and distortion ratio (SNDR).

#### 2.1.1 Sampling Rate and Resolution

The sampling rate of an ADC is used to determine the number of analog to digital code conversions that are completed within a specific period. Typically, this is measured in samples per second, such as 1 MS/sec showing that 1 million samples are collected within one second. This sampling rate is equal to the master sampling clock frequency for Nyquist rate ADCs. For these converters, the clock frequency must be greater than twice the highest frequency component in the analog input signal [12].

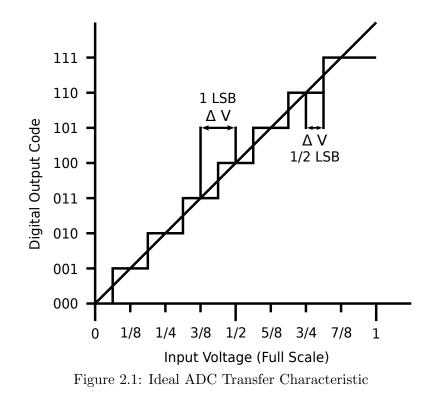

The resolution of an analog to digital converter describes how many quantization levels the ADC can represent. Since the output of an ADC is in binary format, the resolution is given in powers of 2. For example, a 10-bit A/D converter can represent an analog signal using  $2^{10}$  or 1024 quantization levels. As a general rule with Nyquist rate ADCs, there is a trade-off between sampling rate and converter accuracy and resolution. As the sampling rate increases, the converter resolution must be reduced in order to complete the conversion in a shorter period of time [12].

A single quantization level is the smallest analog voltage level that an ADC can resolve. This is called the Least Significant Bit, or LSB. The analog voltage value of the LSB is determined by the ADC resolution and the full scale voltage range,  $V_{FS}$ :

$$1 \text{ LSB} = \frac{V_{FS}}{2^N} \tag{2.1}$$

A transition level is the point from one quantization level to the next. The distance between two consecutive transition points is equal to a single quantization level or 1 LSB. Some input voltage changes are small enough to occur between the transition levels without crossing

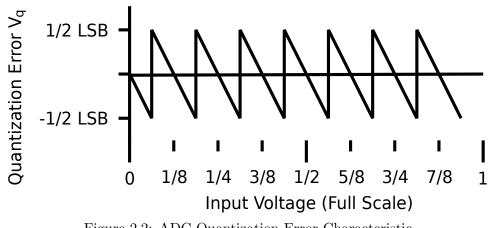

Figure 2.2: ADC Quantization Error Characteristic

them. These small changes are not detectable by the converter. This finite limit is referred to as the quantization error or noise in the A/D.

If an ideal transfer function of an ADC is compared to an ideal analog ramp, there is a difference of  $\pm \frac{1}{2}$  LSB. This quantization noise signal has an average value of zero, but its Root Mean Squared (RMS) value can be shown as:

$$(\text{RMS})V_q \approx \frac{1 \text{ LSB}}{\sqrt{12}} = \frac{V_{FS}}{2^N \sqrt{12}}$$

(2.2)

[12, 13]

The ideal dynamic range of an A/D is the maximum Signal-to-Noise Ratio (SNR), or the ratio from the largest to the smallest analog signal the converter can represent. The SNR for signals with a uniform distribution from 0 to  $V_{FS}$  can be shown as a ratio of  $V_{FS}$ to 1 LSB [12, 5, 13].

Dynamic Range (dB) =

$$20 \log \left( \frac{V_{FS}}{1 \text{ LSB}} \right) = 20 \log \left( 2^N \right) \approx 6.02N$$

(2.3)

However, since most input signals are sinusoidal with a non-uniform distribution, the maximum SNR is more commonly represented as the ratio of the AC power of the input to 1 LSB [5].

Dynamic Range (dB) =

$$20 \log \left( \frac{V_{FS}/(2\sqrt{2})}{1 \text{ LSB}} \right) \approx 6.02N + 1.76$$

(2.4)

Figure 2.3: ADC Transfer Function with Offset and Gain Error.

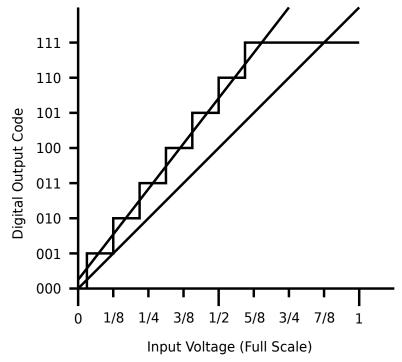

#### 2.1.2 Nonidealities and Nonlinearity

The ideal analog to digital converter has a linear transfer function within  $\pm \frac{1}{2}$  LSB as previously shown in Figure 2.1. Real converters produce errors due to non ideal devices and component mismatch. The most common types of errors are offset, gain, and nonlinearity. Offset error represents a fixed difference between the output and input signals. Gain error (or scaling factor) occurs when the slope of the real transfer function is different from the ideal transfer function. These two errors can be calibrated in hardware or software using y = Ax + b.

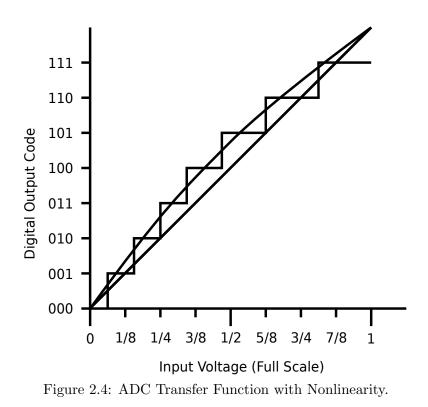

In an ideal case, each quantization step of a converter is equal to 1 LSB. However, in a real converter this is not always the case and any deviation from 1 LSB is measured as Differential Nonlinearity (DNL). The deterministic approach to measuring this error is defined as

$$DNL[i] = \frac{V_{i+1} - V_i}{V_{LSB}} - 1$$

(2.5)

where *i* is the quantization code level [13]. For example, if the output changes levels when the analog input increases by only 3/4 LSB, then the DNL for that transition is -1/4 LSB. Each transition has an associated DNL value that can be greater than or equal to -1 as seen in Equation 2.5. In the case where the DNL is -1, the transition never occurs. When the DNL exceeds +1, the quantization level is skipped completely, which results in a missing code [12, 13].

A different approach to finding the DNL of a converter is to perform a statistical analysis using an input signal with a known probability density function (pdf). The most common input signal used is a sinewave which has an ideal pdf of

$$f_S(v) = \frac{1}{\pi \sqrt{V_{pk}^2 - v^2}}$$

(2.6)

where v represents the input voltage and  $V_{pk}$  represents the amplitude [14]. By integrating the pdf over all code levels or bins, the ideal probability value for each bin can be calculated

11

as P(i).

$$P[i] = \frac{1}{\pi} \left[ \arcsin\left(\frac{V_{FS} \times (i - 2^{N-1})}{2^N V_{pk}}\right) - \arcsin\left(\frac{V_{FS} \times (i - 1 - 2^{N-1})}{2^N V_{pk}}\right) \right]$$

(2.7)

Equation 2.7 requires the code level, i, the resolution of the A/D, N, the full scale voltage for the converter,  $V_{FS}$ , and the amplitude of the sinewave,  $V_{pk}$ . The DNL for each code can be found by comparing the deviation between the measured histogram for each code of the converter, MP[i], to the ideal histogram P[i] [14].

$$DNL[i] (LSB) = \frac{MP[i]}{P[i]} - 1$$

(2.8)

The summation of DNL measurements is referred to as the Integral Nonlinearity (INL). Using the individual DNL measurements from Equation 2.5 or 2.8, the INL can be shown as the sum of the DNL errors.

$$INL[k] = \sum_{i=0}^{k} DNL[i]$$

(2.9)

This can be shown as a nonlinear transfer function of the A/D as shown in Figure 2.4. A plot of the INL can be made by taking the difference of the converter transfer function from the best linear fit of the two endpoints.

While individual DNL errors may be less than 1/2 LSB, the summation can result in INL error greater than 1/2 LSB. This is important to note because a 16-bit ADC that is still capable of resolving an LSB voltage change may have an overall accuracy of the converter less than 16-bit [15]. Figure 2.4 shows how the individual DNL errors can result in a large INL error.

Nonlinearity errors result in harmonic distortion in the frequency domain. This is measured as Total Harmonic Distortion (THD) which is the sum of the power of the harmonics divided by the power of the fundamentals. The THD measurement can be added to the SNR value to calculate the Signal to Noise and Distortion Ratio (SNDR). This SNDR value provides one type of measurement of the overall accuracy of the analog to digital converter.

The Effective Number of Bits (ENOB) is another method of measuring the overall

accuracy of an A/D. Using the ideal SNR Equation 2.4 the ENOB can be calculated from the measured SNDR.

$$ENOB = \frac{SNDR - 1.76}{6.02}$$

(2.10)

The overall accuracy presented in this format makes it easier to compare the real ADC's performance to its ideal resolution.

Aperture delay error is one more type of nonideality. There is always a delay from the time the ADC is told to capture a new sample to the time the converter acquires the sample. This delay is composed of a finite, deterministic delay and a varying, random delay. The finite delay component is due to such factors as signal path length and digital circuit propagation. The random component is called clock jitter, which is caused by phase noise in the sample clock generator circuit. The clock jitter component is a concern for all ADCs as too much jitter can affect the noise floor of the converter. The maximum clock jitter requirement is dependent on both the quantization level and the input signal frequency.

$$\Delta t = \frac{1}{2^N \pi f_o} \tag{2.11}$$

Figure 2.6: The Effects of Aperture Delay on the Sampled Voltage

The fixed deterministic component of aperture delay does not affect most converters. While clock jitter is a varying delay, the deterministic component of aperture delay does not affect the absolute sample period, since most ADCs are time invariant. The one exception to this is a time interleaved architecture. A time interleaved architecture is made of multiple ADC channels to create a single, high-speed converter system. Any difference in the signal paths between each ADC channel in a TI system will result in different fixed aperture delays. This results in a master sampling period that changes based on which ADC channel is used. The effects of this fixed delay on a TI architecture will be discussed further in Chapter 3.

#### 2.2 ADC Architectures

Nyquist rate converters are designed using a variety of different architectures. Each type of architecture design has its advantages and disadvantages which makes them suitable for different applications. As stated earlier, Nyquist rate architectures have a common trade-off between sampling rate and resolution. This makes architectures with high speeds and low resolutions well suited for applications such as video imaging, while high resolution paired with slower speeds are more suited for measurement systems.

Figure 2.7: Block Diagram of a Flash ADC

#### 2.2.1 Flash Architecture

The flash ADC architecture is one of the more commonly used converters [2, 7]. The basic design of the flash A/D uses a comparator for every quantization level in order to compare an input voltage with a series of reference voltages. These voltages are typically generated using a single reference input and a voltage divider resistor ladder. The analog input signal is then fed to the negative input of each converter while the reference voltage is fed to the positive input. This results in a thermometer code output, where all comparators with reference voltages greater than the input voltage will output a logic '1' and vice versa. A digital decoder circuit is required to translate the thermometer code into a binary weighted output code [5, 2].

This type of setup requires  $2^N - 1$  comparators, making a high-resolution flash ADC

Figure 2.8: Block Diagram of a Cyclic ADC

impractical. For example, an 8-bit converter would require 255 comparators, placing large demands on both die area and power consumption. However, the converter speed is directly dependent on the propagation delay from the analog input signal to the output of the comparators (and subsequent thermometer to binary logic). For this reason, normal flash ADCs are used in applications such as video imaging and wide band radio transceivers where speed is preferred over resolution [15, 16, 6].

#### 2.2.2 Cyclic Architecture

While the flash ADC is useful on its own, there are several architectures that use the flash to achieve higher resolutions. The cyclic ADC uses a low resolution flash converter with a negative feedback loop that operates over multiple internal cycles. The block diagram in Figure 2.8 shows the function of the cyclic converter [12].

For the first cycle, the frontend multiplexer switch selects the analog input voltage to be held on the track and hold circuit. This voltage held on the track and hold circuit is quantized by a small resolution, m-bit flash converter while simultaneously fed to a subtracter circuit. The m-bit digital code from the flash is then sent to a m-bit DAC. The analog voltage from the DAC is subtracted from the analog voltage held by the track and hold circuit which, generates a small residue voltage. This small voltage is then amplified with a gain of  $2^m$  to produce a larger residue voltage,  $V_{RES}$ . For the next cycle, the frontend switch is set to sample  $V_{RES}$  on the track and hold circuit. This process from the previous cycle is repeated for a total of n cycles. Using this method, the converter generates n number of m-bit digital codes to create a single N-bit output code [12, 5]. In more recent systems, there is at least a 1-bit overlap in the m-bit codes between cycles for redundancy. To achieve this overlap, the amplifier stage has a gain of less than  $2^m$  (typically  $\approx 1.8^m$ ) [17]. The result is a N-bit converter output code that is less than  $n \times m$ .

The primary advantage of the cyclic ADC over a straight flash converter is that it uses less comparators and achieves a higher resolution. For an N-bit cyclic ADC, the number of comparators required is only  $2^m - 1$ . This requires less die area and power than an equivalent N-bit flash converter. In addition, a full resolution of more than 8-bits can be achieved by increasing the number of cycles used for each conversion. The main drawback for this architecture is the converter speed. Since a single conversion requires multiple cycles, the sample period is dependent on the signal propagation times the number of cycles performed. This makes the cyclic ADC well suited to moderate speed, moderate resolution applications that require a small die area and low power [5, 17].

#### 2.2.3 Pipelined Architecture

The advantages of the cyclic ADC are improved upon by the pipelined architecture. A pipelined A/D breaks up a single conversion into multiple stages, similar to the way a pipelined microprocessor breaks up a single instruction execution. In this setup, the feedback loop from the cyclic ADC is removed and multiple copies or stages are used in a daisy chain array as shown in Figure 2.9 [2].

For example, the first stage samples the input signal with a track and hold circuit without the frontend selection switch. The path is the same as a cyclic ADC up until output of the residue amplifier. Instead of sending the  $V_{RES}$  voltage back to the beginning of the system, the voltage is sent to another stage that looks similar to the first stage. The frontend track and hold amplifier at the beginning of the first stage is now free to capture the next analog input sample while the second stage THA can sample the residue voltage

Figure 2.9: Block Diagram of a Pipelined ADC

from the first stage. The delay time from input to output for a N stage pipeline converter is about the same as a N cycle ADC. The sampling rate is only limited by the slowest stage in the pipeline converter as opposed to the sum of all stages. The pipeline converter is capable of moderate to high speed sample rates and moderate resolutions [7]. This architecture is common in such applications as Charge Coupled Device (CCD) imaging and ultrasonic medical imaging [2].

#### 2.2.4 SAR Architecture

Unlike the previous architectures the Successive Approximation Register (SAR) ADC does not use a flash sub-converter. The SAR instead uses a full resolution DAC and one comparator to perform a binary search algorithm [5, 6]. The SAR iterates through each bit of the DAC to find an analog voltage that is approximately equal to the sampled input voltage. Most SARs use a binary weighted charge balancing architecture for the D/A since capacitors are easier to match than resistors and offer better noise performance. A comparator is used to determine if the DAC voltage is greater or less than the original input voltage. The decision of the comparator is used to determine the next bit in the DAC code. Once the SAR has reached the last bit, the complete digital word is used as the ADC's output.

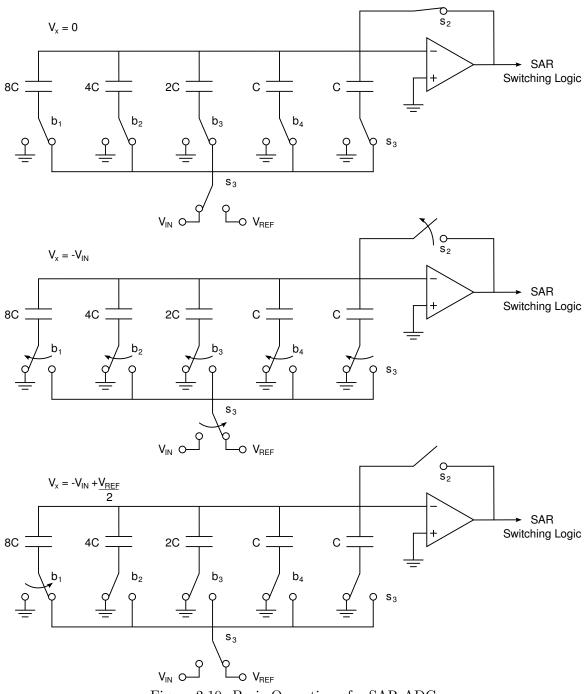

Figure 2.10 shows the first couple of steps in the successive approximation process for a unipolar, charge balancing SAR converter [5]. For the first step, the analog input voltage is sampled onto all of the capacitors in the switch-cap network while the comparator is reset to its threshold voltage (ground in this case). During the hold mode, the comparator output

is released and all capacitors are switched to ground. This forces the DAC output voltage  $(V_x)$  to go to negative  $V_{IN}$ . At the same time,  $s_1$  is switched to  $V_{REF}$ . The next step is the start of the bit-cycling mode, which is where the binary search takes place. In the scenario shown in Figure 2.10 the comparator output during the hold mode was a logic '1' decision. Using this information, the first capacitor which represents the MSB is switched to  $V_{REF}$ . This changes the DAC voltage to  $-V_{IN} + \frac{V_{REF}}{2}$  resulting in a new comparator decision for the next DAC bit. This process is repeated until all DAC bits have been set and sent as the A/D digital output code [7, 6, 5].

Iterating through the sample, hold, and bit cycling modes requires a longer sample period than flash, cyclic, and pipeline ADCs [6]. This makes the SAR converter a moderate speed ADC, but it is capable of higher resolutions than the flash based architectures. In the cyclic and pipeline converter, a residue voltage must be amplified by a fixed gain amplifier before being sent to the next cycle or stage. This amplifier circuit will add noise to the residue voltage with a cumulative effect for each cycle or stage. This places a practical limit on the number of cycles or stages used, thereby restricting the full A/D resolution to moderate levels. The noise in a charge balancing, successive approximation converter is limited by the capacitor DAC network and the preamp for the comparator. Charge balancing SAR converters are more power efficient that flash or pipeline converters due to the low number of active components and the elimination of a resistor ladder [7, 6]. This makes the SAR converter well suited for both low power and higher resolution applications such as portable instrumentation and data acquisition [2, 7].

#### 2.2.5 Time Interleaved Architecture

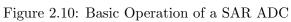

The time interleaved architecture is a system that uses multiple full resolution ADCs running on a subdivided master sample clock [2, 3]. For a given M:1 time interleaved A/D, there are M converters which operate at sample rate of  $\frac{f_S}{M}$ . Figure 2.11 shows the operation of a 2:1 interleaved converter. Two separate ADCs operate at an individual sample rate of  $\frac{f_S}{2}$ . One converter processes the odd samples of the input while the other converter processes the even samples. This allows for the system sample rate,  $f_S$ , to be twice the maximum sample rate of the two sub-converters [3].

The 2:1 example can be extended to any M:1 interleaved system that can operate at M times the sample rate of its M interleaved converters. The primary advantage of a time interleaved system is the increase in speed without sacrificing resolution. This makes them well suited for applications that require high speed and high resolution converters such as instrumentation and measurement. Unfortunately, linear errors that were trivial in a single converter system present a new set of problems in the interleaved architecture.

As discussed earlier gain and offset errors can be easily calibrated out for a single converter [2, 3]. In an interleaved system, the individual converters have each have their own unique gain and offset errors. The mismatch in these errors between each converter channel can no longer be modeled as y = Ax+b. The third linear mismatch error is the deterministic component of aperture delay. As previously mentioned, a fixed delay in the sample time of a single converter does not affect the output code. However, in the interleaved architecture, mismatch in signal path lengths leads to differences in the aperture delay between each sub-converter channel [4, 3]. Since the delay is no longer fixed for each sample time, this results in a varying sample period. The effects of gain, offset, and aperture delay channel mismatch will be discussed further in Chapter 3.

### Chapter 3

## Interleaved and SAR Architectures

The two ADC architectures that are the focus of this research are the time interleaved and successive approximation register converters. Both architectures can provide high resolution samples with moderate to high speed conversions. However, as previously discussed, each type has unique non-idealities which can limit the accuracy of the ADC. Section 3.1 describes the interleaved ADC and the effects of gain, offset and aperture delay on the output signal. Section 3.2 describes the charge balancing, SAR converter and the effects of capacitor mismatch.

#### 3.1 The Time Interleaved Converter

As discussed earlier, the time interleaved converter is an effective architecture for achieving high speed conversions using M full resolution subconverters. Each Nyquist-rate subconverter operates at a rate of  $f_S/M$ , allowing the full system to run M times faster than the maximum sample rate of a single subconverter. However, differences between each subconverter channel leads to errors in a TI system. As device technology scales deeper into the nanoscale region, physically matching subconverter channels becomes a critical issue. Because of this, the error sources in a TI structure have been studied to determine their cause and how to minimize their effects.

The three main error contributions due to channel mismatch are offset, gain and aperture or timing delay. The effects of all three errors on the digital output code for a single channel

Figure 3.1: Effects of time interleaved channel mismatch on an input signal

can be modeled as (3.1).

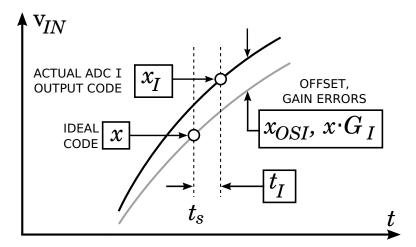

$$x_I = x + x_{OSI} + xG_I + \dot{x}t_I \tag{3.1}$$

The three error coefficients for channel 1 are  $x_{OSI}$  as the offset error,  $G_I$  as the gain error, and  $t_I$  for the aperture delay. The ideal output code is represented by x, while  $\dot{x}$  represents the derivative and  $x_I$  represents the non-ideal output code from channel 1. Using Equation (3.1), one can see how the effects of gain mismatch are proportional to the magnitude of the input signal and the effects of aperture delay are proportional to the derivative.

Figure 3.1 shows a graphical example of (3.1). The solid black curve represents the signal with only offset and gain distortion. The delay in sampling time can be seen as difference in  $V_{IN}$  that is dependent on the derivative of the input signal as described by (3.1).

To understand the effects of this channel mismatch, the time interleaved converter should be analyzed in the frequency domain. The work presented in [4] quantifies the relationship between the effects of the channel mismatch and the error spurs in a FFT.

#### 3.1.1 Offset Mismatch Error

The magnitude of the offset mismatch spurs can be found in (3.2). The location of the spurs in the frequency domain is dependent on the frequency components of the input signal and the interleaving ratio of the TI converter. For a 4:1 system, the offset spurs would occur

Figure 3.2: Block Diagram of 4:1 Time Interleaved Converter with Offset Error Introduced

at  $f_S/4$  and  $f_S/2$ .

Offset Spur =

$$20 \log \left(\frac{\Delta OS}{V_{FS}}\right)$$

(3.2)

Equation (3.2) shows how the spurs are proportional to the offset mismatch,  $\Delta OS$  (in volts), with relation to the full scale voltage,  $V_{FS}$ .

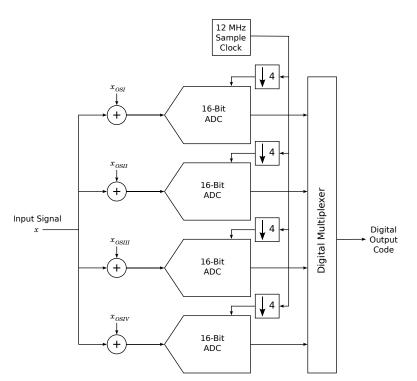

A simulation of a 4:1 TI system with only offset channel mismatch provides a clear example of its effect on the output spectrum. For this setup, all gain and aperture delay errors are set to zero and the offset mismatch is limited to  $\pm 0.1\%$ . While the mean or system offset is 215  $\mu$ V, it has no effect on the image spurs. A block diagram of the configuration is shown in Figure 3.2. A 317 kHz, full scale input sinewave is fed to four A/D converters. A unique offset voltage is added to the signal before the input stage of each ADC. All four converters have a 16-bit resolution and operate at 3 MHz each to produce a master sampling frequency of 12 MHz.

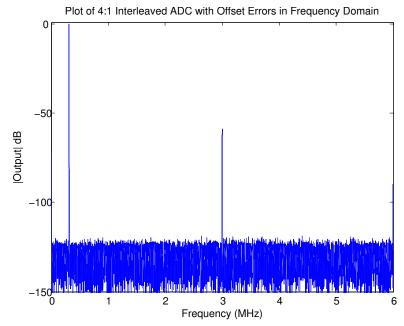

The simulation results are presented in Figure 3.3. The spectrum plot is normalized to

Figure 3.3: 4:1 Time Interleaved Output Spectrum with Offset Errors

the 317 kHz input sinewave at 0 dB. The plot shows two errors spurs at 3 MHz and 6 MHz. The Spurious Free Dynamic Range is the ratio of the input signal to the largest distortion or error spur. In this simulation the SFDR is 58.81 dB from the input signal at 317 kHz to the offset error spur at 3 MHz.

#### 3.1.2 Gain Mismatch Error

The effects of gain mismatch error on the output spectrum of a TI system is described by (3.3). In a 4:1 time interleaved converter, the image spurs due to gain mismatch error would occur at  $f_S/2 - f_{in}$  and  $f_S/4 \pm f_{in}$  [4]. The gain mismatch error is the full scale voltage ratio between two channels as defined by (3.4).

Gain Spur =

$$20 \log \left( \frac{G_{err}}{2 \cdot V_{FS}} \right)$$

(3.3)

$$G_{err} = \left| 1 - \frac{V_{FSA}}{V_{FSB}} \right| \tag{3.4}$$

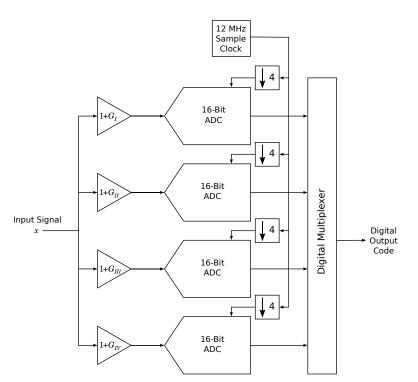

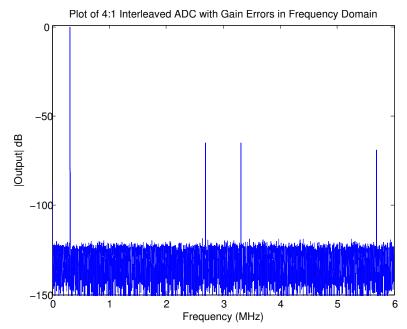

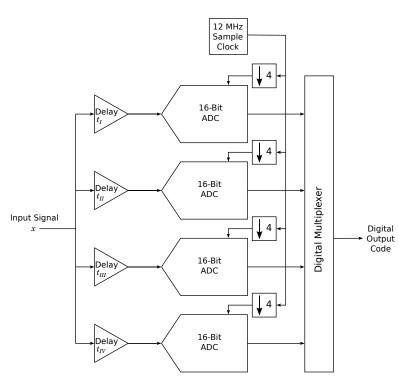

This simulation of a time interleaved system with a 4:1 ratio used a gain mismatch error

Figure 3.4: Block Diagram of 4:1 Time Interleaved Converter with Gain Error Introduced

of  $\pm 0.2\%$  and all other errors set to zero. The sampling rate used was 12 MHz with an input signal of 317 kHz. The sinewave is fed to four gain stages where each stage has a unique gain of  $1 \pm 0.002$ . The gain stage outputs are then fed to their respective 16-bit converters.

The simulation results showed a system gain error of -617 mV. The image spurs can be seen in Figure 3.5 at 2683 kHz, 3317 kHz and 5683 kHz. The largest spurs are the two at 2683 kHz and 3317 kHz which gives a SFDR of 65.15 dB.

### 3.1.3 Aperture Delay Mismatch Error

The effect of aperture delay mismatch error on the output spectrum can be represented by (3.5). A 4:1 TI system has image spurs in the same locations as those due to gain mismatch error. When both gain and aperture delay mismatch errors are present, the Root Mean Square value is shown by (3.6) [4]. The magnitude of the image spurs due to aperture delay mismatch are dependent on both the time delay and input frequency.

Figure 3.5: 4:1 Time Interleaved Output Spectrum with Gain Errors

Aperture Delay Spur =

$$20 \log \left(\frac{2\pi f_{in} \Delta t_{apd}}{2}\right)$$

(3.5)

Gain & Aperture Delay Spurs =

$$20 \log \left( \sqrt{\left(\frac{G_{err}}{2}\right)^2 + \left(\frac{2\pi f_{in}\Delta t_{apd}}{2}\right)^2} \right)$$

(3.6)

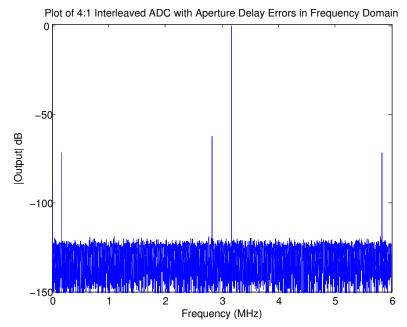

A simulation of a 4:1 TI converter was used to show the effect of aperture delay. The setup for this simulation was similar to the one used for gain mismatch. A single input signal was fed to four individual delay stages. Each stage had a delay between 0 and 50 ps with a mean aperture delay error of 23 ps. The delayed signals were then sent to their respective, 16-bit converters. As before, the sampling rate was 12 MHz, but this time the input frequency was set to 3175 MHz. As previously mentioned, the effects of aperture delay are proportional to the frequency of the input signal, as seen in (3.5). Therefore, an input with a higher frequency was used to show the effect of aperture delay for signals close to Nyquist.

Figure 3.6: Block Diagram of 4:1 Time Interleaved Converter with Aperture Delay Error Introduced

Figure 3.7 shows the output spectrum of the simulated TI converter with spurs at 175 kHz, 2825 kHz and 5825 kHz. The largest spur at 2825 kHz produces a SFDR of approximately 62.29 dB.

The total power of all image spurs due to offset, gain, and aperture delay can be found using the Root Sum Square (RSS) as shown in (3.7).

Total Spurs =

$$20 \log \left( \sqrt{\sum_{i=1}^{M} \left( \frac{\Delta OSi}{V_{FS}} \right)^2 + \sum_{i=1}^{M} \left( \frac{G_{erri}}{2} \right)^2 + \sum_{i=1}^{M} \left( \frac{2\pi f_{in} \Delta t_{apdi}}{2} \right)^2} \right)$$

(3.7)

For a given M:1 interleaved converter, the square of each mismatch error for each,  $i^{th}$  channel is summed before taking the square root. The total power is used to determine how much calibration is necessary to reduce the errors enough for an N-bit converter. For example, using the SNDR from (2.4), a 16-bit converter can have a maximum SNDR of 98 dB. Therefore, the total power of all spurs due to mismatch error after calibration must be less than -98 dB.

Figure 3.7: 4:1 Time Interleaved Output Spectrum with Aperture Delay Errors

## 3.1.4 Bandwidth Mismatch Error

Channel bandwidth mismatch is a type of nonlinear error in TI converters. An in-depth analysis of effects due to this error is presented in [18]. The T/H circuit in each channel can be approximated as a first-order system in the frequency domain as

$$H_k(j2\pi f) = 1/(1 + jf/f_{c(i)}) \tag{3.8}$$

where  $f_{c(i)}$  is the mismatch of the bandwidth in each channel  $(i = 1, 2, \dots, M)$ . The output signal has two error components due to bandwidth mismatch, AC gain mismatch  $G_i$  and AC phase mismatch  $\theta_i$  [18].

$$G_i = \frac{1}{\sqrt{1 + (f_{in}/f_{c(i)})}}$$

(3.9)

$$\theta_i = -\arctan(f_{in}/f_{c(i)}) \tag{3.10}$$

It is important to note that AC gain and phase depend on bandwidth mismatch and the input frequency  $f_{in}$ , unlike the linear gain and aperture delay mismatch. [18] presents a

detailed analysis of bandwidth mismatch in a 4:1 time interleaved system. It shows that the SNR in a 4:1 is

SNR (dB) =

$$20 \log \frac{B_{s4}^2}{B_{n1}^2 + B_{n2}^2 + B_{n3}^2}$$

(3.11)

where

$$B_{s4} = \sqrt{B_{sc}^2 + B_{ss}^2} \quad B_{n1} = \sqrt{B_{n1c}^2 + B_{n2s}^2} \quad B_{n2} = \sqrt{B_{n2c}^2 + B_{n2s}^2} \quad B_{n3} = \sqrt{B_{n3c}^2 + B_{n3s}^2}$$

and the the values  $B_{sc}$ ,  $B_{ss}$ ,  $B_{n1c}$ ,  $B_{n1s}$ ,  $B_{n2c}$ ,  $B_{n2s}$ ,  $B_{n3c}$  and  $B_{n3s}$  are defined below [18].

$$B_{sc} = \frac{1}{4} \Big( + (G_1 + G_3)\cos(\theta)\cos(\theta_{13}) + (G_2 + G_4)\cos(\theta)\cos(\theta_{24}) \\ - (G_1 - G_3)\sin(\theta)\sin(\theta_{13}) + (G_2 - G_4)\sin(\theta)\sin(\theta_{24}) \Big)$$

(3.12)

$$B_{ss} = \frac{1}{4} \Big( - (G_1 + G_3)\sin(\theta)\cos(\theta_{13}) + (G_2 + G_4)\sin(\theta)\cos(\theta_{24}) \\ - (G_1 - G_3)\cos(\theta)\sin(\theta_{13}) - (G_2 - G_4)\cos(\theta)\sin(\theta_{24}) \Big)$$

(3.13)

$$B_{n1c} = \frac{1}{4} \Big( -(G_1 + G_3)\sin(\theta)\sin(\theta_{13}) + (G_2 + G_4)\cos(\theta)\sin(\theta_{24}) \\ + (G_1 - G_3)\cos(\theta)\cos(\theta_{13}) - (G_2 - G_4)\sin(\theta)\cos(\theta_{24}) \Big)$$

(3.14)

$$B_{n1s} = \frac{1}{4} \Big( -(G_1 + G_3)\cos(\theta)\sin(\theta_{13}) + (G_2 + G_4)\sin(\theta)\sin(\theta_{24}) \\ -(G_1 - G_3)\sin(\theta)\cos(\theta_{13}) + (G_2 - G_4)\cos(\theta)\cos(\theta_{24}) \Big)$$

(3.15)

$$B_{n2c} = \frac{1}{4} \Big( + (G_1 + G_3)\cos(\theta)\cos(\theta_{13}) - (G_2 + G_4)\cos(\theta)\cos(\theta_{24}) \\ - (G_1 - G_3)\sin(\theta)\sin(\theta_{13}) - (G_2 - G_4)\sin(\theta)\sin(\theta_{24}) \Big)$$

(3.16)

$$B_{n2s} = \frac{1}{4} \Big( - (G_1 + G_3)\sin(\theta)\cos(\theta_{13}) - (G_2 + G_4)\sin(\theta)\cos(\theta_{24}) \Big)$$

$$-(G_1 - G_3)\cos(\theta)\sin(\theta_{13}) + (G_2 - G_4)\cos(\theta)\sin(\theta_{24})\Big)$$

(3.17)

$$B_{n3c} = \frac{1}{4} \Big( -(G_1 + G_3)\sin(\theta)\sin(\theta_{13}) - (G_2 + G_4)\cos(\theta)\sin(\theta_{24}) + (G_1 - G_3)\cos(\theta)\cos(\theta_{13}) + (G_2 - G_4)\sin(\theta)\cos(\theta_{24}) \Big)$$

(3.18)

$$B_{n3s} = \frac{1}{4} \Big( -(G_1 + G_3)\cos(\theta)\sin(\theta_{13}) - (G_2 + G_4)\sin(\theta)\sin(\theta_{24}) - (G_1 - G_3)\sin(\theta)\cos(\theta_{13}) - (G_2 - G_4)\cos(\theta)\cos(\theta_{24}) \Big)$$

(3.19)

The values  $G_1$  through  $G_4$  and  $\theta_1$  and  $\theta_4$  are defined in 3.9 and 3.10 respectively. The values  $\theta$ ,  $\theta_{13}$  and  $\theta_{24}$  in (3.12) through (3.19) are defined as

$$\theta = \frac{1}{4} (\theta_1 - \theta_2 + \theta_3 - \theta_4) \quad \theta_{13} = \frac{1}{2} (\theta_1 - \theta_3) \quad \theta_{24} = \frac{1}{2} (\theta_2 - \theta_4).$$

(3.20)

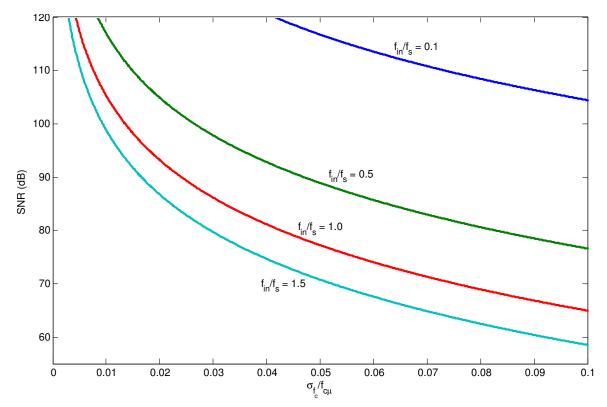

To determine how much bandwidth mismatch is acceptable for an N-bit converter, (2.4) must be used with (3.11). Again, for a 16-bit converter the SNDR must be better than 98 dB, however, the SNDR due to bandwidth mismatch is dependent on the bandwidth of each channel and the input frequency  $f_{in}$ . Therefore, a numerical analysis of bandwidth mismatch can show SNDR performance over a range of input frequencies. Figure 3.8 shows SNDR performance versus channel bandwidth mismatch for multiple input frequencies. To perform this analysis a set of restrictions were placed on the variables  $f_{c1}$ ,  $f_{c2}$ ,  $f_{c3}$  and  $f_{c4}$ . The channel bandwidths were uniformly distributed with a mean bandwidth  $f_{c\mu}$ , of 50 MHz and a standard deviation  $\sigma_{f_c}$ , determined by

$$\sigma_{f_c} = \sqrt{\frac{(f_{c1} - f_{c\mu})^2 + (f_{c2} - f_{c\mu})^2 + (f_{c3} - f_{c\mu})^2 + (f_{c4} - f_{c\mu})^2}{4}}.$$

(3.21)

The master sampling frequency was 12 MHz and four input frequencies were tested, 1.2 MHz, 6 MHz, 12 MHz, and 18 MHz. According to the plot in Figure 3.8, a 16-bit TI ADC with an average bandwidth of 50 MHz and an input frequency near Nyquist  $f_S/2$ , can tolerate a maximum bandwidth mismatch of  $\pm 3\%$ .

Figure 3.8: Plot of Bandwidth Mismatch for Multiple Input Frequencies

## 3.2 The SAR Converter

Successive approximation ADCs provide high resolution samples at moderate conversion speeds with moderate circuit complexity [5]. The SAR converter requires only one precision analog comparator, a DAC network with a sample and hold circuit, as well as supporting digital logic for the binary search algorithm.

One of the more common designs for a successive approximation ADCs uses a differential, charge balancing DAC network. The benefits of using capacitors in the DAC circuit is two fold. In an IC layout, capacitors are better than resistors at both device matching as well as noise performance [12, 5]. The use of a switched-capacitor DAC also eliminates the need for a separate sample and hold circuit. A fully differential, charge balancing SAR is presented as an example, in the following section. Section 3.2.2 describes the non-idealites and errors that are found in this type of A/D.

#### 3.2.1 Operation of a Differential SAR

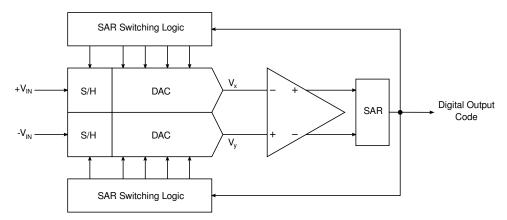

The basic operation of a differential SAR is similar to the operation of the single-ended converter described in Section 2.2.4. Two switched-cap DAC networks are used, one positive and one negative. Figure 3.9 shows a block diagram of the differential converter with the two DAC circuits. Instead of comparing a single DAC voltage to a fixed common-mode DC voltage, the positive DAC voltage is compared to the negative side. This allows for the sampling of a differential input while making use of a high Common Mode Rejection Ratio (CMRR). The differential output of the comparator is fed into digital logic that makes the appropriate capacitor selection in the DACs. With each bit decision, the differential voltage is driven to zero, balancing the charge between the positive and negative DACs.

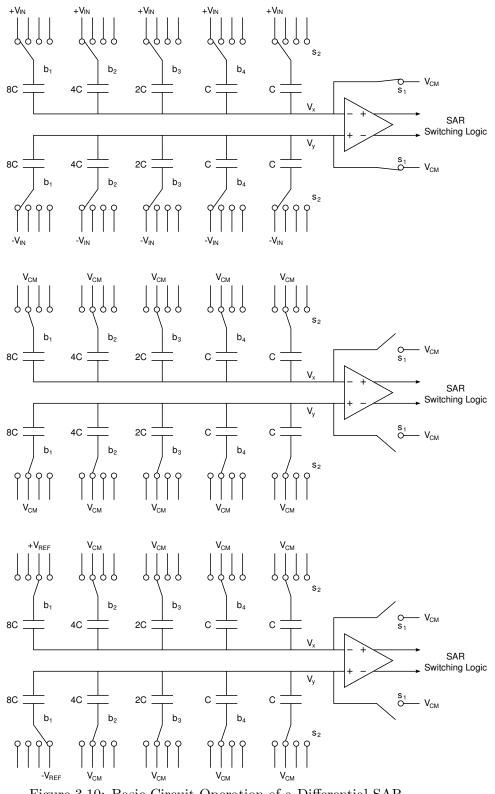

Figure 3.10 shows the first three steps of the differential SAR converter. There are a few differences between the single-ended and differential circuits. During the sample phase, the capacitors are switched to their respective input voltages. In this case, the comparator is fully differential and there is no closed-loop feedback for the sample mode. Instead, the two DAC voltages are shorted to a common mode voltage. For the hold phase, the capacitor network is switched to the common mode while the differential DAC voltage is allowed to

Figure 3.9: Block Diagram of a Differential SAR

| Cycle  | V <sub>x</sub> (V) | V <sub>y</sub> (V) | Bit Decision |

|--------|--------------------|--------------------|--------------|

| Sample | 0.900              | 0.900              | N/A          |

| Hold   | 1.375              | 0.425              | +1           |

| Bit 1  | 0.925              | 0.875              | +1           |

| Bit 2  | 0.700              | 1.100              | -1           |

| Bit 3  | 0.8125             | 0.9875             | -1           |

| Bit 4  | 0.8688             | 0.9313             | N/A          |

Table 3.1: Table of DAC Voltages for a Single Conversion

settle to the sampled differential input voltage. For the bit cycling mode, the comparator decision is used to switch the capacitors used for that bit in each DAC.

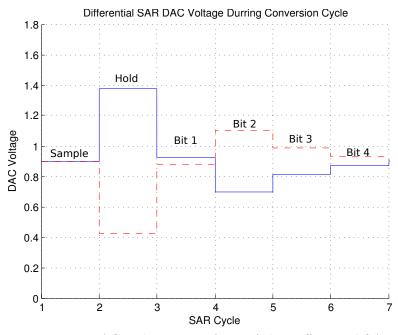

To better illustrate the operation for a full conversion, Figure 3.11 shows the voltage waveforms from both DACs for a 4-bit SAR converter. The voltage reference used for this example was 1.8 V with a 0.9 V common mode and a differential input voltage of +0.95 V. The two DAC voltages,  $V_P$  and  $V_N$  are brought to 0.9 V for the sample mode, while the input side of the capacitors are shorted to the differential input voltage. For the hold mode,  $V_P$  is allowed to settle to 1.375 V while  $V_N$  is allowed to settle 0.425 V. At this point, the magnitude of the differential DAC voltage is equal to the magnitude of the sampled input voltage. The comparator then makes a +1 decision, switching bit one in the negative DAC to 0 V and the positive DAC to 1.8 V. This forces the differential DAC voltage to settle to a new value, 0.05 V. Once the DACs have enough time to settle, the comparator makes a new decision of +1, bringing  $V_P$  to 0.7 V and  $V_N$  to 1.1 V. Table 3.1 describes the remaining bit decisions and DAC voltages for the entire conversion cycle.

Figure 3.11: DAC Voltage Waveform of the Differential SAR

In the ideal case, the DAC voltages quickly settle to the correct values and the comparator always makes the right decision. In addition, the capacitor weights would always be perfectly matched to powers of 2. Unfortunately, this is never the case in the real world, and non-idealities with the comparator, DAC settling time, and capacitor mismatch results in output errors.

### 3.2.2 Non-Idealities in a SAR Converter

The two main types of errors in a SAR A/D are incorrect comparator decisions and nonlinearity. The sources for these errors can range from capacitor mismatch, voltage reference noise and distortion, to insufficient DAC settling time. These types of errors are difficult to account for outside of the SAR, so extra circuitry is usually added to correct for these errors internally.

#### 3.2.3 Incorrect Comparator Decisions

Noise or distortion on the reference voltage side of the DAC network can result in an incorrect decision. The charge balancing network is a capacitively loaded circuit that

Figure 3.12: DAC Voltage Waveform of the SAR with Redundant Bit and Recovery

changes voltage in sharp steps. When the differential DAC voltage changes after a bit decision, there is a finite amount of time required to allow for the voltage to settle from ringing. If the differential voltage does not settle in time, the comparator might make the wrong the decision and tell the DAC to switch in the wrong direction. Once this occurs, it is no longer possible to drive the differential DAC voltage to within one half LSB. This will also result in a digital output code that does not match with the sampled input voltage. A bad decision at the beginning of the conversion with one of the first couple of bits would result in a larger error than a bad decision with one of the last few bits.

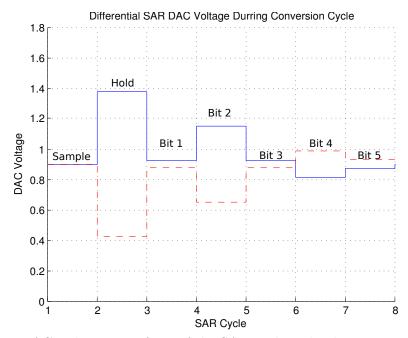

In order to correct for this kind of error, the DAC network must be expanded to allow for the ability to recover from a wrong decision. The classic method of doing this is to add redundant bits to the charge balancing circuit. Using the four bit SAR example, a fifth bit decision can be added in between bits two and three. This redundant bit would have the same weight as the second bit and allow for a recover if a mistake is made with either the first or second bit decision. Figure 3.12 and Table 3.2 shows how the ADC can recovery from an early, incorrect bit decision.

In this simulation, the differential voltage input is still +0.95 V, but the comparator

| Cycle  | $V_x$ (V) | $V_y$ (V) | Bit Decision |

|--------|-----------|-----------|--------------|

| Sample | 0.900     | 0.900     | N/A          |

| Hold   | 1.375     | 0.425     | +1           |

| Bit 1  | 1.120     | 0.875     | -1           |

| Bit 2  | 1.150     | 0.650     | +1           |

| Bit 3  | 0.925     | 0.875     | +1           |

| Bit 4  | 0.8125    | 0.9875    | -1           |

| Bit 5  | 0.8688    | 0.9313    | N/A          |

Table 3.2: Table of DAC Voltages for a SAR Conversion with Decision Recovery

makes a wrong decision with the second bit. Without the redundant bit, the final digital output would be 1011 which results in an equivalent analog voltage of 0.787 V. Using the redundant bit with a weight equal to the second bit, the new output code is 10110 with an equivalent analog voltage of 1.0125 V. As one can see, the fifth bit does not add to the resolution of the A/D, but it does help correct for a decision error in the first two bits. For higher resolution converters, the number of redundant bits can be increased to correct for multiple bad decisions.

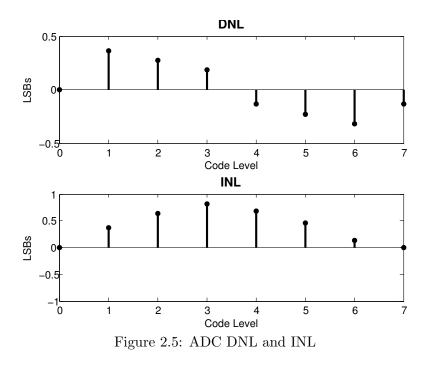

#### 3.2.4 Capacitor Weight Mismatch

In a SAR converter, the second type of error, nonlinearity, is due to the capacitor size mismatch in the DAC network. An ideal SAR DAC has a binary weighted capacitor network where each successive capacitor is exactly one half the size of the previous capacitor. When the weights are not exact binary multiples of each other, the transfer characteristic of the converter is nonlinear. This effect is most obvious with transition at the Most Significant Bit. The weight of the MSB should be one LSB greater than the sum of the weights for the remaining bits. However, the mismatch between the MSB and the remaining bits is usually the largest.

In the example shown in Figure 3.13, a discontinuity can be seen when the code changes from 0111 to 1000. Table 3.3 shows both the ideal and non-ideal weights for a 4-bit A/D. Using this table the combined weights of the last three bits is 0.7782 V while the weight of the MSB is 0.9135 V resulting in a weight mismatch of 0.1353 V.

The nonlinearity due to capacitor size mismatch can be easily measured and character-

| Ideal Weights | Non-Ideal Weights |

|---------------|-------------------|

| 0.9000 V      | 0.9135 V          |

| 0.4500 V      | 0.4478 V          |

| 0.2250 V      | 0.2212 V          |

| 0.1125 V      | 0.1092 V          |

Table 3.3: Table of Ideal and Non-Ideal DAC Weights

Figure 3.13: INL of Non-Ideal SAR Converter

ized externally. There are several methods used to measure DNL and INL for an A/D. The most straight forward method requires a computer controlled, precision voltage generator and a Digital Acquisition unit. The computer steps through all  $2^N$  quantization levels, while DAQ captures the output code for each sample. This allows for a direct measurement of the nonlinearity errors. However, it is difficult to precisely iterate through all quantization levels of a high resolution ADC. More often, a statistical method is used by feeding a sinusoidal input to the A/D and plotting a histogram of the output as discussed in Section 2.1.2. After several million samples, the output histogram is compared to the ideal histogram of the sinewave input. Deviations from the ideal histogram curve translate to DNL and the INL can be calculated from the DNL. [14]

Measuring and quantifying the nonlinearity error due to capacitor mismatch can pro-

vide information to be used in correcting the output. Typically these measurements are fed back to a calibration circuit within the SAR converter. This eliminates the need for external circuitry to compensate for non-ideal weights. There are several calibration and correction techniques used with both TI and SAR converters, each with their own benefits and drawbacks. These methods and the method used for this research are discussed in more detail in the following chapter.

## Chapter 4

# **ADC** Calibration

As integrated circuit technology scales down to deep sub-micron sizes, device mismatching and increased variability introduce more challenges to analog circuit design. These difficulties have a large impact on the accuracy and distortion of all analog to digital converters. Therefore, much effort has gone into calibrating and correcting the outputs of A/Ds using combinations of analog and digital techniques.

## 4.1 Time Interleaved ADC Calibration

There are several techniques for reducing errors found in TI converters. One method can reduce the errors within the desired frequency range and increases the signal-to-noiseand-distortion ratio (SNDR). An example of this is the use of digital filters at the output of the converter to shift or shape the spectrum of the overall signal [19, 20, 21]. Another method involves calibrating the ADC to remove or reduce the cause of the errors and thus remove their effects. There are various forms of converter calibration, each with their own advantages and disadvantages. The main goal for this research is to perform converter calibrations as quickly and as accurately as possible. Therefore, it is necessary to ensure that a deterministic and digital background calibration technique is used.

In the past, analog circuit techniques have been used for calibration, but suffered the penalty of adding complex circuitry. In the analog domain, an increase in circuit complexity results in a larger penalty of die area, power, and noise [22, 9]. Common analog techniques include variable signal delay stages or a reference ramp signal generator [23, 24]. These components can be very sensitive to noise and interference, producing invalid error estimates.

The work in [24] uses digital techniques to generate timing delay estimates which are discussed later. While the calibration estimates are done in the digital domain, this converter implements adjustable delay lines for each channel in the analog domain to correct for aperture delay mismatch. Another analog technique for correcting aperture delay mismatch is a distributed Sample and Hold network [25, 26]. A front-end S/H circuit operates at the full speed of the interleaved converter,  $f_S$ , to capture every sample. In order to reduce loading of the master S/H circuit, each channel has its own S/H circuit placed before the sub-ADC. By reducing the load on the front-end S/H circuit, the converter can run at a higher speed without any delay mismatch [25]. The additional S/H networks introduce extra analog complexity and the top speed of the master S/H is still limited by the process technology. An analog technique for offset error is shown in [21]. This work introduces a TI structure that adds a PRN chopping circuit to the analog front-end of each channel for offset estimation (correction is done in the digital domain).

[27] describes a 2:1 interleaved pipeline converter. This novel technique uses a single first stage that runs at the full sampling rate,  $f_S$ , but uses two interleaved subsequent stages that each operate at  $f_S/2$ . The ADC uses two tack and hold circuits that run at the full speed sampling rate,  $f_S$ . One T/H drives the first stage 2.8-bit flash A/D. The output of the first A/D is fed to two MDACs that use the second T/H to generate the two, interleaved residue paths. While the two T/H allow for a higher throughput rate, it adds analog complexity and the need to design for time delay mismatch. The ADC performs gain and offset error calibration in the digital domain. However, the offset error corrections that are calculated are then fed into offset cancellation circuits inside each pipeline stage. This introduces another layer of analog complexity to the calibration and correction hardware.

One of the advantages of technology scaling is the ability to use redundancy as a method for calibrating interleaved converters [26, 24]. The highly interleaved converter in [26] achieved a 36:1 ratio by implementing 42 ADCs on the chip. Instead of directly calibrating out all of the mismatch errors for each sub-ADC, the 6 worst performing channels were eliminated in order to improve the system level performance. While this method does not use any additional power as those six sub-ADCs are turned off, it does require additional space for both analog and digital circuitry. This method also has the disadvantage of requiring foreground calibration to determine which six channels must be turned off.

Another redundant method which is similar to this author's work described in Chapter 5 compares the different ADC channels with each other [24]. In [24] two redundant ADC channels are added to a 16:1 interleaved converter. One of the channels is chosen as the reference channel. For some conversions, this reference channel is run simultaneously with another channel. A calibration loop observes the long-term RMS and mean values and attempts to make them identical for each channel pairing by making gain and offset adjustments in the digital domain [24]. While this calibration is similar to the one used in Chapter 5, there are two main differences. As mentioned earlier, [24] uses variable delay lines to correct for timing delay in the analog domain. In addition, the use of two redundant, full sized A/Ds adds both die area and power to the circuit design.

Digital calibration takes advantage of the scalability and improved performance of digital circuits [28, 9]. These circuits are more robust and less sensitive to noise from the system, which allows for accurate estimation and correction. Unfortunately, previous digital calibration techniques have not been both background and deterministic. Statistical calibration techniques usually require known inputs and long calibration times [29, 30, 31].